Table of Contents

EE6361: Advanced Topics in VLSI

Announcement: End Sem details

Date: 3 May 2017 (Wednesday)

Time: 2:00 - 5:00 PM

Location: ESB 207B

Syllabus: eDRAM, SRAM, EDA

Announcement: Second quiz details

Date: 5 Apr 2017 (Wednesday)

Time: 5:00 - 6:00 PM

Location: ESB 207B

Syllabus: SRAM

Announcement: First quiz details

Date: 27 Feb 2017 (Monday)

Time: 5:00 - 6:00 PM

Location: ESB 207B

Syllabus: eDRAM

Instructors

- Janakiraman Viraraghavan (IITM)

- Dr. Rahul Rao (STSM IBM. India. Pvt. Ltd)

- Dr. Sridhar Rangarajan (STSM IBM India Pvt. Ltd)

Classroom

ESB 207B

Schedule

S-slot - Thu (1:30 - 4:30 PM)

Evaluation

- Assignments: 20%

- Quiz 1: 10% (eDRAM)

- Quiz 2: 10% (SRAM)

- Self Study Seminar : 20%

- End Semester Exam: 40%

Course Objective

(Why we teach this course?)

- Introduce students to some relevant advanced topics of current interest in academia and industry

- Make students aware of some advanced techniques

- Make students aware of work happening in India

This course will cover three broad subjects:

- Embedded DRAM design and statistical yield analysis (Janakiraman)

- SRAM design (Rahul Rao)

- EDA (Sridhar Rangarajan)

Learning Objectives

(What the students should be able to do after the course)

Part 1- eDRAM Design and Yield Analysis

- Explain the working of a (e)DRAM. What Embedded means?

- Explain the working of a feedback sense amplifier and modify existing designs to improve performance

- Calculate the voltage levels of operation of various components for an eDRAM

- Introduce stacked protect devices to reduce voltage stress of the WL driver

- Calculate the number of samples required to estimate yield to specified accuracy and confidence

- Explain the use of importance sampling to reduce the number of samples required in step 6

Part 2- SRAM Design

- Articulate memory hierarchy and the value proposition of SRAMs in the memory chain + utilization in current processors

- Explain SRAM building blocks and peripheral operations and memory architecture (with physical arrangement)

- Articulate commonly used SRAM cells (6T vs 8T), their advantages and disadvantages

- Explain the operation of a non-conventional SRAM cells, and their limitations

- Explain commonly used assist methods

- Explain how variations impact memory cells

Part 3- EDA

- Describe the role of CAD tools in VLSI Physical Design process.

- Explain various design phases and physical design flow

- Articulate the commonly used algorithms in physical design tools

- Detailed understanding of placement and routing techniques.

- Describe the role of physical synthesis in design closure

- Incremental synthesis and optimization and its role in physical design closure

Class 1 (12 Jan 2017)

- Introduction

- Refresher of basic concepts form digital IC design

- 6T SRAM operation and sizing

Key References:

K. Roy, S. Mukhopadhyay and H. Mahmoodi-Meimand, “Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits,” in Proceedings of the IEEE, vol. 91, no. 2, pp. 305-327, Feb 2003.

Class 2 (19 Jan 2017)

- Memory Hierarchy

- SRAM and eDRAM comparison

- eDRAM functionality

- 3T Micro Sense Amplifier

Key References:

Barth, J. et al., “A 500 MHz Random Cycle, 1.5 ns Latency, SOI Embedded DRAM Macro Featuring a Three-Transistor Micro Sense Amplifier,” IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 43, NO. 1, JANUARY 2008. PDF

Class 3 (28 Jan 2017)

Saturday - 2:00 - 430 PM

LTSpice Simulator: http://www.linear.com/designtools/software/#LTspice

22nm PTM Models:

Assignment 1

Class 4 (2 Feb 2017)

* Gated Feedback Sense Amplifier

Key Reference:

Gregory Fredeman, et. al. A 14 nm 1.1 Mb Embedded DRAM Macro With 1 ns Access. J. Solid-State Circuits 51(1): 230-239 (2016) PDF

In class quiz:

Class 5 (9 Feb 2017)

Probability Theory Tutorial

Class 6 (16 Feb 2017)

Importance sampling

Key Reference:

R. Kanj, et. al., “Mixture importance sampling and its application to the analysis of SRAM designs in the presence of rare failure events,” 2006 43rd ACM/IEEE Design Automation Conference, San Francisco, CA, 2006, pp. 69-72.PDF

Class 7 (23 Feb 2017)

In class quiz:

- 6T SRAM cell

- Static/ Read and Write noise margins

- Read/ Write/ Hold and Access failures

- Column interleaving

Assignment 2

Class 8 (2 Mar 2017)

- 8T SRAM cell

- 10T SRAM cell

- Asymmetric cells

- Sub-threshold cells

- Low leakage cells

Class 9 (9 Mar 2017)

- High Performance SRAM design

- Impact of variation

- Assist circuits

Class 10 (16 Mar 2017)

- BTI Effects

- Stress in SRAM

- Testing and Faults

- March patterns

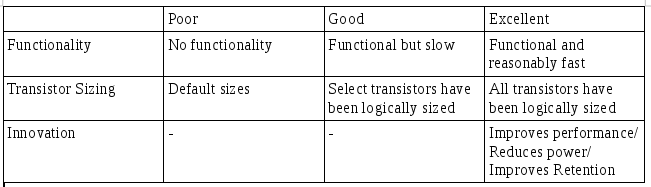

Assignment 3

Due on: 27th Mar 2017 (11:55 PM)

H. Pilo et al., “A 64Mb SRAM in 32nm High-k metal-gate SOI technology with 0.7V operation enabled by stability, write-ability and read-ability enhancements,” 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, 2011, pp. 254-256. doi: 10.1109/ISSCC.2011.5746307[PDF]

Self Study Seminar

Due on: 12 and 14 Apr 2017 5:00 - 6:00 PM- Will split the groups across two one hour sessions based on convenience

- Work in groups of 2

- Each group will be assigned 1 of 3 papers given below

- Each group will make a 15 min presentation to the class

- Speaker will be switched arbitrarily in between by the teacher

- Presentation should include

- Introduction to basic TCAMs

- The problem with the traditional TCAM

- Key concept of the proposal

- Key results shown in the paper

- Conclusion - Potential pit falls in the proposed design and suggested fix

- Simulation is not necessary but suitable simulation will carry bonus marks

List of Papers

- I. Arsovski and A. Sheikholeslami, “A current-saving match-line sensing scheme for content-addressable memories,” 2003 IEEE International Solid-State Circuits Conference, 2003. Digest of Technical Papers. ISSCC., San Francisco, CA, USA, 2003, pp. 304-494 vol.1. doi: 10.1109/ISSCC.2003.1234309

- I. Arsovski, T. Hebig, D. Dobson and R. Wistort, “1Gsearch/sec Ternary Content Addressable Memory compiler with silicon-aware Early-Predict Late-Correct single-ended sensing,” 2012 Symposium on VLSI Circuits (VLSIC), Honolulu, HI, 2012, pp. 116-117. doi: 10.1109/VLSIC.2012.6243817

- I. Arsovski, T. Chandler and A. Sheikholeslami, “A ternary content-addressable memory (TCAM) based on 4T static storage and including a current-race sensing scheme,” in IEEE Journal of Solid-State Circuits, vol. 38, no. 1, pp. 155-158, Jan 2003. doi: 10.1109/JSSC.2002.806264

Upload presentations here

Class 11 (23 Mar 2017)

- Introduction to Design Flow Lecture Slides

- Introduction to Design Automation Lecture Slides

Class 12 (30 Mar 2017)

- System and Netlist partitioning Lecture Slides

- Floor planning Lecture Slides

Class 13 (06 Apr 2017)

- Placement Lecture Slides

Class 14 (13 Apr 2017)

- Global Routing Lecture Slides

- Routing Lecture Slides

Class 15 (20 Apr 2017)

- Physical Synthesis Lecture Slides