# Floorplanning

Presented By: Sridhar H Rangarajan IBM STG India Enterprise Systems Development

# Chip Planning

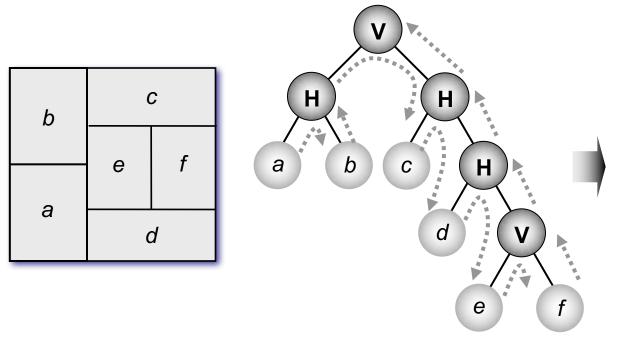

#### Introduction

- Floorplanning Algorithms

- Floorplan Sizing

- Cluster Growth

- Simulated Annealing

Power and Ground Routing

Design of a Power-Ground Distribution Network

Planar Routing Mesh Routing

### **Optimization Goals**

- Area and shape of the global bounding box

- Global bounding box of a floorplan is the minimum axis-aligned rectangle that contains all floorplan blocks.

- Area of the global bounding box represents the area of the top-level floorplan

- □ Minimizing the area involves finding (x, y) locations, as well as shapes, of the individual blocks.

- Total wirelength

- Long connections between blocks may increase signal propagation delays in the design.

- Combination of area area(F) and total wirelength L(F) of floorplan F

- □ Minimize  $\checkmark \cdot area(F) + (1 \checkmark) \cdot L(F)$ where the parameter  $0 \le \checkmark \le 1$  gives the relative importance between area(F) and L(F)

- Signal delays

- Static timing analysis is used to identify the interconnects that lie on critical paths.

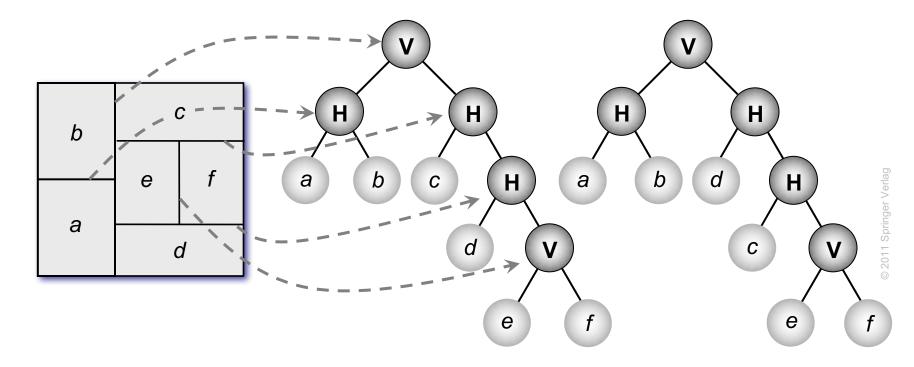

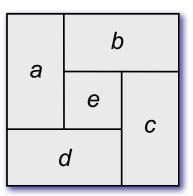

Slicing floorplan and two possible corresponding slicing trees

#### Polish expression

AB+CDEF\*++\*

- Bottom up:  $V \rightarrow *$  and  $H \rightarrow +$

- Length 2*n*-1 (*n* = Number of leaves of the slicing tree)

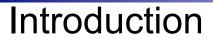

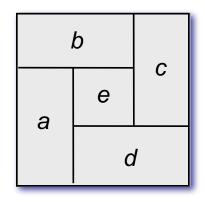

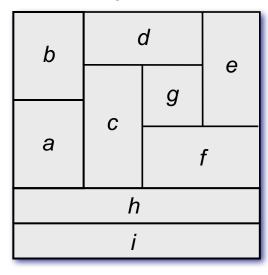

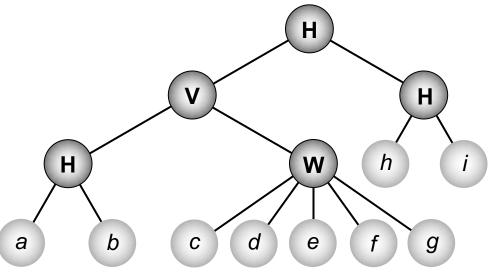

#### Non-slicing floorplans (wheels)

Floorplan tree: Tree that represents a hierarchical floorplan

H

Horizontal division (objects to the top and bottom) Vertical division

(objects to the left and right)

Wheel (4 objects cycled around a center object)

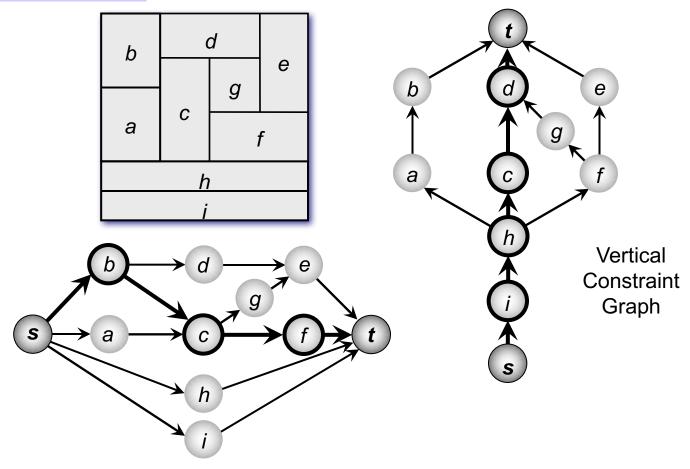

- In a vertical constraint graph (VCG), node weights represent the heights of the corresponding blocks.

- Two nodes  $v_i$  and  $v_j$ , with corresponding blocks  $m_i$  and  $m_j$ , are connected with a directed edge from  $v_i$  to  $v_j$  if  $m_i$  is below  $m_j$ .

- In a horizontal constraint graph (HCG), node weights represent the widths of the corresponding blocks.

- Two nodes  $v_i$  and  $v_j$ , with corresponding blocks  $m_i$  and  $m_j$ , are connected with a directed edge from  $v_i$  to  $v_j$  if  $m_i$  is to the left of  $m_j$ .

- The longest path(s) in the VCG / HCG correspond(s) to the minimum vertical / horizontal floorplan span required to pack the blocks (floorplan height / width).

- A constraint-graph pair is a floorplan representation that consists of two directed graphs – vertical constraint graph and horizontal constraint graph – which capture the relations between block positions.

#### Constraint graphs

Horizontal Constraint Graph

# Otten, R.: Efficient Floorplan Optimization. Int. Conf. on Computer Design, 499-502, 1983

#### **Floorplanning Algorithms**

**Common Goals**

• To minimize the total length of interconnect, subject to an upper bound on the floorplan area

or

• To simultaneously optimize both wire length and area

# Chip Planning

Introduction

Floorplanning Algorithms

Floorplan Sizing

Cluster Growth

Simulated Annealing

Power and Ground Routing

Design of a Power-Ground Distribution Network

Planar Routing

Mesh Routing

Floorplan Sizing

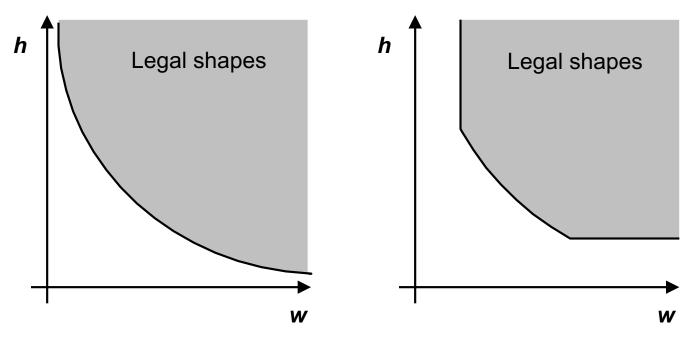

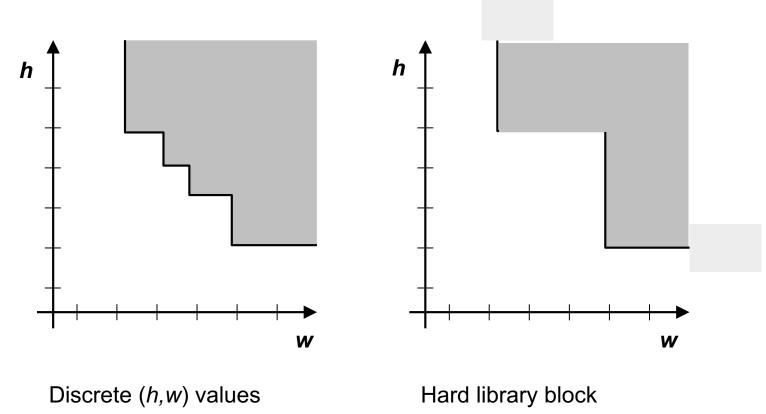

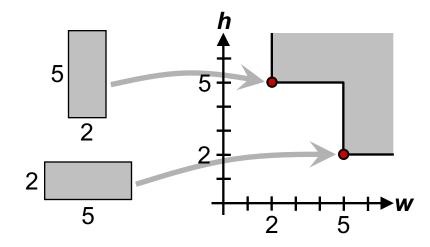

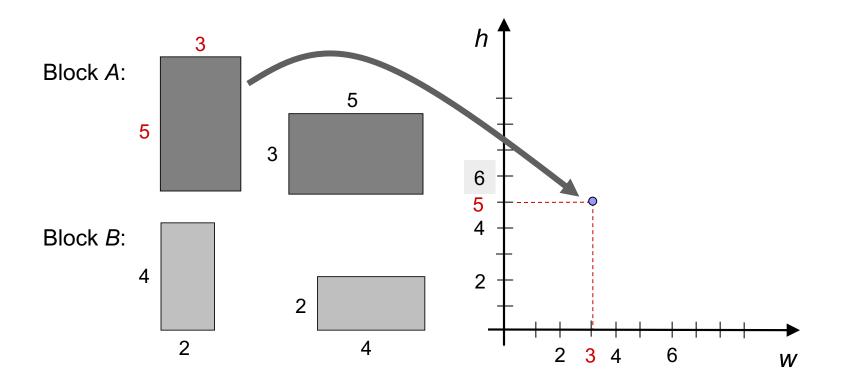

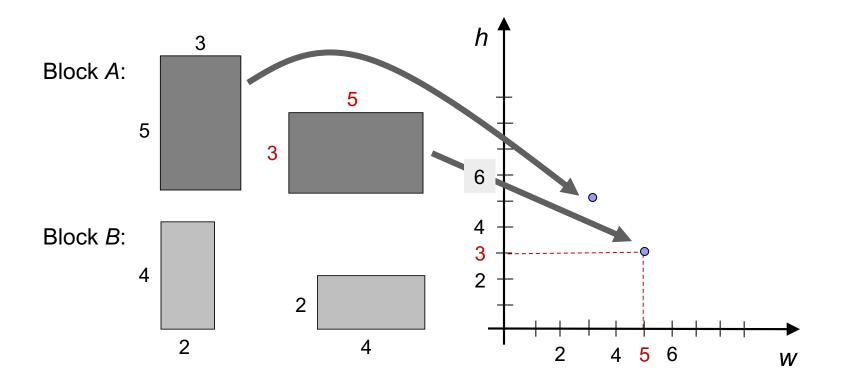

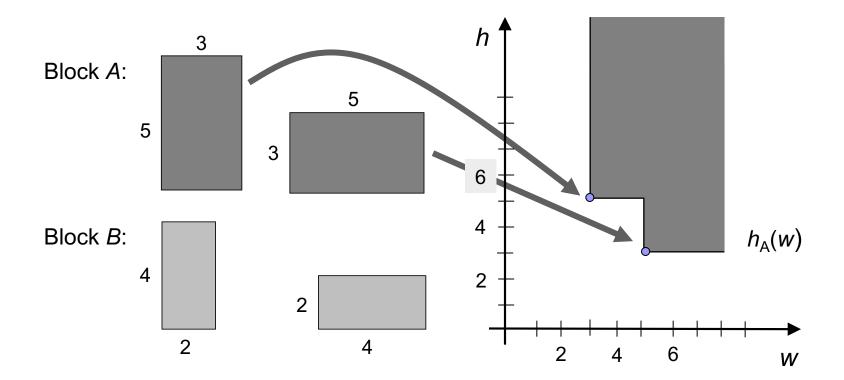

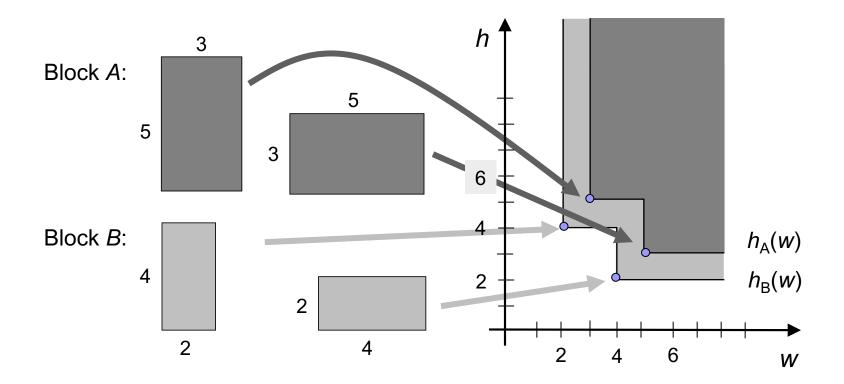

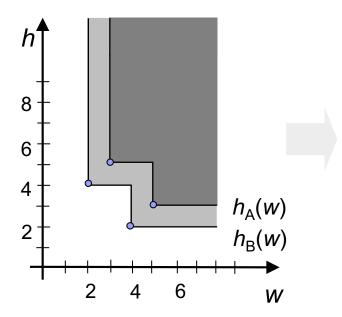

#### Shape functions

$h^* w \ge A$

Block with minimum width and height restrictions

Floorplan Sizing

#### Shape functions

#### Corner points

## Floorplan Sizing

- This algorithm finds the minimum floorplan area for a given slicing floorplan in polynomial time. For non-slicing floorplans, the problem is NP-hard.

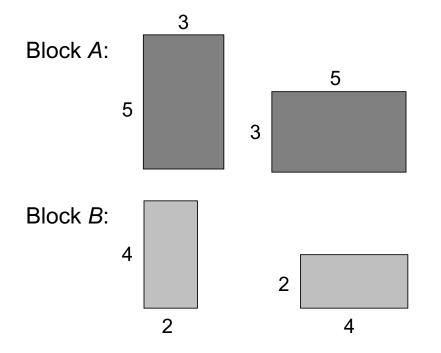

- Construct the shape functions of all individual blocks

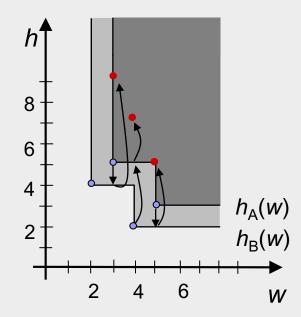

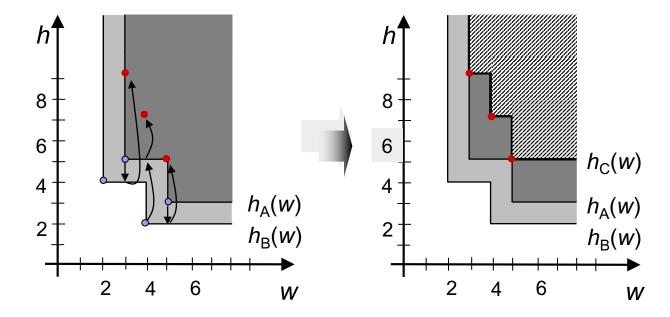

- Bottom up: Determine the shape function of the toplevel floorplan from the shape functions of the individual blocks

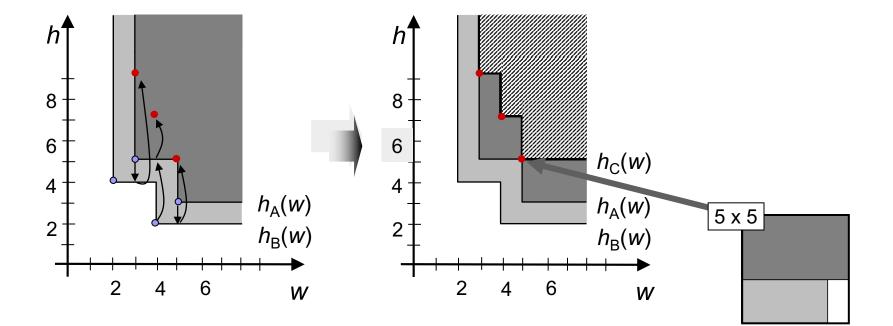

- Top down: From the corner point that corresponds to the minimum top-level floorplan area, trace back to each block's shape function to find that block's dimensions and location.

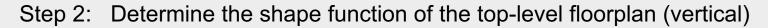

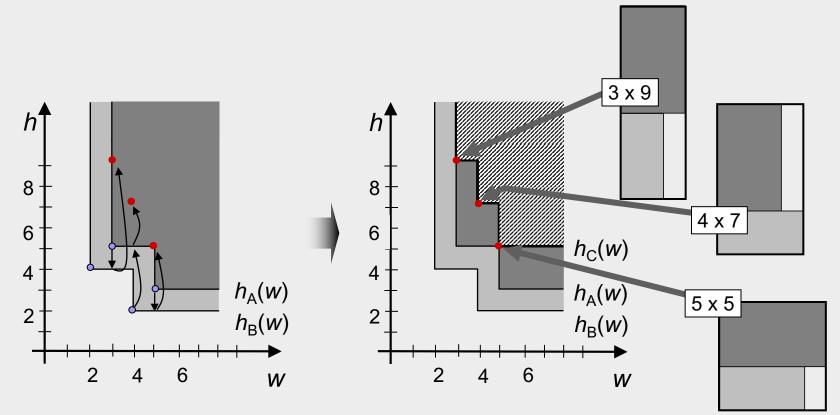

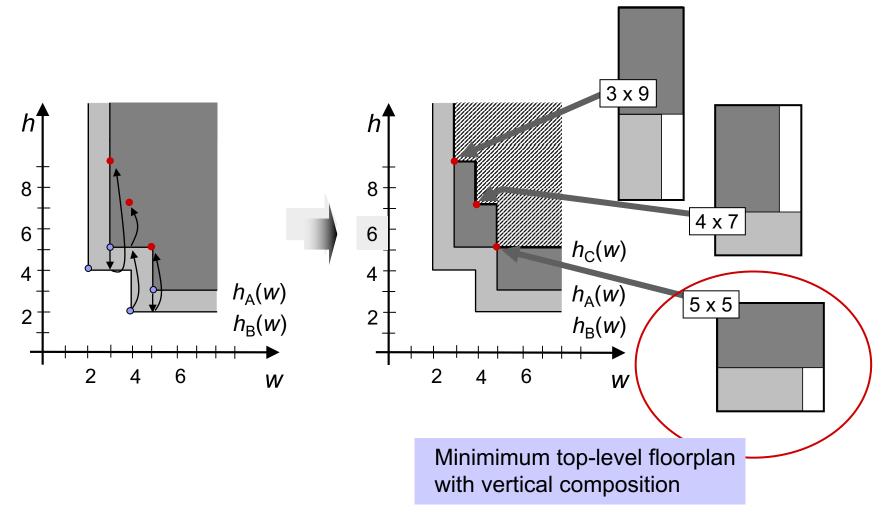

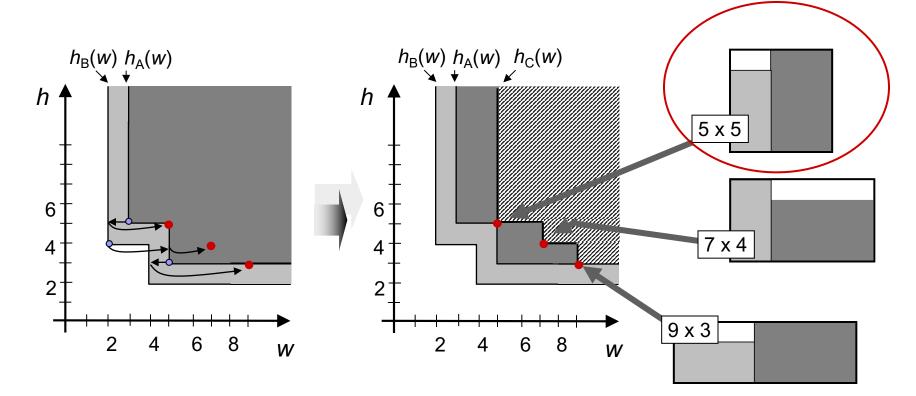

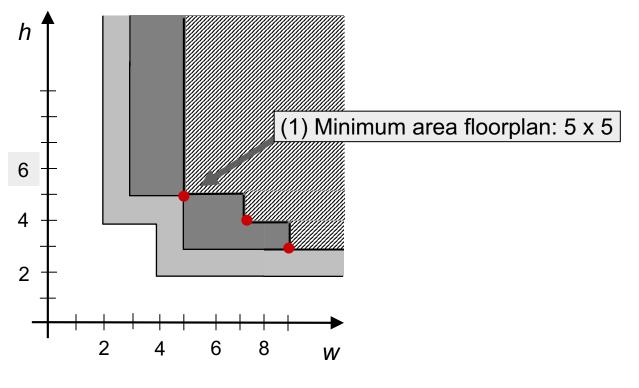

Step 2: Determine the shape function of the top-level floorplan (horizontal)

Minimimum top-level floorplan with horizontal composition

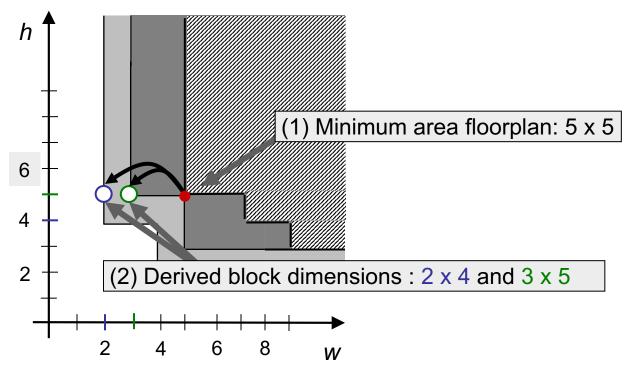

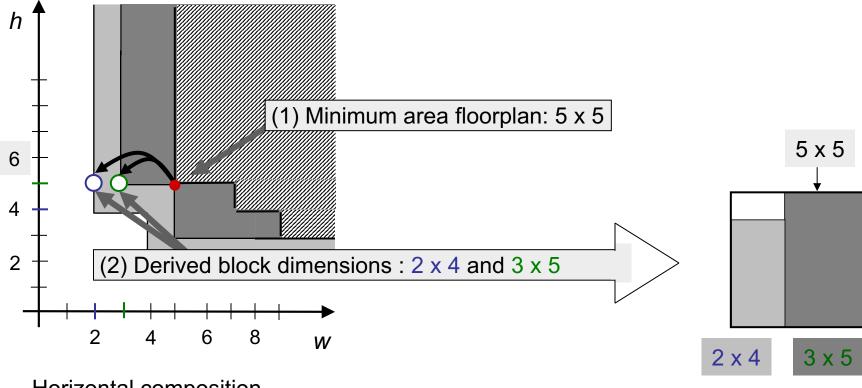

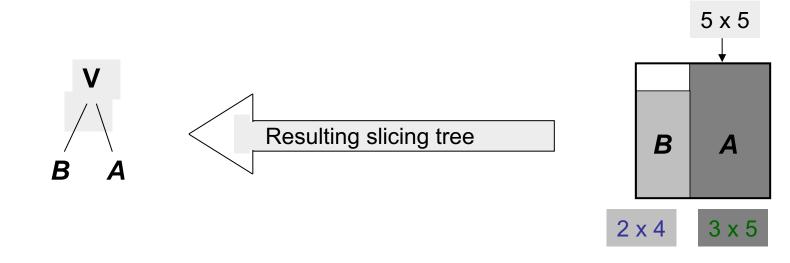

Step 3: Find the individual blocks' dimensions and locations

Horizontal composition

Step 3: Find the individual blocks' dimensions and locations

Horizontal composition

Step 3: Find the individual blocks' dimensions and locations

Horizontal composition

# Chip Planning

#### Introduction

Floorplanning Algorithms

Floorplan Sizing

Cluster Growth

Simulated Annealing

Power and Ground Routing

Design of a Power-Ground Distribution Network

Planar Routing

Mesh Routing

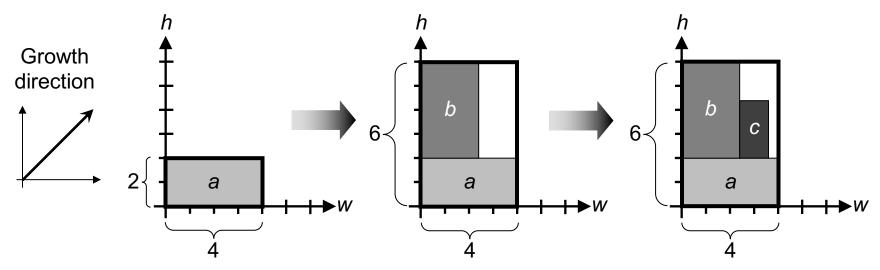

#### **Cluster Growth**

- Iteratively add blocks to the cluster until all blocks are assigned

- Only the different orientations of the blocks instead of the shape / aspect ratio are taken into account

- Linear ordering to minimize total wirelength of connections between blocks

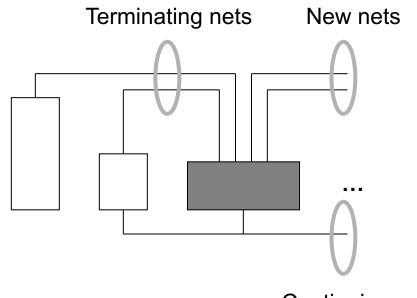

#### Cluster Growth – Linear Ordering

- New nets have no pins on any block from the partially-constructed ordering

- Terminating nets have no other incident blocks that are unplaced

- Continuing nets have at least one pin on a block from the partiallyconstructed ordering and at least one pin on an unordered block

Continuing nets

#### Cluster Growth – Linear Ordering

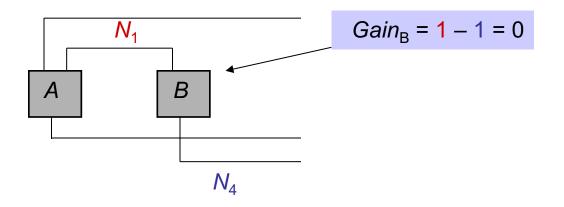

• Gain of each block *m* is calculated:

$Gain_m$  = (Number of terminating nets of *m*) – (New nets of *m*)

• The block with the maximum gain is selected to be placed next

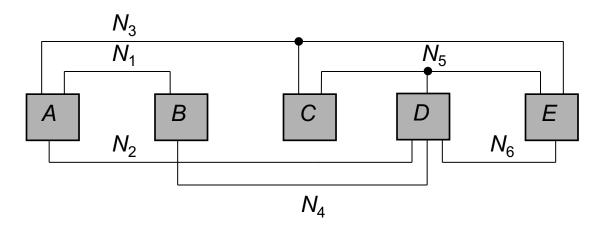

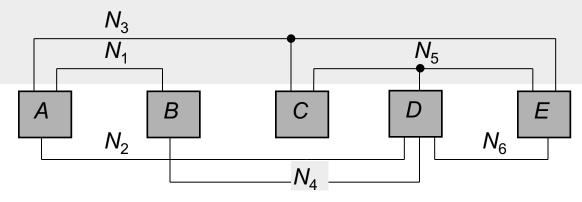

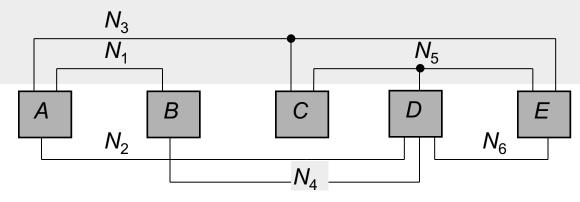

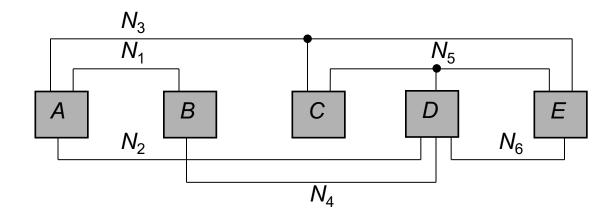

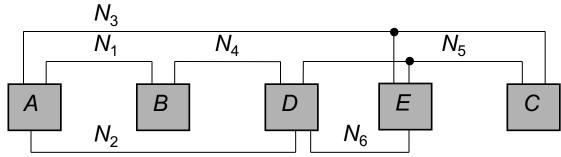

### Cluster Growth – Linear Ordering (Example)

#### Given:

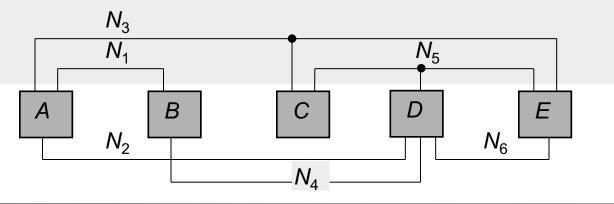

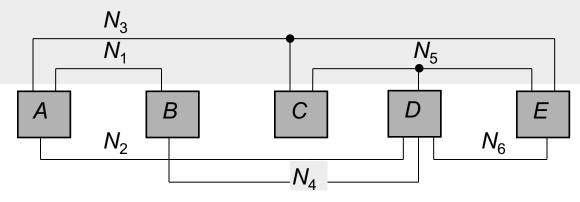

- Netlist with five blocks A, B, C, D, E and six nets N = (A, B)

- $N_1 = \{A, B\}$  $N_2 = \{A, D\}$

- $N_2 = \{A, C, E\}$

- $N_4 = \{B, D\}$

- $N_5 = \{C, D, E\}$  $N_6 = \{D, E\}$

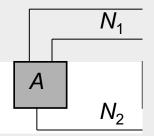

- Initial block: A

Task: Linear ordering with minimum netlength

| Iteration<br># | Block      | New Nets                                                       | Terminating<br>Nets | Gain | Continuing<br>Nets | • |  |

|----------------|------------|----------------------------------------------------------------|---------------------|------|--------------------|---|--|

| 0              | Α          | $N_{1}, N_{2}, N_{3}$                                          |                     | -3   |                    |   |  |

|                | Î          |                                                                |                     |      |                    |   |  |

| Ini            | tial block | $Gain_A = (Number of terminating nets of A) - (New nets of A)$ |                     |      |                    |   |  |

| Iteration<br># | Block | New Nets                                       | Terminating<br>Nets | Gain | Continuing<br>Nets |

|----------------|-------|------------------------------------------------|---------------------|------|--------------------|

| 0              | Α     | N <sub>1</sub> ,N <sub>2</sub> ,N <sub>3</sub> |                     | -3   |                    |

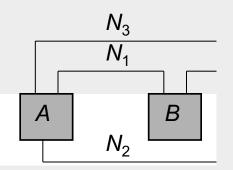

| 1              | В     | N <sub>4</sub>                                 | N <sub>1</sub>      |      |                    |

|                | С     | N <sub>5</sub>                                 |                     | -1   | N <sub>3</sub>     |

|                | D     | $N_4, N_5, N_6$                                | N <sub>2</sub>      | -2   |                    |

|                | E     | $N_4, N_5, N_6$<br>$N_5, N_6$                  |                     | -2   | N <sub>3</sub>     |

| Iteration<br># | Block            | New Nets                                                                           | Terminating<br>Nets                      | Gain                | Continuing<br>Nets                       |

|----------------|------------------|------------------------------------------------------------------------------------|------------------------------------------|---------------------|------------------------------------------|

| 0              | А                | $N_{1}, N_{2}, N_{3}$                                                              |                                          | -3                  |                                          |

| 1              | B<br>C<br>D<br>E | $N_4 \\ N_5 \\ N_4, N_5, N_6 \\ N_5, N_6$                                          | N <sub>1</sub><br><br>N <sub>2</sub><br> | 0<br>-1<br>-2<br>-2 | <br>N <sub>3</sub><br><br>N <sub>3</sub> |

| 2              | C<br>D<br>E      | N <sub>5</sub><br>N <sub>5</sub> ,N <sub>6</sub><br>N <sub>5</sub> ,N <sub>6</sub> | <br>N <sub>2</sub> ,N <sub>4</sub><br>   | 1<br>0<br>-2        | N <sub>3</sub><br><br>N <sub>3</sub>     |

| Iteration<br># | Block            | New Nets                                                                           | Terminating<br>Nets                      | Gain                | Continuing<br>Nets                                               |

|----------------|------------------|------------------------------------------------------------------------------------|------------------------------------------|---------------------|------------------------------------------------------------------|

| 0              | Α                | $N_{1}, N_{2}, N_{3}$                                                              |                                          | -3                  |                                                                  |

| 1              | B<br>C<br>D<br>E | $N_4 \\ N_5 \\ N_4, N_5, N_6 \\ N_5, N_6$                                          | N <sub>1</sub><br><br>N <sub>2</sub><br> | 0<br>-1<br>-2<br>-2 | <br>N <sub>3</sub><br><br>N <sub>3</sub>                         |

| 2              | C<br>D<br>E      | N <sub>5</sub><br>N <sub>5</sub> ,N <sub>6</sub><br>N <sub>5</sub> ,N <sub>6</sub> | <br>N <sub>2</sub> ,N <sub>4</sub><br>   | -1<br>0<br>-2       | N <sub>3</sub><br><br>N <sub>3</sub>                             |

| 3              | C<br>E           |                                                                                    | <br>N <sub>6</sub>                       | 0<br>1              | N <sub>3</sub> ,N <sub>5</sub><br>N <sub>3</sub> ,N <sub>5</sub> |

|                | Î                |                                                                                    |                                          | 1                   |                                                                  |

#### Cluster Growth – Linear Ordering (Example)

41

## Cluster Growth – Algorithm

**Input:** set of all blocks *M*, cost function *C* **Output:** optimized floorplan *F* based on *C*

$F = \emptyset$

order = LINEAR\_ORDERING(M)

for (i = 1 to |order|)

curr\_block = order[i]

ADD\_TO\_FLOORPLAN(F,curr\_block,C)

// generate linear ordering

// find location and orientation

// of curr\_block that causes

// smallest increase based on

// C while obeying constraints

### **Cluster Growth**

#### Analysis

- The objective is to minimize the total wirelength of connections blocks

- Though this produces mediocre solutions, the algorithm is easy to implement and fast.

- Can be used to find the initial floorplan solutions for iterative algorithms such as *simulated annealing*.

# Chip Planning

#### Introduction

Floorplanning Algorithms

Floorplan Sizing

Cluster Growth

Simulated Annealing

Power and Ground Routing

Design of a Power-Ground Distribution Network

Planar Routing

Mesh Routing

Introduction

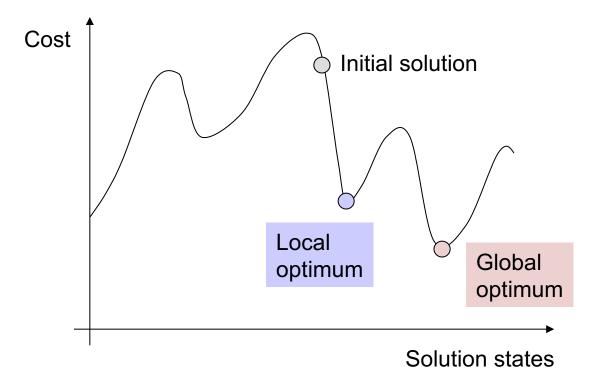

- Simulated Annealing (SA) algorithms are iterative in nature.

- Begins with an initial (arbitrary) solution and seeks to incrementally improve the objective function.

- During each iteration, a local neighborhood of the current solution is considered. A new candidate solution is formed by a small perturbation of the current solution.

- Unlike greedy algorithms, SA algorithms can accept candidate solutions with higher cost.

What is annealing?

- Definition (from material science): controlled cooling process of high-temperature materials to modify their properties.

- Cooling changes material structure from being highly randomized (chaotic) to being structured (stable).

- The way that atoms settle in low-temperature state is probabilistic in nature.

- Slower cooling has a higher probability of achieving a perfect lattice with minimum-energy

- Cooling process occurs in steps

- Atoms need enough time to try different structures

- Sometimes, atoms may move across larger distances and create (intermediate) higher-energy states

- Probability of the accepting higher-energy states decreases with temperature

**Simulated Annealing**

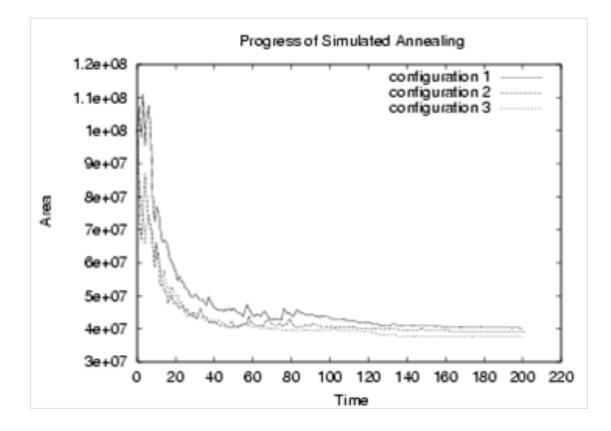

- Generate an initial solution S<sub>init</sub>, and evaluate its cost.

- Generate a new solution S<sub>new</sub> by performing a random walk

- $S_{new}$  is accepted or rejected based on the temperature T

- Higher T means a higher probability to accept  $S_{new}$  if  $COST(S_{new}) > COST(S_{init})$

- T slowly decreases to form the final solution

- Boltzmann acceptance criterion, where r is a random number [0,1)

$$e^{\frac{COST(S_{init}) - COST(S_{new})}{T}} > r$$

Simulated Annealing

- Generate an initial solution and evaluate its cost

- Generate a new solution by performing a random walk

- Solution is accepted or rejected based on a temperature parameter T

- Higher T indicates higher probability to accept a solution with higher cost

- T slowly decreases to form the finalized solution.

- Boltzmann acceptance criterion:

$e^{\frac{cost(curr_{sol}) - cost(next_{sol})}{T}} >$

curr<sub>sol</sub> : current solution

next<sub>sol</sub>: new solution after perturbation

T: current temperature

r: random number between[0,1) from normal distr.

#### Simulated Annealing – Algorithm

### Simulated Annealing – Algorithm

Input: initial solution init\_sol

Output: optimized new solution curr\_sol

$T = T_0$ i = 0curr sol = init sol *curr cost* = COST(*curr sol*) while  $(T > T_{min})$ while (stopping criterion is not met) i = i + 1 $(a_i, b_i) = SELECT_PAIR(curr_sol)$ trial sol = TRY MOVE $(a_i, b_i)$ *trial cost* = COST(*trial sol*)  $\triangle cost = trial cost - curr cost$ if  $(\triangle cost < 0)$ *curr cost* = *trial cost* curr sol =  $MOVE(a_i, b_i)$ else r = RANDOM(0,1)if  $(r < e^{-\Delta cost/T})$ *curr cost* = *trial cost* curr sol =  $MOVE(a_i, b_i)$  $T = \alpha \cdot T$

#### // initialization

// select two objects to perturb

// try small local change

// if there is improvement,

// update the cost and

// execute the move

// random number [0,1]

// if it meets threshold,

// update the cost and

// execute the move

// 0 <  $\alpha$  < 1, *T* reduction

# Chip Planning

#### Introduction

Floorplanning Algorithms

Floorplan Sizing

Cluster Growth

Simulated Annealing

#### Power and Ground Routing

Design of a Power-Ground Distribution Network

Planar Routing

Mesh Routing

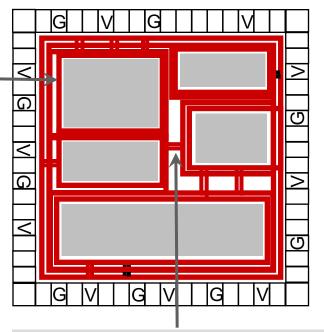

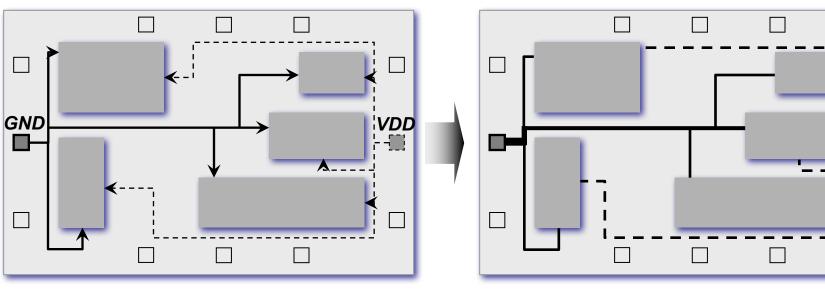

Power-ground distribution for a chip floorplan

Power and ground rings per block or abutted blocks

Trunks connect rings to each other or to top-level power ring

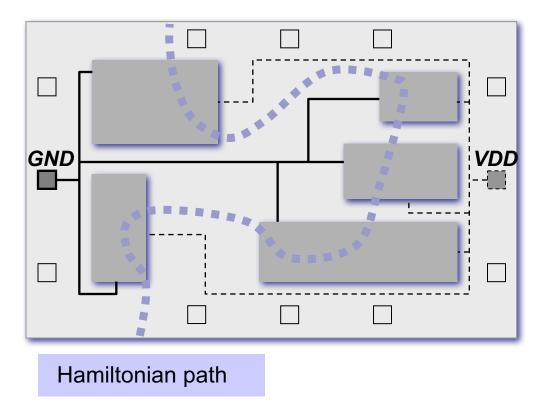

Planar routing

Planar routing

#### Step 1: Planarize the topology of the nets

As both power and ground nets must be routed on one layer, the design should be split using the Hamiltonian path

#### Step 2: Layer assignment

□ Net segments are assigned to appropriate routing layers

Step 3: Determining the widths of the net segments

A segment's width is determined from the sum of the currents from all the cells to which it connects

Planar routing

Generating topology of the two supply nets

Adjusting widths of the segments with regard to their current loads

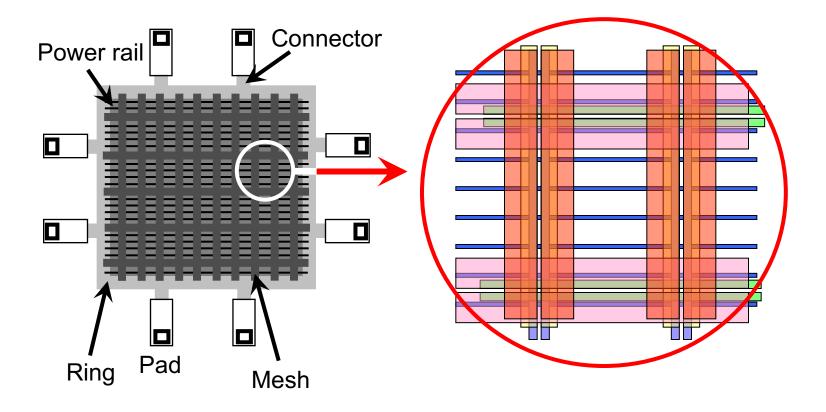

Mesh routing

#### Step 1: Creating a ring

A ring is constructed to surround the entire core area of the chip, and possibly individual blocks.

Step 2: Connecting I/O pads to the ring

Step 3: Creating a mesh

A power mesh consists of a set of stripes at defined pitches on two or more layers

#### Step 4: Creating Metal1 rails

Power mesh consists of a set of stripes at defined pitches on two or more layers

Step 5: Connecting the Metal1 rails to the mesh

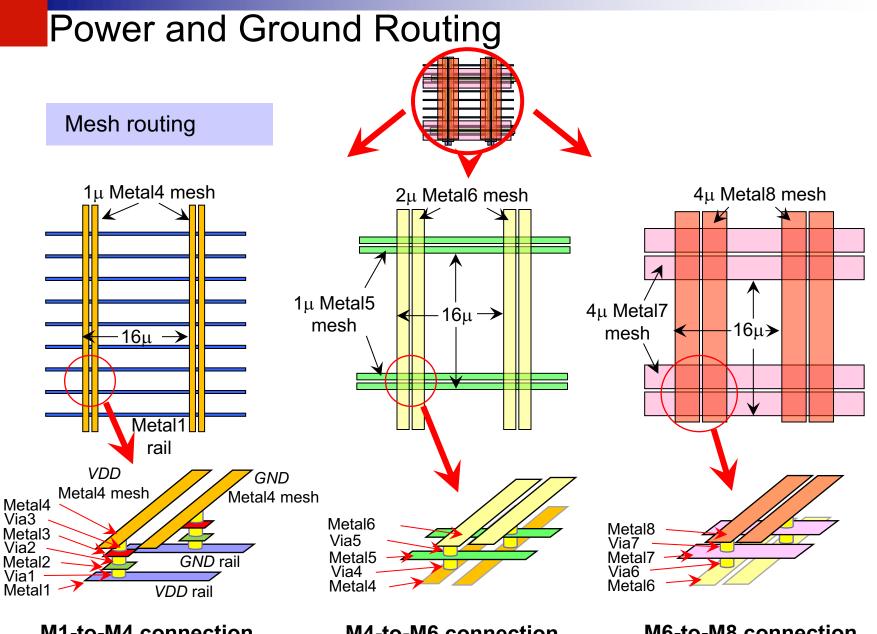

#### Mesh routing

M1-to-M4 connection

M4-to-M6 connection

M6-to-M8 connection

# Summary

- Traditional floorplanning

- Assumes area estimates for top-level circuit modules

- Determines shapes and locations of circuit modules

- Minimizes chip area and length of global interconnect

#### Additional aspects

- Assigning/placing I/O pads

- Defining channels between blocks for routing and buffering

- □ Design of power and ground networks

- Estimation and optimization of chip timing and routing congestion

- Fixed-outline floorplanning

- □ Chip size is fixed, focus on interconnect optimization

- Can be applied to individual chip partitions (hierarchically)

- Structure and types of floorplans

- □ Slicing versus non-slicing, the wheels

- Hierarchical

- Packed

- Zero-deadspace

### Summary - Data Structures for Floorplanning

- Slicing trees and Polish expressions

Evaluating a floorplan represented by a Polish expression

- Horizontal and vertical constraint graphs

A data structure to capture (non-slicing) floorplans

Longest paths determine floorplan dimensions

- Floorplan sizing

- □ Shape-function arithmetic

# Summary - Algorithms for Floorplanning

Floorplan Slicing - An algorithm for slicing floorplans

#### Cluster growth

- □ Simple, fast and intuitive

- Not competitive in practice

- Simulated annealing

- Stochastic optimization with hill-climbing

- Many details required for high-quality implementation (e.g., temperature schedule)

- Difficult to debug, fairly slow

- Competitive in practice

- Power and ground routing

- Planar routing in channels between blocks

- Can form rings around blocks to increase current supplied and to improve reliability

- Mesh routing