# Negative Feedback System and Circuit Design 22<sup>nd</sup> International Conference on VLSI Design, New Delhi

#### Nagendra Krishnapura Shanthi Pavan

Department of Electrical Engineering Indian Institute of Technology, Madras Chennai, 600036, India

9 January 2009

#### **Outline**

- Basics

- Negative feedback amplifier basics

- Negative feedback amplifier realization

- Stability and compensation

- Stability in Negative Feedback Systems

- Dominant pole frequency compensation

- Feedback around transistors

- Negative Feedback for Bias Stabilization

- Negative Feedback in Single Transistor Circuits

- CMOS opamps—1, 2, and 3 stages

- Amplifier Nonlinearity in Negative Feedback Systems

- Case studies

- A 7X Programmable 5<sup>th</sup> Order Active-RC Filter

- Lead lag compensation

# Negative feedback amplifier basics

#### Goals

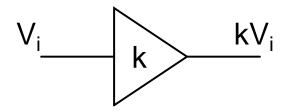

Realize an amplifier with a gain k using negative feedback

- with a high gain accuracy

- with a high speed

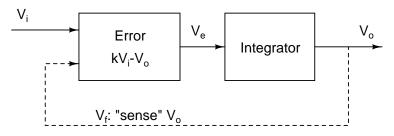

#### Negative feedback

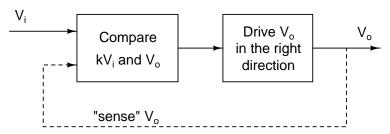

Sense the difference between desired and actual output, and drive the output in the right direction

- Controlling the speed of a vehicle

- Controlling the volume of an audio player

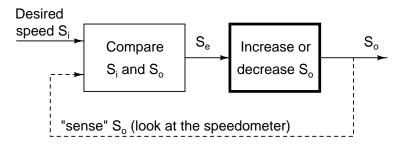

#### Speed control

Input: Desired speed

Sense: Speedometer reading

Drive: Proportional to the difference

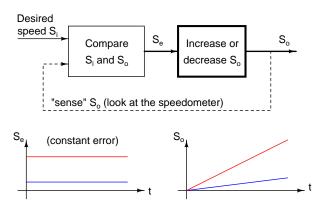

#### Speed control-driving block behavior

- Output ramps up for constant error

- Ramp rate proportional to error

Integrate the error  $S_e$  to drive the output

#### Integrator in the forward path

- At steady state,  $V_f = V_i$  (constant input  $V_i$ )

- Zero steady state error

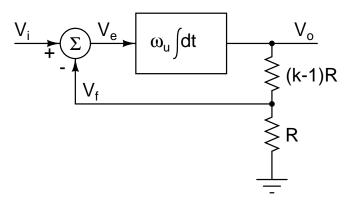

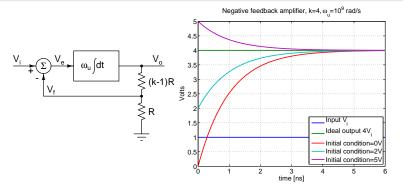

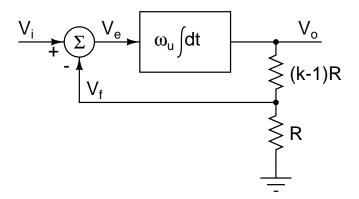

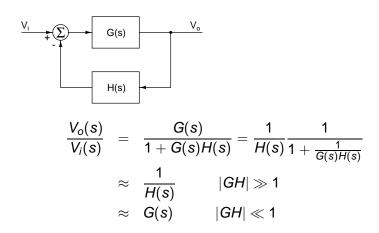

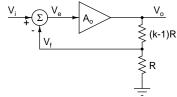

#### Negative feedback amplifier using an integrator

- Zero steady state error for constant inputs:  $V_f = V_i$

- For an amplifier of gain k,  $V_o = kV_i \Rightarrow$  use  $V_f = V_o/k$

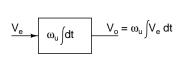

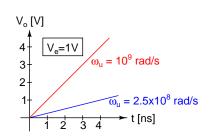

#### Integrator: Time domain

- Described by a single parameter ω<sub>u</sub>

- Higher  $\omega_u \Rightarrow$  faster integration

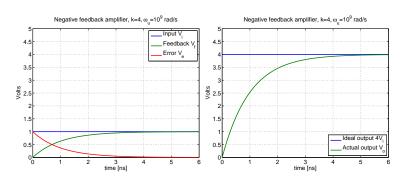

#### Negative feedback amplifier using an integrator

- Error reduces as feedback V<sub>f</sub> ramps up

- Reduced error slows the rate of output ramp

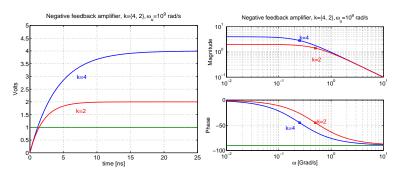

#### Negative feedback amplifier: Constant input

$$\frac{dV_o}{dt} = \omega_u \left( V_i - \frac{V_o}{k} \right)

V_o(t) = kV_i \left( 1 - \exp(-\frac{\omega_u}{k}t) \right) + V_o(0) \exp(-\frac{\omega_u}{k}t)$$

Output exponentially approaches the steady state of kV<sub>i</sub>

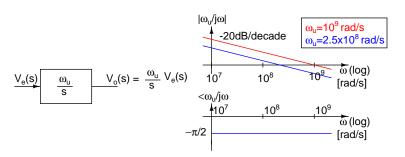

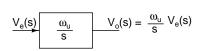

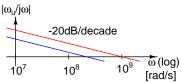

#### Integrator: Frequency domain

- Described by a single parameter ω<sub>u</sub>

- $\omega_u$ : "unity gain frequency"

- Higher  $\omega_u \Rightarrow$  higher gain magnitude for all frequencies

#### Integrator: Summary

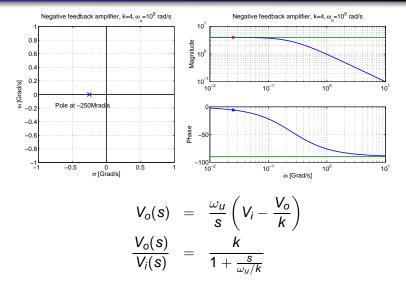

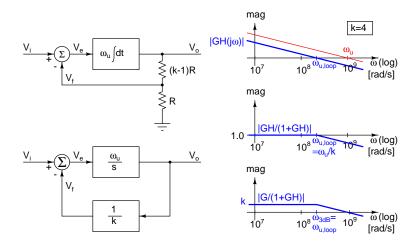

#### Negative feedback amplifier: Frequency domain

• First order response; DC gain = k, pole at  $\omega_u/k$

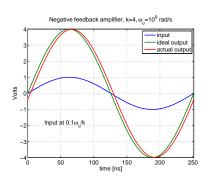

## Negative feedback amplifier: Sinusoidal input

$$\frac{V_o(j\omega)}{V_i(j\omega)} = \frac{k}{1 + \frac{j\omega}{\omega_u/k}}$$

$$\left| \frac{V_o(j\omega)}{V_i(j\omega)} \right| = \frac{k}{\sqrt{1 + \left(\frac{\omega}{\omega_u/k}\right)^2}} \quad ; \quad \angle \frac{V_o(j\omega)}{V_i(j\omega)} = -\tan^{-1}\frac{\omega}{\omega_u/k}$$

- dc gain: k (= desired value)

- 3 dB bandwidth:  $\omega_u/k$

#### Negative feedback amplifier: Low frequency input

$$\left| \frac{V_o(j\omega)}{V_i(j\omega)} \right| = \frac{k}{\sqrt{1 + \left(\frac{\omega}{\omega_u/k}\right)^2}}$$

$$\approx k$$

$$\angle \frac{V_o(j\omega)}{V_i(j\omega)} = -\tan^{-1}\frac{\omega}{\omega_u/k}$$

$$\approx \frac{\omega}{\omega_u/k}$$

- Nearly ideal behavior

- Gain k, delay  $k/\omega_u$

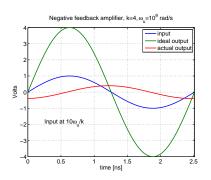

#### Negative feedback amplifier: High frequency input

$$\left| \frac{V_o(j\omega)}{V_i(j\omega)} \right| = \frac{k}{\sqrt{1 + \left(\frac{\omega}{\omega_u/k}\right)^2}}$$

$$\approx \frac{\omega}{\omega_u}$$

$$\angle \frac{V_o(j\omega)}{V_i(j\omega)} = -\tan^{-1}\frac{\omega}{\omega_u/k}$$

$$\approx -\frac{\pi}{2}$$

- Attenuated output

- Nearly 90° phase lag

## Negative feedback amplifier: Summary

- Integrate the error  $V_i V_o/k$  to drive the output

- Ideal steady state output for constant inputs

- Nearly ideal output for "slow" inputs; constant delay  $k/\omega_u$

- Attenuated output for "fast" inputs; large phase lag

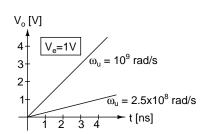

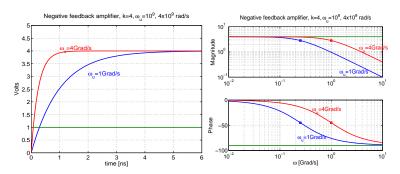

#### Negative feedback amplifier: Effect of $\omega_u$

- Time constant:  $k/\omega_u$

- Higher  $\omega_u \Rightarrow$  Faster response

- Bandwidth:  $\omega_u/k$

- Higher  $\omega_u \Rightarrow$  Desired gain over a wider frequency range

#### Negative feedback amplifier: Effect of k

- Higher  $k \Rightarrow$  longer time to reach steady state

- Gain bandwidth product:  $\omega_u$

- Bandwidth:  $\omega_u/k$

- Higher  $k \Rightarrow$  Smaller bandwidth

#### Example

#1: k = 4, bandwidth  $f_{3dB} = 100 \,\text{MHz}$ .

- Bandwidth (in rad/s) =  $\omega_u/k = 2\pi f_{3dB}$

- Require an integrator with  $\omega_u = 8\pi \times 100$  Mrad/s = 2.514 Grad/s

#2: k = 4, 99% settling time  $\tau_s = 20 \,\mathrm{ns}$

• Require an integrator with  $\omega_u = 2k \ln(10)/\tau_s = 0.92$  Grad/s

(These numbers apply only to the configuration shown in the above figure)

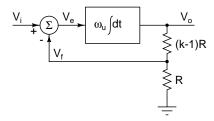

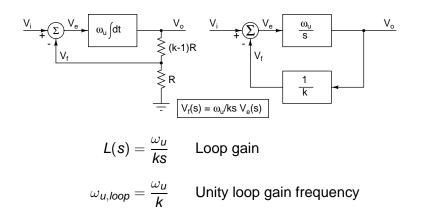

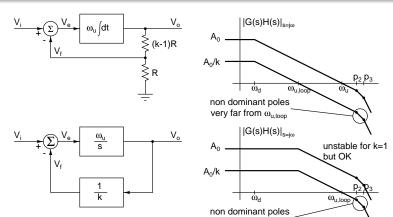

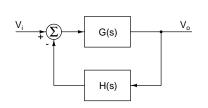

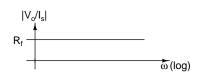

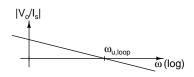

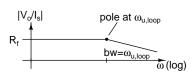

- Loop gain L(s) = G(s)H(s)

- Feedback effectively broken when  $|L| \ll 1 : V_o/V_i \approx G(s)$

- Nearly ideal behavior below  $\omega_{u,loop}$

- Nonideal behavior above  $\omega_{u,loop}$

- 3 dB bandwidth =  $\omega_{u,loop}$ , the unity loop gain frequency

- In general closed loop system bandwidth (region of ideal behavior) comprises regions of high loop gain

#### For our amplifier

- Unity loop gain frequency  $\omega_{u,loop} = \omega_u/k$

- $\omega_{u,loop}$  is not always  $\omega_u$  divided by the closed loop gain k!

- $\omega_{u,loop}$  is the unity gain frequency of G(s)H(s)

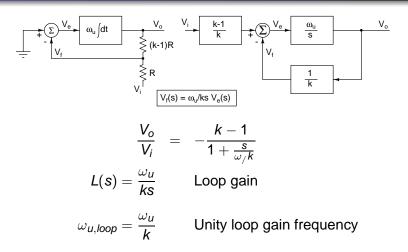

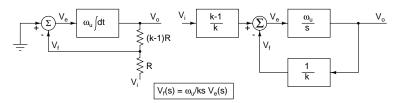

#### Inverting amplifier

ullet  $\omega_{u,loop}$  depends on the feedback factor, not the closed loop gain

#### Inverting amplifier

- Loop gain, stability are properties of the loop

- Transfer function depends on the input/output locations

## Negative feedback: Integrator vs. high gain amplifier

- Easily related to intuitive notion of feedback

- Incorporates delay/finite bandwidth

- Ideal behaviour for constant inputs

- All feedback systems have "integrator-like" behaviour over some range

- $\omega_u = \infty$ : Ideal behavior for all frequencies

Negative feedback amplifier realization

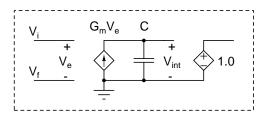

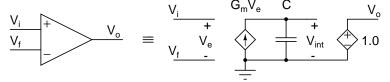

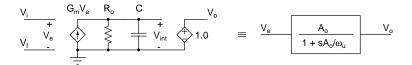

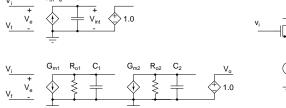

#### Negative feedback amplifier: Realization

$$V_o(s) = \frac{G_m}{sC}V_e(s)$$

- Difference input to sense  $V_i V_f$

- Integration using  $G_m C$ ;  $\omega_u = G_m/C$

- Buffer to isolate the load

Combination of differencing and integration: opamp

#### Operational amplifier (opamp)

Combination of differencing and integration: opamp

#### Integrator: Finite dc gain

$$V_{o}(s) = \frac{G_{m}R_{o}}{1 + sCR_{o}}V_{e}(s)$$

$$= \frac{1}{\frac{sC}{G_{m}} + \frac{1}{G_{m}R_{o}}}V_{e}(s)$$

$$= \frac{1}{\frac{s}{G_{m}} + \frac{1}{4}}V_{e}(s)$$

- Controlled current source has a finite output resistance R<sub>o</sub>

- Finite dc gain  $A_o = G_m R_o$

- Pole at  $-\omega_u/A_o$  instead of the origin

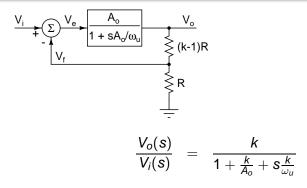

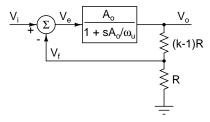

## Negative feedback amplifier: Finite dc gain

- Non zero steady state error for a constant input

- DC gain:  $k/(1 + k/A_0)$

- Relative error inversely proportional to dc loop gain  $A_o/k$

- Pole:  $\omega_u/k(1+k/A_0)\approx \omega_u/k$

#### Example

#1: k = 4, error  $\delta = 1\%$

- $k/(1 + k/A_0) = k(1 \delta)$

- $k/A_o \approx \delta = 0.01$

- Need an opamp with a dc gain  $A_0 = 400$

- Larger A<sub>o</sub> required for higher accuracy

- Larger A<sub>o</sub> required for higher gain k

(These numbers apply only to the configuration shown in the above figure)

## Negative feedback amplifier: Increasing gain accuracy

- DC gain:  $k/(1 + k/A_0)$

- Increase dc loop gain to increase gain accuracy

- Limited  $G_m R_o \Rightarrow$  Cascade many stages

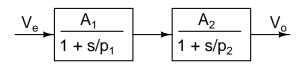

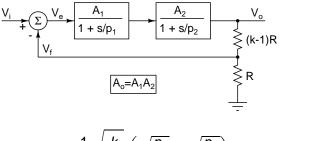

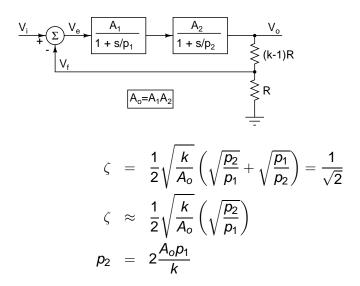

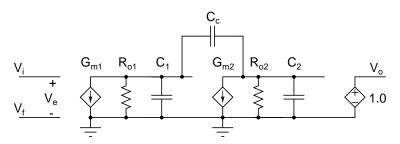

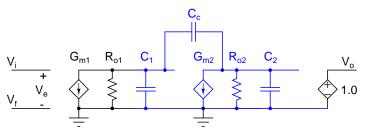

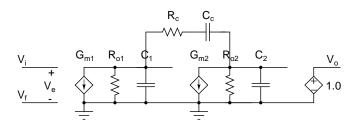

## Two stages in cascade

$$A_0 = A_1 A_2$$

- DC gain  $A_o = G_{m1}R_{o1}G_{m2}R_{o2}$

- Two poles at  $-p_1 = -1/R_{o1}C_1$ ,  $-p_2 = -1/R_{o2}C_2$

## Two stage amplifier in negative feedback

$$\begin{array}{c|c}

V_i & \Sigma & V_e & A_1 \\

\hline

1 + s/p_1 & 1 + s/p_2 & V_o \\

\hline

V_f & & & & & \\

\hline

A_0 = A_1 A_2 & & & & \\

\hline

R & & & & & \\

\hline$$

$$\frac{\sigma}{V_i} = \frac{1}{1 + \frac{k}{A_o} + s\left(\frac{1}{p_1} + \frac{1}{p_2}\right)\frac{k}{A_o} + \frac{s^2}{p_1p_2}\frac{k}{A_o}}}$$

$$\frac{k}{1 + \frac{k}{A_o}} \qquad A_o \text{ much larger than before}$$

$$\zeta = \frac{1}{2} \sqrt{\frac{k}{A_o}} \left( \sqrt{\frac{p_2}{p_1}} + \sqrt{\frac{p_1}{p_2}} \right)$$

Damping factor

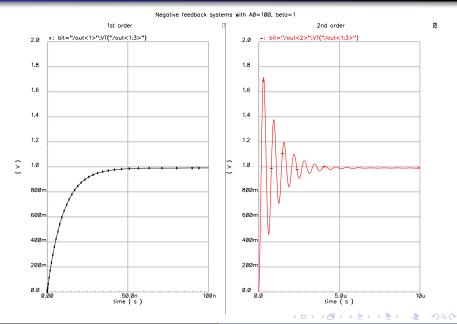

## Two stage amplifier in negative feedback

$$\zeta = \frac{1}{2} \sqrt{\frac{k}{A_0} \left( \sqrt{\frac{p_2}{p_1}} + \sqrt{\frac{p_1}{p_2}} \right)}$$

Damping factor

- Higher  $A_o/k \Rightarrow$  reduced steady state error

- Small damping factor for large A<sub>o</sub>/k—Lot of ringing

- Damping factor increased by increasing the ratio  $p_2/p_1$

- Poles well separated ⇒ less ringing

## Two stage amplifier in negative feedback

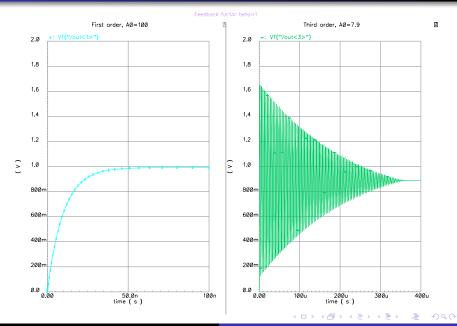

## Three stage amplifier in negative feedback

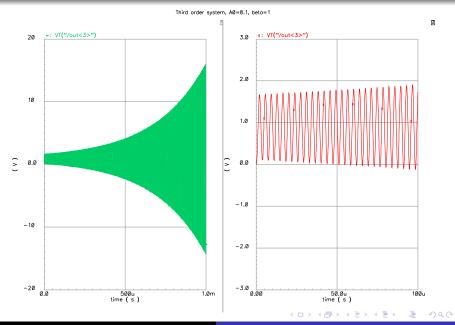

- Amplifier has 3 poles at  $-p_1$

- Poles at  $\pm j\sqrt{3}p_1$  for  $A_o/k=8$

- Instability for  $A_o/k \ge 8$ , but require *much* larger values!

## Three stage amplifier in negative feedback

# Three stage amplifier in negative feedback

## Realizing accurate amplifiers: Problem

- Large A<sub>o</sub>/k required for high accuracy

- Stage A<sub>o</sub> limited by finite R<sub>o</sub>

- Larger A<sub>o</sub> from cascaded stages, but . . . low damping, ringing, instability

## Realizing accurate amplifiers: Remedy

$$\zeta = \frac{1}{2} \sqrt{\frac{k}{A_o}} \left( \sqrt{\frac{p_2}{p_1}} + \sqrt{\frac{p_1}{p_2}} \right)$$

Damping factor

Results from two cascaded stages provides a possible way out

- Move the poles apart

- Ratio of poles should be  $\sim A_o/k$  (damping factor around 1)

# For a damping factor of $\sqrt{2}$

## Multiple poles: Frequency domain view

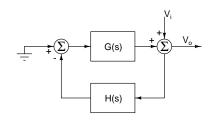

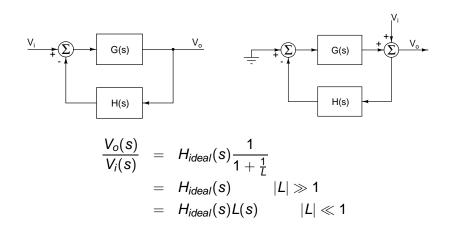

$$\begin{array}{lcl} \frac{V_o(s)}{V_i(s)} & = & \frac{G(s)}{1 + G(s)H(s)} \\ & = & \frac{1}{H(s)} \frac{1}{1 + \frac{1}{G(s)H(s)}} \end{array}$$

- Instability if loop gain L=GH=-1, i.e. |L|=1 and  $\angle L=-\pi$

- When GH has only poles and no zeros, instability if |L|>1 and  $\angle L=-\pi$

- Avoid this condition to ensure stability

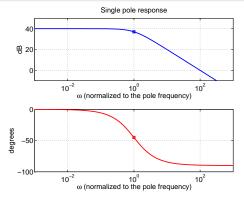

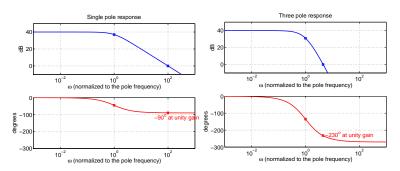

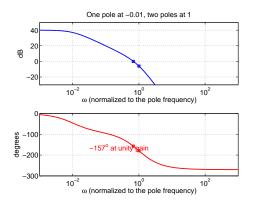

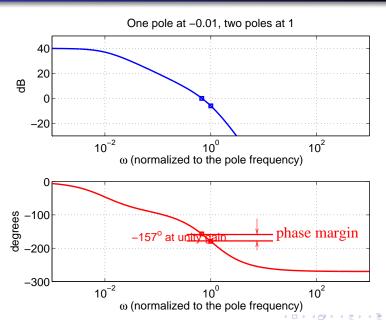

## Single real pole: Bode plot

#### Magnitude:

- Constant for frequencies less than the pole frequency

- Rolloff for frequencies more than the pole frequency

#### Phase:

- Phase change before and after the pole frequency

- $\pi/4 = 45^{\circ}$  lag at the pole frequency

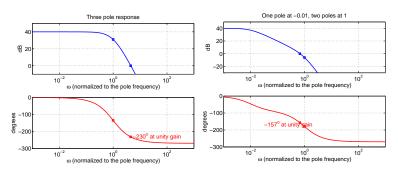

#### Poles close to each other

- With multiple poles close to each other,  $\angle L$  drops off to or below  $-\pi$  before |L| rolls off to unity  $\Rightarrow$  instability

- Risk of instability is worst when the loop gain is high and poles are close to each other

## Poles far from each other

• With one pole at a much lower in frequency compared to others, magnitude rolls off to unity before phase approaches  $-\pi$

## Stable negative feedback systems

- One pole at a low frequency (\*)

- Remaining poles beyond the unity gain frequency

- < 180° phase lag at the unity loop gain frequency</li>

<sup>(\*)</sup> This condition is sufficient, but not necessary

## Have "sufficient phase margin" for stability

# Stability in Negative Feedback Systems

- The loop gain is G(s)H(s)

- Closed loop transfer function is  $\frac{G(s)}{1+G(s)H(s)}$

- For stability, the closed loop poles must be in the Left Half Plane (LHP).

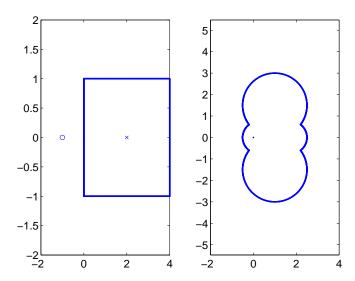

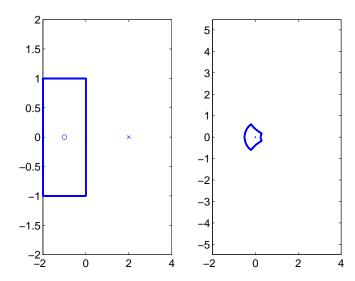

- The Nyquist Criterion : A technique to reliably predict the number of closed loop poles in the RHP from G(s)H(s).

- Consider a function F(s), a ratio of polynomials in s

- Draw a closed contour in the s plane

- The contour must not pass through any singular points

- If the contour in the s-plane encloses **one** pole of F(s), the locus of F(s) encircles the origin of the F(s) plane **once** in the **counterclockwise** direction

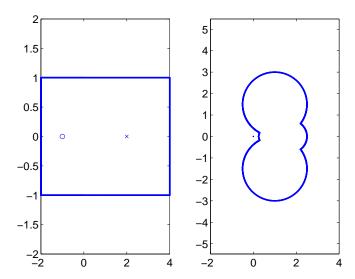

$$F(s) = \frac{s+1}{s-2}$$

• If the contour in the s-plane encloses **one** zero of F(s), the locus of F(s) encircles the origin of the F(s) plane **once** in the **clockwise** direction

$$F(s) = \frac{s+1}{s-2}$$

If the contour in the s-plane encloses one pole and one zero of F(s), the locus of F(s) does not encircle the origin

$$F(s) = \frac{s+1}{s-2}$$

#### Summary: Cauchy's Principle of Argument

• If the contour in the s-plane encloses  $\mathbf{N}$  poles and  $\mathbf{M}$  zeros of F(s), the locus of F(s) encircle the origin  $(\mathbf{N} - \mathbf{M})$  times in the counter-clockwise direction

#### Example

$$F(s) = \frac{s+1}{(s-2)(s-1)}$$

- Want to find if the poles of the closed loop system are in the RHP

- Closed loop poles are the roots of 1 + G(s)H(s) = 0

- In other words, closed loop poles are the zeros of 1 + G(s)H(s)

- In circuit work, the open loop system is always stable

- The poles of the open loop system are the the LHP

- The poles of 1 + G(s)H(s) and G(s)H(s) are the same

- $\Rightarrow$  1 + G(s)H(s) has poles in the LHP

- Apply Cauchy's Principle to F(s) = 1 + G(s)H(s)

- F(s) has poles in the LHP

- Apply Cauchy's Principle to find the location of the zeros of F(s)

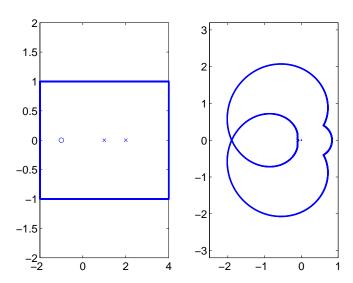

Travel along a countour that encloses the entire RHP

- If F(s) has zeroes in the RHP, there will be encirclements about the origin

- Since F(s) has no poles in the RHP number of encirclements = number of RHP zeros of F(s) = number of RHP poles of the closed loop system

- F(s) encircling the origin is equivalent to G(s)H(s) encircling the point (-1,0)

- Find the number of encirclements of  $G(j\omega)H(j\omega)$  around the point (-1,0)

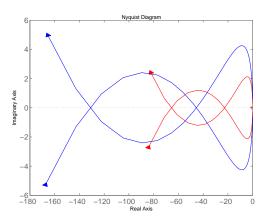

# Nyquist by Example All Pole Systems

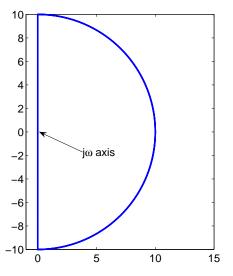

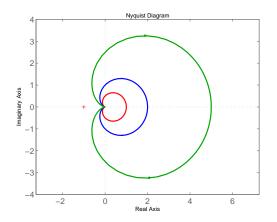

#### First Order System: Unconditionally Stable

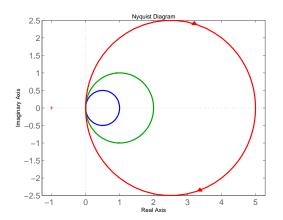

$$G(s)H(s) = \frac{K}{s+1}, K = 1, 2, 5$$

### Second Order System : Unconditionally Stable

$$G(s)H(s)=rac{K}{(s+1)^2},\,K=1,2,5$$

#### Third Order System: Conditionally Stable

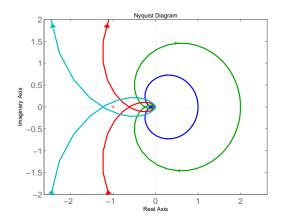

$$G(s)H(s) = \frac{K}{(s+1)^3}$$

,  $K = 1, 2, 5, 10$

#### All-pole Loop Gain Summary

- First & second order systems are unconditionally stable

- Third and higher order systems are conditionally stable

- Magnitude and phase are monotonically decreasing

- ⇒ With a sufficiently large gain, will become unstable

- Example : Third order system becomes unstable for K > 8

- This intuition (wrongly) applied to other systems can cause confusion

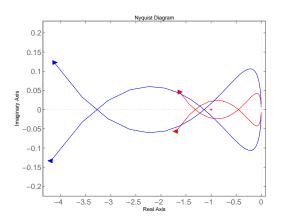

#### Question

The loop gain of a feedback amplifier has a magnitude greater than 1, and a phase lag larger than 180 degrees. Is it possible that the closed loop system is stable?

#### Answer:?

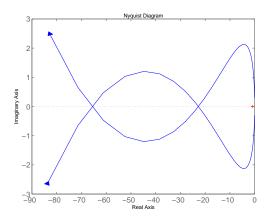

- Example :  $G(s)H(s)=\frac{3s^2+4s+2}{(s+\delta)^3}$ , where  $\delta \to 0$

- Closed loop poles the roots of  $s^3 + 3s^2 + 4s + 2$

- Poles are at -1,  $-1 \pm j$

- Phase lag @ DC is 0°

- Phase lag @ low frequencies is 270°

- Magnitude @ low frequencies >> 1

#### The Nyquist Plot

- Phase crosses 180° twice

- There is **no** encirclement of (-1,0)

- ⇒ There are no RHP poles

- System is stable!

#### Common Misconception I

- Statement :If the magnitude is greater than 0 dB and the phase lag is greater than 180° ⇒ instability

- True only for all pole G(s)H(s)

- Incorrect when the loop gain has zeros

(as demonstrated by the example in the previous slides)

#### Question

I have a feedback system on the verge of instability. I now increase the loop gain by a factor K > 1. The closed loop system becomes nice and stable. Is this possible?

I have a stable feedback system. I now *decrease* the loop gain by a factor K > 1. The closed loop system starts oscillating. Is this possible ?

#### The Nyquist Plot

- Plot for high gain does not encircle (-1,0)

- System is "more" stable!

#### The Nyquist Plot

- Plot for low gain encircles (-1,0) twice

- There are two RHP poles

- System is unstable!

#### Common Misconception II

- Statement : Increasing gain is bad news for stability or reducing loop gain improves stability

- True only for all pole G(s)H(s)

- Incorrect when the loop gain has zeros

(as demonstrated by the examples in the previous slides)

- These "anomalies" can be explained by the Nyquist plot

#### Closing Comments on Stability and Phase Margin

- For stability, the magnitude plot must have a slope of 20 dB per decade around the unity gain frequency.

- There can be any number of poles to the left or right of the unity gain cross over, and the system will be stable as long as these poles are sufficiently far away from the cross over frequency

- The phase margin is a valuable metric to assess stability even in high order systems

- To stabilize a high order system, it must be made to "look" like a first order system at and around its unit gain cross over point

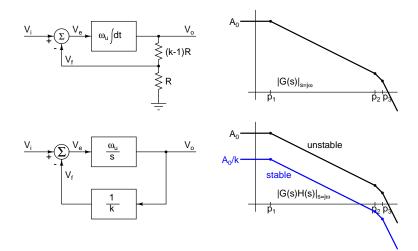

Dominant pole frequency compensation

## Dominant pole frequency compensation

#### Modify the frequency response such that there is

- One pole at a low frequency

- Remaining poles beyond the unity loop gain frequency

- $\omega_{u,loop} \approx (A_o/k)|p_1|$ , where  $p_1$  is the dominant pole

- 20 dB/decade rolloff at unity loop gain

This condition is sufficient, but not necessary

### Two pole example

### Damping factor of $1/\sqrt{2}$

$$\zeta = \frac{1}{2} \sqrt{\frac{k}{A_o}} \left( \sqrt{\frac{p_2}{p_1}} + \sqrt{\frac{p_1}{p_2}} \right) = \frac{1}{\sqrt{2}}$$

$$\zeta \approx \frac{1}{2} \sqrt{\frac{k}{A_o}} \left( \sqrt{\frac{p_2}{p_1}} \right)$$

$$p_2 = 2 \frac{A_o p_1}{k} = 2 \omega_{u,loop}$$

$$\phi_m = 90^\circ - \tan^{-1} \frac{\omega_{u,loop}}{p_2}$$

$$= 63.5^\circ$$

### Two pole example

Phase margin of 60°

$$-90^{\circ} - \tan^{-1} \frac{\omega_{u,loop}}{p_2} = -120^{\circ}$$

$$\frac{\omega_{u,loop}}{p_2} = \frac{1}{\sqrt{3}}$$

$$p_2 = \sqrt{3}\omega_{u,loop}$$

$$\zeta = \frac{\sqrt{\sqrt{3}}}{2}$$

$$= 0.66$$

# Dependence of stability on feedback factor

# Unity gain compensation

- Variable feedback factor: compensate for lowest k

- General purpose opamps: unity gain compensated

- e.g.: LM741, LF356, OPA656

# Why not always compensate for unity gain?

- Sub optimal bandwidth for non unity feedback

- Compensate only for the required feedback factor

far enough from ω<sub>u,loop</sub>

OPA657: compensated for feedback factors ≤ 1/8

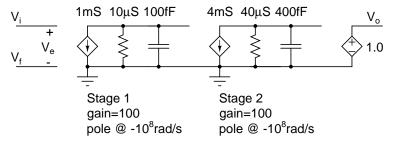

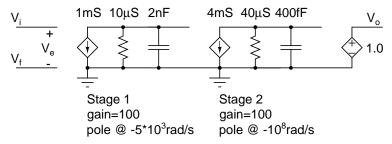

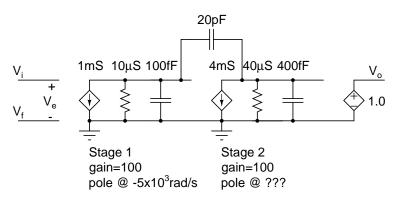

#### Two stage amplifier example

- DC gain  $A_o = 10^4 \, (80 \, \text{dB})$

- Two poles at -10<sup>8</sup> rad/s

- Insufficient phase margin

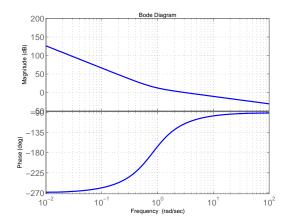

### Dominant pole compensation

- Move one of the poles to  $-5 \times 10^3$  rad/s

- Other pole remains at the original frequency

- Unity gain frequency  $\omega_u = 5 \times 10^7 \, \text{rad/s} = |p_2|/2$

- 2 nF compensation capacitor: too large on an IC

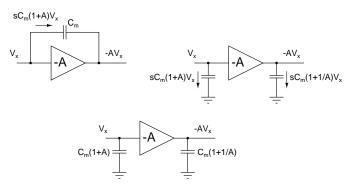

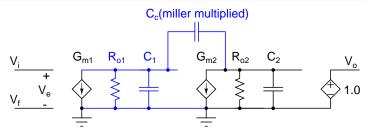

#### Miller effect

(amplifier: ideal voltage controlled voltage source)

• 2 nF can be realized using 20 pF across a gain of 100

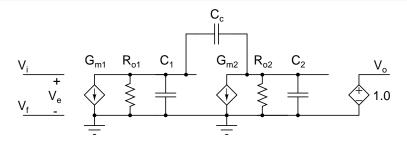

### Miller compensated amplifier

- Dominant pole at  $5 \times 10^3$  rad/s

- Simulated frequency response <u>does not show</u> the second pole at -10<sup>8</sup> rad/s

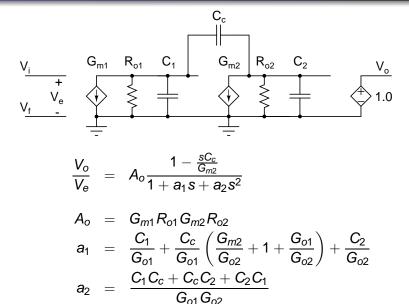

### Miller compensated amplifier-analysis

## Approximate solution to a quadratic equation

$$a_2s^2 + a_1s + 1 = 0$$

$a_1p_1 + 1 \approx 0$

$p_1 \approx -\frac{1}{a_1}$

$a_2p_2^2 + a_1p_1 \approx 0$

$p_2 \approx -\frac{a_1}{a_2}$

• Works for widely separated (real) poles i.e.  $|p_2| \gg |p_1|$

### Miller compensated amplifier-analysis

$$egin{array}{lll} egin{array}{lll} egin{arra$$

## Miller compensated amplifier-analysis

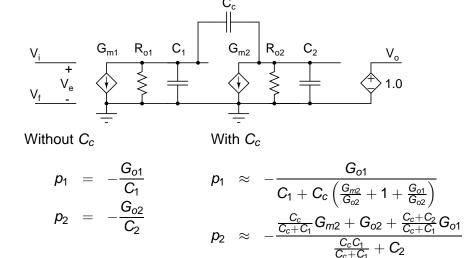

## Miller compensated amplifier: pole splitting

- p<sub>1</sub> moves to a lower frequency

- p<sub>2</sub> moves to a higher frequency

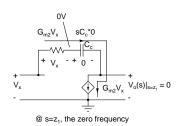

- Right half plane zero  $z_1 = G_{m2}/C_c$ ; additional phase lag; reduced phase margin

- Unity gain frequency has to be lower than the modified p<sub>2</sub>

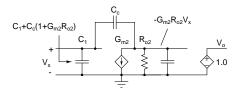

#### Intuitive explanation

- Input capacitance increased due to miller multiplication

- Output conductance increased due to feedback around  $G_{m2}$

#### Intuitive explanation

1st stage output pole p<sub>1</sub> ~ -1/[R<sub>o1</sub>(C<sub>1</sub>+C<sub>c</sub>(1+G<sub>m2</sub>R<sub>o1</sub>))]

$2^{\text{nd}} \text{ stage output pole p}_2 \sim -[G_{\text{m2}}(C_{\text{c}}/(C_1 + C_{\text{c}}) + G_{\text{o2}}]/[C_2 + C_{\text{c}}C_1/(C_{\text{c}} + C_1)]$

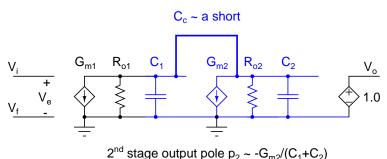

### Output pole frequency

- 2 stage output pole  $p_2 \sim -G_{m2}/(C_1+C_2)$

- Crude approximation:  $p_2 \approx G_{m2}/(C_1 + C_2)$

- Works when  $C_c \gg C_1$

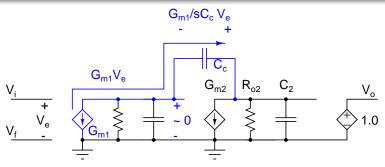

## Unity gain frequency

If one pole is dominant

$$\begin{array}{lcl} \omega_{u} & \approx & A_{o}|p_{1}| \\ & = & G_{m1}R_{o1}G_{m2}R_{o2}\frac{G_{o1}}{C_{1} + C_{c}\left(\frac{G_{m2}}{G_{o2}} + 1 + \frac{G_{o1}}{G_{o2}}\right)} \\ & = & \frac{G_{m1}}{C_{c}\left(1 + \frac{G_{o2}}{G_{m2}} + \frac{G_{o1}}{G_{m2}}\right) + C_{1}\frac{G_{o2}}{G_{m2}}} \approx \frac{G_{m1}}{C_{c}} \end{array}$$

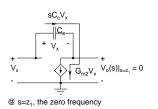

### Right half plane zero

- Zero at G<sub>m2</sub>/C<sub>c</sub>

- Zero moves to  $\infty$  for  $R_c = 1/G_{m2}$

### Tuning the zero

$$\frac{V_o(s)}{V_e(s)} = A_o \frac{1 - sC_c \left(R_f - \frac{1}{G_{m2}}\right)}{D_3(s)}$$

- $\bullet$  Zero can be moved to  $\infty$  or to LHP to cancel a non dominant pole

- Third order system-extra pole

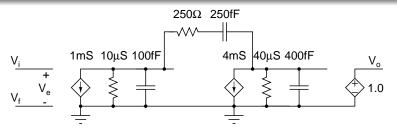

#### Calculations

$$egin{array}{lcl} rac{G_{m1}}{C_c} & = & rac{1}{2} G_{m2} C_1 + C_2 \\ C_c & = & 250 \, \mathrm{fF} \\ \omega_u & = & rac{G_{m1}}{C_c} = 4 \, \mathrm{Grad/s} \\ |p_2| & = & rac{G_{m2}}{C_1 + C_2} = 8 \, \mathrm{Grad/s} \end{array}$$

- $C_c \gg C_1$  is not valid

- Refine the values using exact calculations/simulations

- Use  $R_f = 1/G_{m2} = 250 \Omega$  to cancel the RHP zero

#### Calculations

|                  | with $R_c$             | w/o R <sub>c</sub>    |           |

|------------------|------------------------|-----------------------|-----------|

| DC gain          | 10 <sup>4</sup>        |                       |           |

| Poles            | $-3.92 \times 10^{5}$  | $-3.92 \times 10^{5}$ | rad/s     |

|                  | $-6.88 \times 10^{9}$  | $-6.19 \times 10^{9}$ | rad/s     |

|                  | $-5.93 \times 10^{10}$ |                       | rad/s     |

| Zeros            | $\infty$               | $+1.6 \times 10^{10}$ | rad/s     |

| $\omega_{u}$     | $3.49 \times 10^{10}$  | $3.49 \times 10^{10}$ | rad/s     |

| Phase margin     | 60°                    | 48°                   |           |

| (unity feedback) |                        | 40044004              | E 1 4 E 1 |

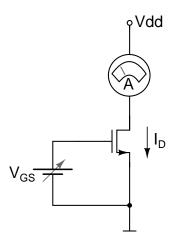

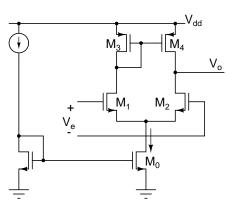

# Negative Feedback for Bias Stabilization

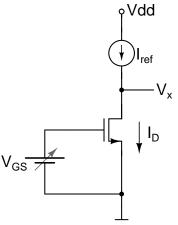

The Bias Stabilization Problem Determine the  $V_{GS}$  that I should apply to a MOS transistor (operating in saturation) so that the drain current  $I_D = I_{ref}$ .

#### Bias Stabilization

- ... involves the following tasks ....

- Measure the quiescent current

- Compare it with a reference current

- **Kick** the *V<sub>GS</sub>* in the right direction

- ... ok, so how many ways can we do this?

- In a MOSFET, I<sub>D</sub> = I<sub>S</sub> ⇒ can measure quiescent current in two ways.

- Varying V<sub>GS</sub> ⇒ can be done in atleast two ways : keep V<sub>S</sub> fixed & vary V<sub>G</sub>, or viceversa.

- ... atleast four ways of stabilizing bias current.

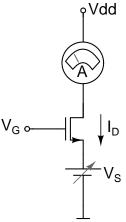

#### Basic Idea

Think: What will I do in a lab?

- Apply an arbitrary gate-source voltage.

- Measure I<sub>D</sub> using an ammeter.

- Compare  $I_D$  with  $I_{ref}$ .

- If I<sub>D</sub> > I<sub>ref</sub>, the applied V<sub>GS</sub> is too high, reduce it.

- If I<sub>D</sub> < I<sub>ref</sub>, the applied V<sub>GS</sub> is too low, increase it.

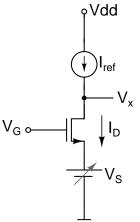

#### Comparing Currents Without an Ammeter

- Monitor  $V_x$ .

- If  $V_x$  increases with time, means  $I_{ref} > I_D$ .

- If V<sub>x</sub> decreases with time, means I<sub>ref</sub> < I<sub>D</sub>.

- If I<sub>D</sub> > I<sub>ref</sub>, or equivalently, if V<sub>x</sub> decreases ⇒ the applied V<sub>GS</sub> is too high, reduce it.

- If I<sub>D</sub> < I<sub>ref</sub>, or equivalently, if V<sub>X</sub> increases ⇒ the applied V<sub>GS</sub> is too low, increase it.

- The simple "diode-connected" transistor is a negative feedback system in disguise!

- Drain current is measured, and the V<sub>GS</sub> is changed by keeping V<sub>S</sub> fixed and varying V<sub>G</sub>.

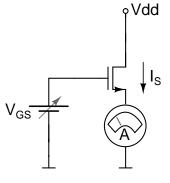

#### Measuring Current in the Source

- Apply an arbitrary gate-source voltage.

- Measure I<sub>S</sub> using an ammeter.

- Compare  $I_S$  with  $I_{ref}$ .

- If I<sub>S</sub> > I<sub>ref</sub>, the applied V<sub>GS</sub> is too high, reduce it.

- If I<sub>S</sub> < I<sub>ref</sub>, the applied V<sub>GS</sub> is too low, increase it.

#### Comparing Currents Without an Ammeter

- Monitor  $V_x$ .

- If V<sub>x</sub> increases with time, means I<sub>S</sub> > I<sub>ref</sub>.

- If V<sub>x</sub> decreases with time, means I<sub>S</sub> < I<sub>ref</sub>.

- If I<sub>S</sub> > I<sub>ref</sub>, or equivalently, if V<sub>x</sub> increases ⇒ the applied V<sub>GS</sub> is too high, reduce it.

- If  $I_S < I_{ref}$ , or equivalently, if  $V_X$  decreases  $\Rightarrow$  the applied  $V_{GS}$  is too low, increase it.

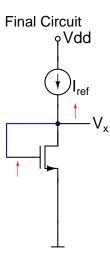

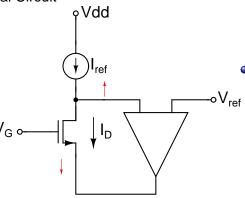

# Final Circuit

Source current is measured, and the V<sub>GS</sub> is changed by keeping V<sub>G</sub> fixed and varying V<sub>S</sub>.

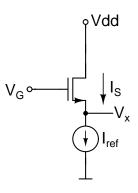

#### Bias Stabilization : Measure $I_D$ & Vary $V_S$

- Keep V<sub>G</sub> fixed, apply an arbitrary source voltage.

- Measure I<sub>D</sub> using an ammeter.

- Compare  $I_D$  with  $I_{ref}$ .

- If I<sub>D</sub> > I<sub>ref</sub>, the applied V<sub>GS</sub> is too high, increase V<sub>S</sub>.

- If I<sub>D</sub> < I<sub>ref</sub>, the applied V<sub>GS</sub> is too low, decrease V<sub>S</sub>.

#### Comparing Currents Without an Ammeter

- Monitor  $V_x$ .

- If  $V_x$  increases with time, means  $I_{ref} > I_D$ .

- If V<sub>x</sub> decreases with time, means I<sub>ref</sub> < I<sub>D</sub>.

- If  $I_D < I_{ref}$ , or equivalently, if  $V_x$  increases  $\Rightarrow$  the applied  $V_{GS}$  is too high, increase  $V_S$ .

- If I<sub>D</sub> > I<sub>ref</sub>, or equivalently, if V<sub>X</sub> decreases ⇒ the applied V<sub>GS</sub> is too low, decrease V<sub>S</sub>.

Drain current is measured, and the  $V_{GS}$  is changed by keeping  $V_{G}$  fixed and varying  $V_{S}$ .

# **Final Circuit** ∘ Vdd $I_{ref}$ Opamp signs come out automatically.

# Negative Feedback in Single Transistor Circuits

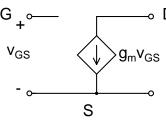

#### The Incremental MOSFET Equivalent Circuit

- A MOSFET biased in saturation is an incremental voltage controlled current source

- In principle,  $g_m$  can be made as large as one wants

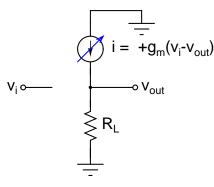

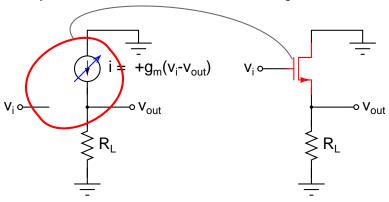

#### Making an Incremental VCVS with Gain=1

How do you make a VCVS when all you have is a variable current source?

- Want  $v_{out} = v_i$

- Measure v<sub>out</sub>

- Compare it to v<sub>i</sub>

- If v<sub>out</sub> < v<sub>i</sub>, pump currentinto v<sub>out</sub>

- If v<sub>out</sub> > v<sub>i</sub>, pump current

out of v<sub>out</sub>

- The current source is controlled by (v<sub>i</sub> - v<sub>out</sub>)

#### Identify the Transistor → Common Drain Stage

If

$$g_m \to \infty$$

,  $v_{out} = v_i$ ,  $R_{out} = 0$

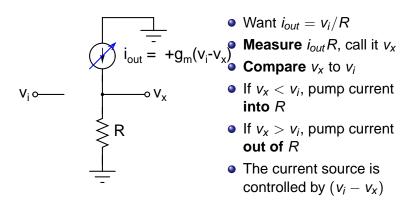

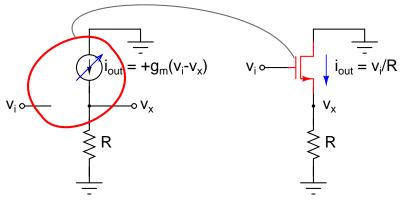

#### Make a VCCS with Transconductance of 1/R

How do you make a VCCS when all you have is a variable current source?

#### $Identify \ the \ Transistor \rightarrow Transconductance \ Stage$

If

$$g_m \to \infty$$

,  $i_{out} = v_i/R$

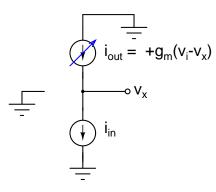

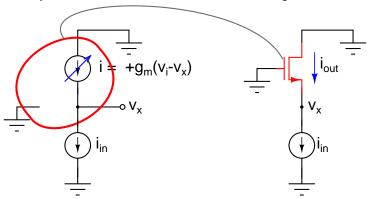

#### Make a CCCS with gain of 1

How do you make a CCCS when all you have is a variable current source ?

- Want  $i_{out} = i_{in}$

- Measure potential v<sub>x</sub>

- Compare  $v_x$  to 0

- If v<sub>x</sub> < 0, i<sub>out</sub> is too small, increase i<sub>out</sub>

- If  $v_x > 0$ ,  $i_{out}$  is too big, decrease  $i_{out}$ .

- The current source is controlled by (0 – v<sub>x</sub>)

#### Identify the Transistor → Common Gate Stage

If

$$g_m \to \infty$$

,  $i_{out} = v_i/R$

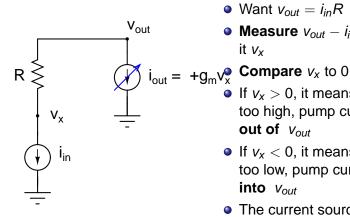

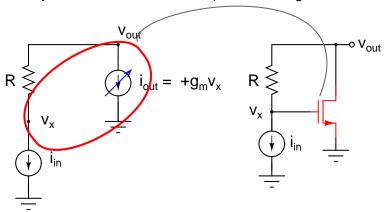

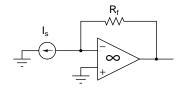

#### Make a CCVS with transimpedance R

How do you make a CCVS when all you have is a variable current source?

- Want  $v_{out} = i_{in}R$

- Measure  $v_{out} i_{in}R$ , call it V<sub>Y</sub>

- If  $v_x > 0$ , it means  $v_{out}$  is too high, pump current out of  $V_{OUT}$

- If  $v_x < 0$ , it means  $v_{out}$  is too low, pump current into *v<sub>out</sub>*

- The current source is controlled by  $v_x$

#### Identify the Transistor → Transimpedance Stage

If

$$g_m \to \infty$$

,  $v_{out} = i_{in}R$

# **CMOS** implementations

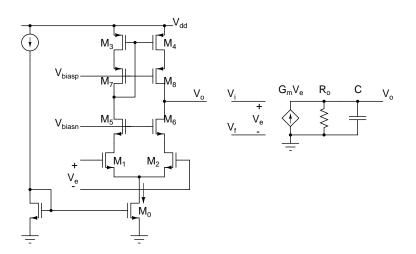

# Negative feedback amplifier: Realization

## **Buffers in CMOS**

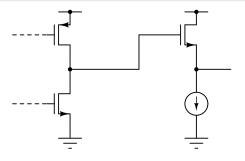

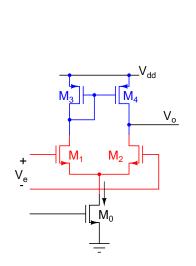

## Single stage opamp

$$\mathsf{M}_1 = \mathsf{M}_2$$

$$\mathsf{M}_3 = \mathsf{M}_4$$

- $R_0 = r_{ds1} || r_{ds3} || R_L$

- $C = C_{p,out} + C_L$

•

$$g_m = g_{m1}$$

•

$$A_o = g_{m1}R_o$$

# Single stage opamp

$$rac{I_{out}(s)}{V_{e}(s)} = g_{m1} rac{1 + s rac{C_3}{2g_{m3}}}{1 + s rac{C_3}{g_{m3}}}$$

Pole zero pair due to two paths

# Single stage opamp-summary

| dc gain A <sub>o</sub>          | $g_{m1}/(g_{d\mathrm{s}1}+g_{d\mathrm{s}3})$ |

|---------------------------------|----------------------------------------------|

| Unity gain frequency $\omega_u$ | $g_{m1}/(C_L+C_o)$                           |

| Additional poles/zeros          | $p_2 = -g_{m3}/C_3$                          |

|                                 | $z_1=-2g_{m3}/C_3$                           |

- ullet  $A_o \sim g_m/g_{ds}$

- Increase dc gain by increasing L

- A<sub>o</sub> limited to about 100

- Increase phase margin by increasing C<sub>L</sub>

- Not preferred with resistive loads

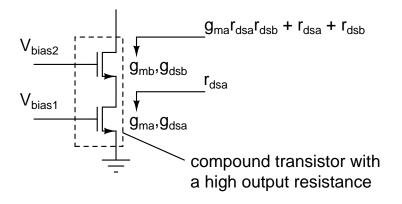

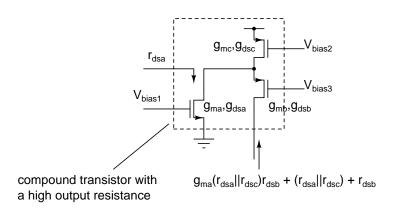

#### Cascode transistor

# Telescopic cascode opamp

# Telescopic cascode opamp

# Telescopic cascode opamp-summary

$$A_o pprox rac{g_{m1}}{g_{ds1}g_{ds5}/g_{m5}+g_{ds3}g_{ds7}/g_{m7}} \ \omega_u = g_{m1}/(C_L+C_o) \ p_2 = -g_{m3}/C_3 \ z_1 = -2g_{m3}/C_3 \ p_{3-6} \sim g_{mx}/C_{px}$$

- $\bullet \ \ \mathsf{A}_o \sim (g_m/g_{ds})^2$

- $A_o \sim 10^4$  possible

- Increase phase margin by increasing C<sub>L</sub>

- Not preferred with resistive loads

# Folded cascode stage

# Folded cascode opamp

# Folded cascode opamp

# Folded cascode opamp-summary

$$egin{array}{lcl} A_o &pprox & rac{g_{m1}}{(g_{ds1}+g_{ds9})g_{ds5}/g_{m5}+g_{ds3}g_{ds7}/g_{m7}} \ \omega_u &=& g_{m1}/(C_L+C_o) \ p_2 &=& -g_{m3}/C_3 \ z_1 &=& -2g_{m3}/C_3 \ p_{3-6} &\sim& g_{mx}/C_{px} \end{array}$$

- $\bullet \ \ \mathsf{A}_o \sim (g_m/g_{ds})^2$

- $A_o \sim 10^4$  possible

- Increase phase margin by increasing C<sub>L</sub>

- Not preferred with resistive loads

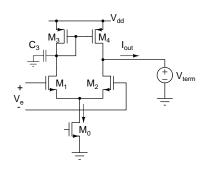

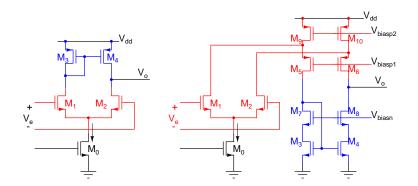

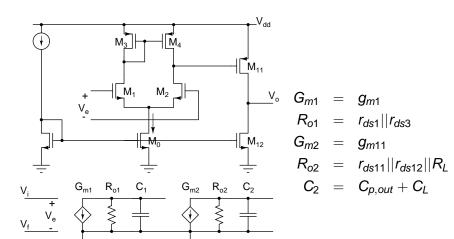

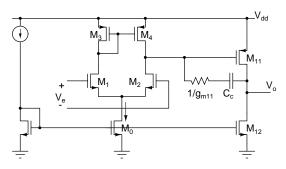

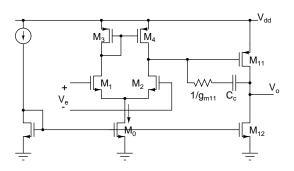

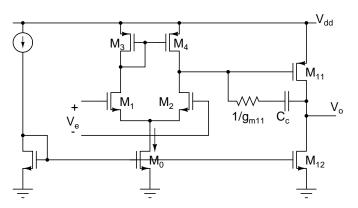

## Two stage opamp

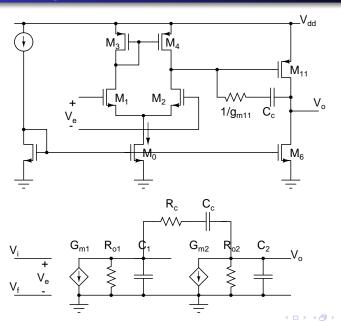

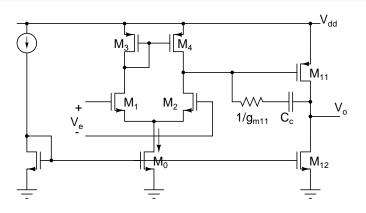

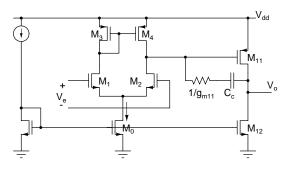

# Two stage opamp with compensation

# Two stage opamp with compensation

## Two stage opamp design for a given $C_L$ , $\omega_u$

- Choose  $g_{m11}$  such that  $g_{m11}/C_L > \omega_u$  (say 2.5 $\omega_u$ )

- Choose  $g_{m1}$  and  $C_c$  such that  $g_{m1}/C_c=\omega_u$

- Scale down g<sub>m1</sub> and C<sub>c</sub> until specs deteriorate (phase margin, noise)

- Iterate with a different value of  $g_{m11}$  to reach an optimum

## Two stage opamp design for a given $R_L$ , $C_L$ , $\omega_u$

- Constraints for  $g_{m11}$

- $g_{m11}/C_L > \omega_u \text{ (say 2.5}\omega_u\text{)}$

- $g_{m11}R_L$  enough to reduce the first stage swing

- Choose  $g_{m1}$  and  $C_c$  such that  $g_{m1}/C_c = \omega_u$

- Scale down  $g_{m1}$  and  $C_c$  until specs deteriorate

- Iterate with a different value of  $g_{m11}$  to reach an optimum

## Two stage opamp design for an internal load and $\omega_u$

- Assume an internal load (e.g. an identical stage)

- Choose  $g_{m11}$  such that  $g_{m11}/C_L > \omega_u$  (say 2.5 $\omega_u$ )

- Choose  $g_{m1}$  and  $C_c$  such that  $g_{m1}/C_c=\omega_u$

- Scale down stages until specs deteriorate

## Two stage opamp design-obtaining dc gain

- Second stage  $\sim$  min. length, esp. with heavy loads

- Optimize first stage for dc gain  $(L_{MOS})$

## Two stage opamp design-increasing dc gain

- Use a telescopic cascode first stage

- ullet  $A_o \sim (g_m/g_{ds})^3$

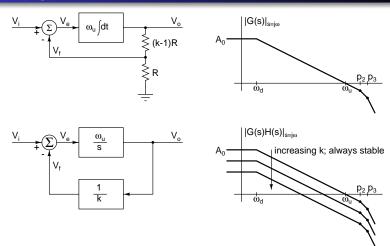

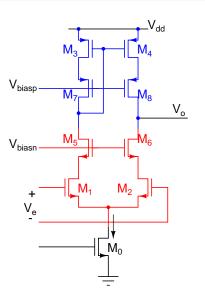

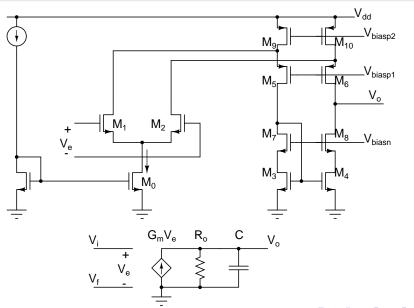

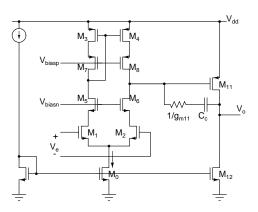

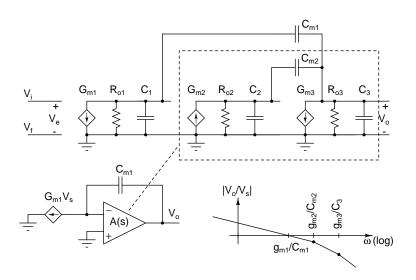

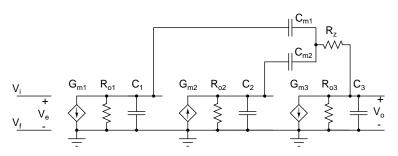

## Three stage opamp

$$\frac{V_o(s)}{V_i(s)} = \frac{G(s)}{1 + G(s)H(s)} \\

= \frac{1}{H(s)} \frac{G(s)H(s)}{1 + G(s)H(s)} \\

= \frac{1}{H(s)} \frac{1}{1 + \frac{1}{G(s)H(s)}}$$

$$\frac{V_o(s)}{V_i(s)} = \frac{G(s)H(s)}{1 + G(s)H(s)}

= (1)\frac{G(s)H(s)}{1 + G(s)H(s)}

= (1)\frac{1}{1 + \frac{1}{G(s)H(s)}}$$

$\overline{\omega}$  (log)

poles at p2, p3

$p_3$

$\sqrt{\omega}$  (log)

$\omega$  (log)

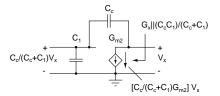

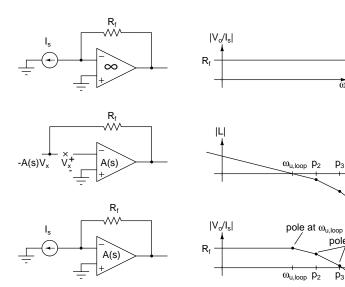

#### Three stages in cascade

## Frequency response of compensated last two stages

## Three stage opamp equivalent circuit

#### Three stage opamp

#### RHP zero cancellation

- Has two zeros

- Approximate cancellation

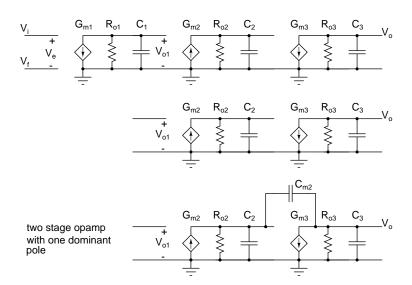

## Three stage opamp design for a given $C_L$ , $\omega_u$

$$\frac{G_{m3}}{C_L} > \omega_u$$

Compensate the last two stages using C<sub>m2</sub>

$$\frac{G_{m3}}{C_L} > \frac{G_{m2}}{C_{m2}}$$

;  $\frac{G_{m2}}{C_{m2}} > \omega_u$

Compensate the opamp using C<sub>m1</sub>

$$\frac{G_{m1}}{C_{m1}} = \omega_u$$

- Scale down  $G_{m1}$  and  $C_{m1}$  within constraints (noise, phase margin)

- Scale down  $G_{m2}$  and  $C_{m2}$  within constraints (phase margin)

## Three stage opamp design for a given $R_L$ , $C_L$ , $\omega_u$

$$\frac{G_{m3}}{C_L} > \omega_u$$

$G_{m3}R_L \sim 5$

- $G_{m3}R_L$  sufficiently high to reduce internal swing

- Remaining steps as before

#### Three stage opamp design

- Analytical expression very complicated—approximate

- Use above approximation as the starting point

- More optimization through simulation

- Scale down G<sub>m</sub>, C until constrained

- Complex zeros may be better

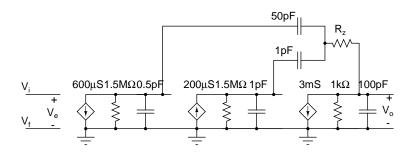

| <b>Specifications</b> |

|-----------------------|

|-----------------------|

| <b>Opcomodició</b> |                          |  |  |

|--------------------|--------------------------|--|--|

| $A_o$              | 100 dB                   |  |  |

| $\omega_{m{u}}$    | 1.75 MHz                 |  |  |

| $R_L$              | 1 kΩ                     |  |  |

| $C_L$              | 100 pF                   |  |  |

| Input ref. noise   | 3 μV rms (100 Hz-24 kHz) |  |  |

| Output swing       | $1.5 V_{ppd}^2$          |  |  |

| $V_{dd}$           | 1.8 V                    |  |  |

| Technology         | 0.18 $\mu$ m CMOS        |  |  |

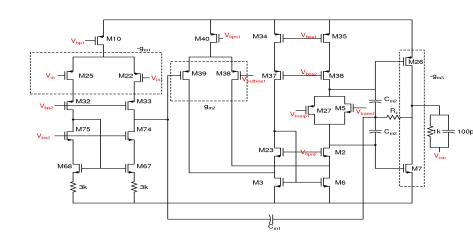

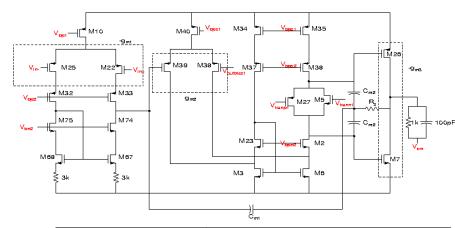

| First-stage                                                                           | Second-stage                                                                                                                      |                                                                     |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| M10: 200(1μ/1μ)<br>M22, M25, M32, M33: 100(1μ/1μ)<br>M75, M74, M68, M67: 100(1.2μ/1μ) | M40 : 300(.5μ/0.25μ) M38, M39 : 20(1μ/1μ) M34, M35, M37, M38 : 80(0.5μ/.25μ) M23, M2 : 20(0.24μ/0.18μ) M79, M62 : 72(0.24μ/0.18μ) | M5, M27: 0.45µ/0.18µ<br>M7: 30(0.24µ/0.18µ)<br>M26: 72(0.24µ/0.18µ) |

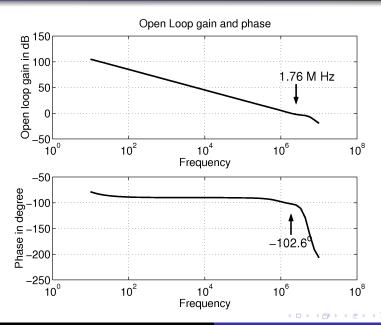

| Specification                 | Value                                        |

|-------------------------------|----------------------------------------------|

| Supply                        | 1.8 V (±5%)                                  |

| Loading Condition             | $100 \text{ pF} // 1 \text{ k}\Omega$        |

| Technology                    | $0.18$ - $\mu \mathrm{m} \ \mathrm{CMOS}$    |

| DC-gain                       | 105 dB                                       |

| Phase Margin                  | $77.4^{o}$                                   |

| UGF(MHz)                      | 1.76                                         |

| Output Swing                  | $0.2 \le V_{out} \le 1.6$                    |

| Slew Rate                     | $\pm 1 \text{ V/}\mu s$                      |

| THD @ 1 kHz input             | -96.65 dB                                    |

| $C_{m1}$                      | 50 pF                                        |

| $C_{m2}$                      | 1 pF                                         |

| $Power(\mu W)$                | $349 \ \mu W$                                |

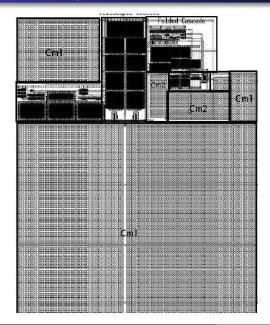

| Total Area                    | $237 \times 297 \ \mu m^2 \ (70389 \mu m^2)$ |

| Operational Amplifier Area    | $10109 \mu m^2$                              |

| Compensation Capacitance Area | $60280 \mu m^2$                              |

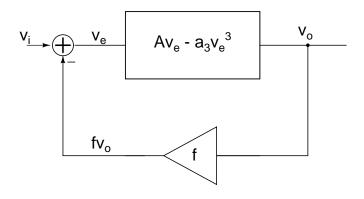

# Amplifier Nonlinearity in Negative Feedback Systems

#### Nonlinearity in the Forward Amplifier

- Transistor stages are used to realize high gain Transistors are nonlinear ⇒ The forward amplifier is nonlinear

- Assume fully differential operation ⇒ only odd order nonlinearity

- Assume weak nonlinearity

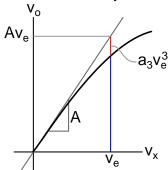

- The transfer curve is approximated as  $v_{out} = Av_x a_3v_y^3$

- Weak nonlinearity  $\Rightarrow Av_x >> a_3v_x^3$

#### Weak Nonlinearity

Difference between the output of a linear amplifier with slope A and the nonlinear amplifier is relatively small

#### What does nonlinearity do to Amplifiers?

- The transfer curve is  $v_{out} = Av_x a_3v_x^3$

- Assume the amplifier is excited with input  $V_{max} \sin(\omega t)$

- $v_{out} pprox AV_{max} \sin(\omega t) rac{a_3}{4} V_{max}^3 \sin(3\omega t)$

- $HD_3 \approx \frac{a_3}{4A} V_{max}^2$

- What happens to distortion when this amplifier is embedded in a feedback loop?

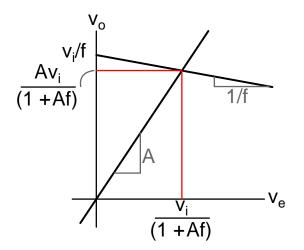

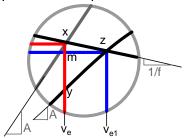

#### Nonlinear Forward Amplifier

What is  $v_o$  versus  $v_i$ ?

Motivation : A picture is worth a thousand equations

x : output of system with linear amp

z : output of system with nonlinear amp

- $v_e = \frac{v_i}{1 + Af}$

- x : (v<sub>e</sub>, Av<sub>e</sub>)

- y:  $(v_e, Av_e a_3v_e^3)$

- Assumption : Slope of the curve is A

x : output of system with linear amp

z: output of system with nonlinear amp

•

$$xy = xm + my = a_3 v_e^3$$

•

$$xm = (v_{e1} - v_e)/f$$

• my =

$$A(v_{e1} - v_e)$$

•

$$(v_{e1} - v_e)(\frac{1}{f} + A) = a_3 v_e^3$$

•

$$v_0 = Av_e - xm = Av_e - (v_{e1} - v_e)/f$$

x: output of system with linear amp

z : output of system with nonlinear amp

•

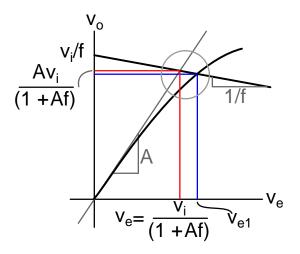

$$(v_{e1} - v_e)(\frac{1}{f} + A) = a_3 v_e^3$$

•

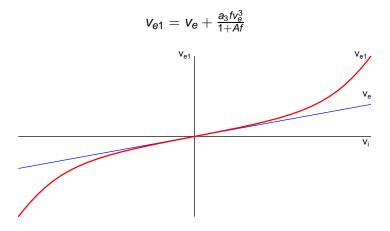

$$V_{e1} = V_e + \frac{a_3 f v_e^3}{1 + A f}$$

•

$$v_0 = Av_e - xm = Av_e - \frac{a_3v_e^3}{(1+Af)}$$

#### Graphical Technique: The Nonlinear Case

- $V_{e} = \frac{V_{i}}{1 + Af}$   $V_{o} = V_{i} \frac{1}{f} \frac{Af}{1 + Af} \frac{a_{3}V_{i}^{3}}{(1 + Af)^{4}}$

x : output of system with linear amp

z : output of system with nonlinear amp

#### Nonlinear Forward Amplifier

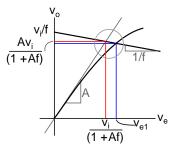

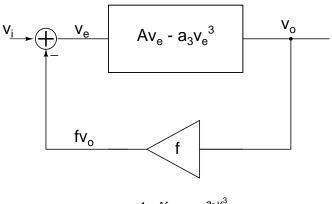

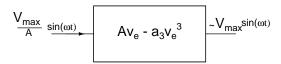

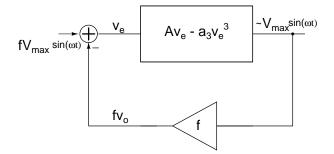

$v_0 = v_i \frac{1}{f} \frac{Af}{1+Af} - \frac{a_3 v_i^3}{(1+Af)^4}$ Why does this make sense?

#### Which System has more Output Distortion?

### System A: Open Loop

$$\frac{V_{\text{max}}}{A} \xrightarrow{\sin(\omega t)} AV_{\text{e}} - a_3 V_{\text{e}}^3 \qquad \frac{V_{\text{max}} \sin(\omega t)}{\Delta V_{\text{max}} \sin(\omega t)}$$

Third Harmonic =

$$\frac{a_3}{4} \left( \frac{V_{max}}{A} \right)^3$$

#### System B: Closed Loop

Third Harmonic =

$$\frac{a_3}{4(1+Af)^4} (fV_{max})^3$$

$\approx \frac{a_3}{4} \left(\frac{V_{max}}{A}\right)^3 \frac{1}{Af}$

System with negative feedback better by a factor of loop gain! Why?

#### $v_{e1}$ versus $v_i$

#### Distorion Reduction: Summary

- Negative feedback reduces distortion

- The input to the forward amplifier is very small

- The error v<sub>e</sub> is predistorted

- This results in a distortion reduction by an extra factor of the loop gain, when compared to the openloop forward amplifier excited by a sinusoid with a small amplitude of the order of v<sub>e</sub>

- Draw a picture! : gives you more insight and understanding

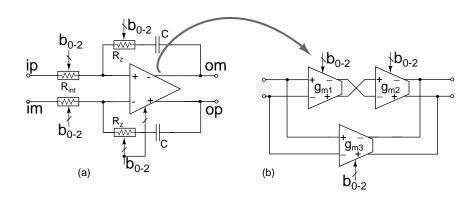

## CASE STUDY

### A 7X Programmable 5<sup>th</sup> Order Active-RC Filter Design Targets

- VHF Active Filter

- Bandwidth programmable over a 7X range (from 44-300 MHz)

- 0.18μm CMOS process, 1.8 V supply

- Frequency response, dynamic range must be maintained over the entire programming range

- As low power as possible

### Why Active-RC?

- Low excess noise of the integrators

- High swing possibilities

- Low distortion

- Parasitic insensitive

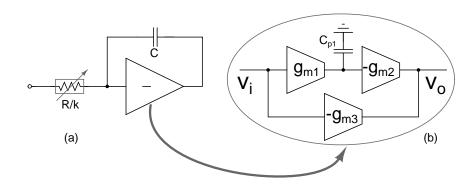

#### Programmable Integrator

#### Programmable Integrator

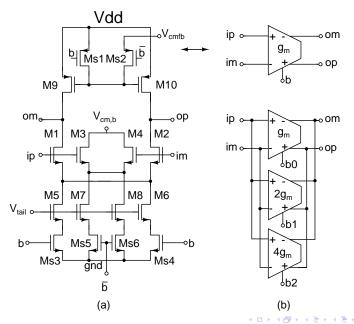

#### Unit Transconductor

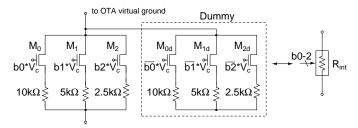

### Digitally Programmable Integrating Resistor

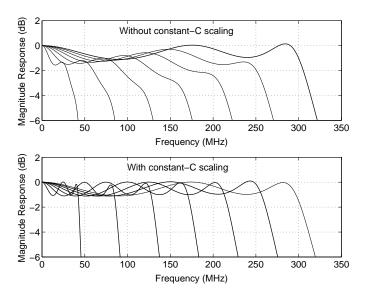

### Benefits of Constant-C Scaling

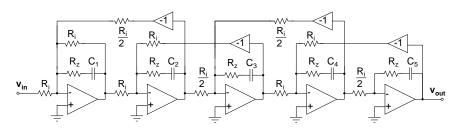

#### Single-ended Filter Schematic

${\rm R_{i}}\text{=}1666.67~\Omega,\,{\rm R_{z}}\text{=}145~\Omega,\,{\rm C_{1}}\text{=}339.76~{\rm fF},\,{\rm C_{2}}\text{=}919.3~{\rm fF},\,{\rm C_{3}}\text{=}634.51~{\rm fF},\,{\rm C_{4}}\text{=}1012.5~{\rm fF},\,{\rm C_{5}}\text{=}530.05~{\rm fF}$

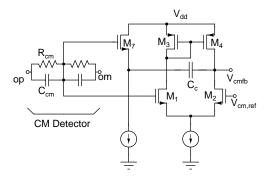

#### Common-mode Feedback

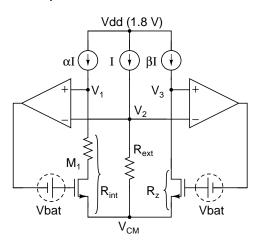

#### Resistor Servo Loop

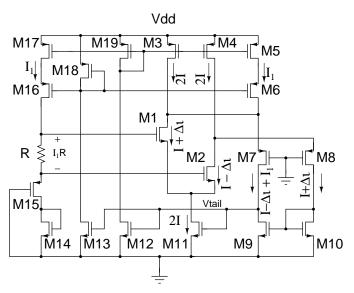

#### **Fixed Transconductance Bias**

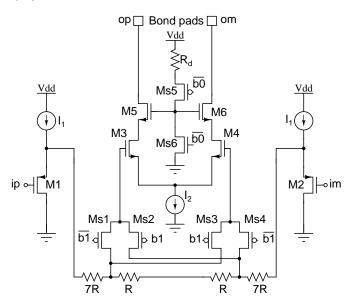

#### Test Buffer

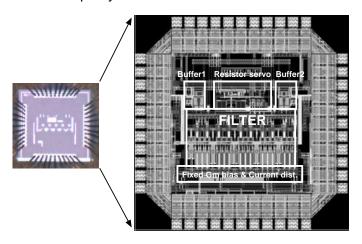

#### Die Photo & Chip Layout

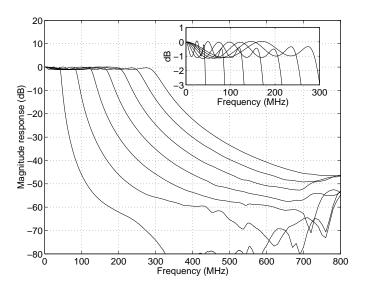

#### Measured Frequency Response

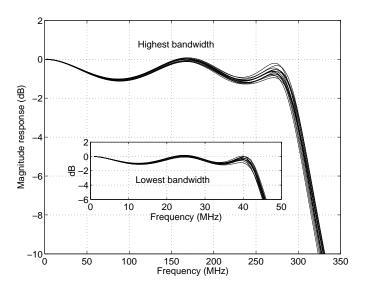

#### Response of Ten Chips

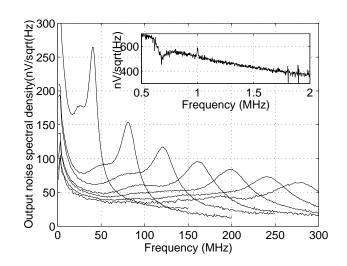

#### Noise Spectral Density with Bandwidth Setting

### Performance Summary

#### Table: SUMMARY OF MEASUREMENT RESULTS

| Technology                                     | $0.18\mu\mathrm{m}$ CMOS                  |

|------------------------------------------------|-------------------------------------------|

| Filter type                                    | 5 <sup>th</sup> order Chebyshev, Opamp-RC |

| Supply voltage                                 | 1.8 V                                     |

| 3 dB bandwidth                                 | 44-300 MHz                                |

| Active chip area                               | $0.63\mathrm{mm}^2$                       |

| Power                                          | 54 mW                                     |

| Integrated output noise                        | 860 $\mu$ V rms                           |

| IIP <sub>3</sub> at band-edge                  | 2.5 V rms                                 |

| Test tone at $\frac{f_{-1dB}}{3}$              |                                           |

| V <sub>in,pp</sub> differential for THD≤-40 dB | 2.2 V                                     |

| Dynamic range for THD=-40 dB                   | 56.6 dB                                   |

# Lead lag compensation

### Opamp models

finite dc gain model: A<sub>0</sub> first order model:  $A_0/(1+s/\omega_d)$ integrator model: ω<sub>u</sub>/s full model:  $A_0/(1+s/\omega_d)(1+s/p_2)(1+s/p_3)$  ...  $\dot{\omega}_{\mathsf{d}}$

- DC performance: Finite dc gain, constant with frequency

- First order estimate of high frequency effects: Integrator

- More detailed high frequency effects: Integrator+pole (s)

- Simulations: Everything

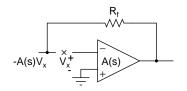

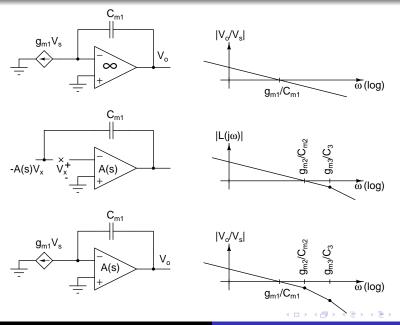

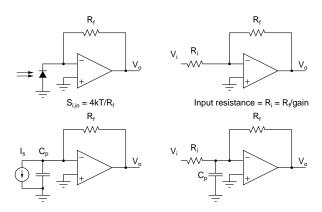

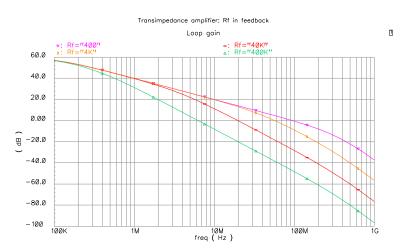

## Negative feedback amplifier design

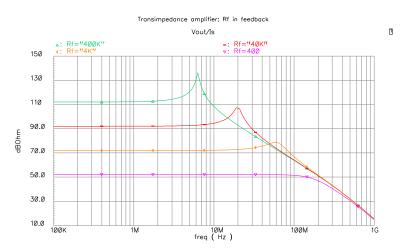

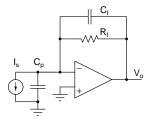

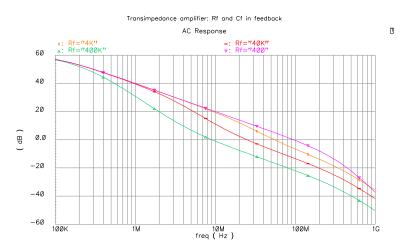

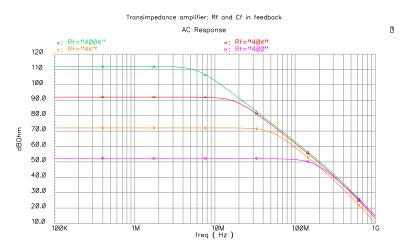

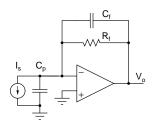

$$L(s) = A(s) \frac{1}{1 + sC_fR_f}$$

$L(s) = A(s) \frac{R_i}{R_i + R_f} \frac{1}{1 + sC_f(R_f||R_i)}$

Extra pole due to the feedback network

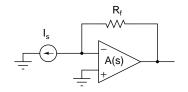

Given  $R_f$  and  $C_d$

$$rac{V_o}{I_s} = rac{R_f}{s^2 \omega_u C_d R_f + s/\omega_u + 1}$$

$\zeta = rac{1}{2\sqrt{C_d R_f \omega_u}} = rac{1}{\sqrt{2}}$

Set the damping factor to  $1/\sqrt{2}$  to obtain a Butterworth response.

$$\omega_{u} = \frac{1}{2C_{d}R_{f}}$$

$$\omega_{-3dB} = \frac{1}{2\sqrt{2}\pi C_{d}R_{f}}$$

- Bandwidth depends on  $C_d$ ,  $R_f$ , independent of  $\omega_u$

- Equivalently,  $R_f$  is fixed, given  $\omega_u$  and  $C_d$ ; can't be increased

Given  $R_f$  and  $C_d$

$$egin{array}{ll} rac{V_o}{I_s} &=& rac{R_f}{s^2 \omega_u C_d R_f + s/\omega_u + s C_f R_f + 1} \ \zeta &=& rac{1 + \omega_u C_f R_f}{2 \sqrt{\omega_u C_d R_f}} \end{array}$$

Set the damping factor to  $1/\sqrt{2}$  to obtain a Butterworth response.

$$C_f = \frac{1}{R_f} \sqrt{2 \frac{C_d R_f}{\omega_u} - \frac{1}{\omega_u^2}}$$

$$\omega_{-3dB} = \frac{1}{2\pi} \sqrt{\frac{\omega_u}{C_d R_f}} \sqrt{\frac{\omega_u C_d R_f}{\omega_u C_d R_f + \sqrt{\omega_u C_d R_f - 1}}} \approx \frac{1}{2\pi} \sqrt{\frac{\omega_u}{C_d R_f}}$$

- $C_f$  can be chosen, given  $C_d$ ,  $R_f$ , and  $\omega_u$

- Higher  $\omega_u \Rightarrow$  higher bandwidth

- Zero introduced in the loop gain function

- First order behaviour around unity gain magnitude crossing

- "Lead-lag" compensation

- Minimize virtual ground node parasitics!

#### References

H. W. Bode, Network analysis and feedback amplifier design, D. Van Nostrand Company, 1945.

Behzad Razavi, Design of Analog CMOS Integrated Circuits, McGraw Hill, Aug. 2000.

K. N. Leung and P. K. Mok, "Analysis of multistage amplifier- frequency compensation," *IEEE Transactions on Circuits and Systems-1: Fundamental Theory and Applications*, vol. 48, no. 9, pp. 1041-1057, Sep. 2001.

T. Laxminidhi, V. Prasadu, and S. Pavan, "A Low Power 44-300 MHz Programmable Active-RC Filter in 0.18um CMOS", *Proceedings of the Custom Integrated Circuits Conference*, San Jose, September 2007.

N. Krishnapura, EE539: Analog Integrated Circuit Design, course offered at IIT Madras. http://www.ee.iitm.ac.in/ nagendra/teaching/EE539/courseinfo.html