# EE5390: Analog Integrated Circuit Design Introduction

#### Nagendra Krishnapura

Department of Electrical Engineering Indian Institute of Technology, Madras Chennai, 600036, India

6 Jan. 2010

#### Course info

- http://www.ee.iitm.ac.in/~nagendra/EE539/201001/courseinfo.html

- TAs: P. Rakesh, Kunal Karanjkar

- E Slot (Tue. 1100-1150, Wed. 1000-1050, Thu. 0800-0850, Fri. 1400-1450)

Check it regularly for recorded lectures, assignments, and references

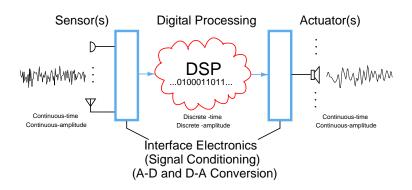

#### Modern signal processing systems

# Analog circuits in modern systems on VLSI chips

- Analog to digital conversion

- Digital to analog conversion

- Amplification

- Signal processing circuits at high frequencies

- Power management-voltage references, voltage regulators

- Oscillators, Phase locked loops

The last two are found even on many "digital" ICs

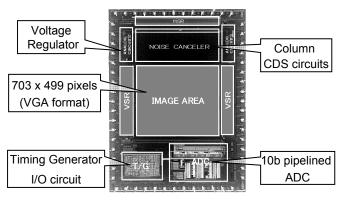

# Image sensor[ISSCC 2004]

# Chip Micrograph

Chip size: 4.74mm x 6.34mm

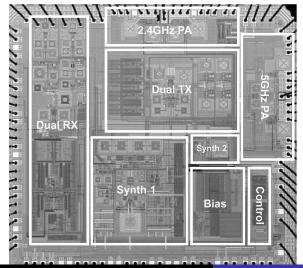

#### Wireless LAN transceiver[ISSCC 2004]

# Die Micrograph

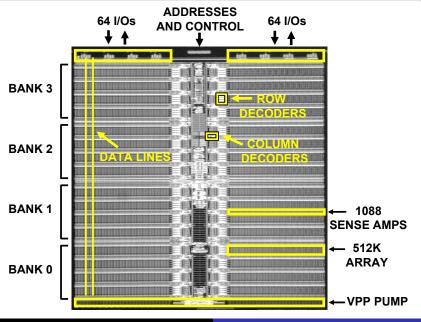

# DRAM[ISSCC 2004]

# Analog IC design in India

- Many companies starting analog centers

- Multinationals-TI, National, ST, ADI etc.

- Indian start ups-Cosmic, Manthan, Karmic, Sankalp etc.

- Big demand for skilled designers

- Interesting and profitable activity ¨

#### Course goals

Learn to design negative feedback circuits on CMOS ICs

- Negative feedback for controlling the output

- Amplifiers, voltage references, voltage regulators, biasing

- Phase locked loops

## Course prerequisites

- Circuit analysis-small and large signal

- Laplace transforms, frequency response, Bode plots, Differential equations

- Opamp circuits

- Single transistor amplifiers, differential pairs

EE542 (Analog Electronic Circuits)/EC201 (Analog Circuits)

# Course contents-Negative feedback amplifiers

- Amplifiers using negative feedback

- Stability, Frequency compensation

- Negative feedback circuits using opamps

- Opamp macromodel

# Course contents-Opamps on CMOS ICs

- Components available on a CMOS integrated circuit

- Device models-dc small signal, dc large signal, ac small signal, mismatch, noise

- Single stage opamp

- Cascode opamps

- Two stage opamp with miller compensation

# Course contents-Fully differential circuits

- Differential and common mode half circuits, common mode feedback

- Fully differential miller compensated opamp

- Fully differential feedforward compensated opamp

#### Course contents-Phase locked loop

- Frequency multiplication using negative feedback

- Type I, type II loops

- Oscillators

- Phase noise basics

- PLL noise transfer functions

# Course contents-Design of opamps

- Single stage opamp

- Folded, telescopic cascode opamps

- Two stage opamp

- Fully differential opamps and common mode feedback

- Applications: Bandgap reference, constant  $g_m$  bias generation

# Course contents-Applications

- Bandgap reference

- Constant current and constant gm bias generators

- Continuous-time filters

- Switched capacitor filters

# Design versus Analysis

- Design: Create something that doesn't yet exist

- Analysis: Analyze something that exists

## To be able to design

- Knowing analysis is necessary, not sufficient

- Multiple ways of looking at building blocks

- Trial and error approaches

- Intuitive thinking/understanding

- Curiosity

- Open mind

- Thoroughness

#### Intuition

- Intuitive thinking is not sloppy thinking!

- Relate problems to other problems already solved

- Use boundary conditions, dimension checks etc.

- Build your intuition

- Solve many problems

- Think about why the answer is what it is

- Come up with the form of the solution <u>before</u> applying full blown analysis

## Circuit analysis

- Nodal analysis-Kirchoff's Current Law (KCL) at each node

- Solve N simultaneous equations for an N node circuit

- Mesh analysis-Kirchoff's Voltage Law (KVL) around each loop

- Solve M simultaneous equations for a circuit with M independent loops

# Nodal analysis

$$i_{11}(\overline{V}) + i_{12}(\overline{V}) + \ldots + i_{1N}(\overline{V}) = i_1$$

$$i_{21}(\overline{V}) + i_{22}(\overline{V}) + \ldots + i_{2N}(\overline{V}) = i_2$$

$$\vdots$$

$$i_{N1}(\overline{V}) + i_{N2}(\overline{V}) + \ldots + i_{NN}(\overline{V}) = i_N$$

- $i_{kl}$ : Current in the branch between nodes k and l

- *i<sub>kk</sub>*: Current in the branch between node *k* and ground

- $v_k$ : Voltage at node k;  $\overline{v} = [v_1 v_2 \dots v_N]^T$

- *i<sub>k</sub>*: Current source into node *k*

$i_{kl}$  can be a nonlinear function of  $\overline{V}$

## Nodal analysis—Linear circuits

$$g_{11}v_1 + g_{12}v_2 + \ldots + g_{1N}v_N = i_1$$

$$g_{21}v_1 + g_{22}v_2 + \ldots + g_{2N}v_N = i_2$$

$$\vdots$$

$$g_{N1}v_1 + g_{N2}v_2 + \ldots + g_{NN}v_N = i_N$$

- g<sub>kl</sub>: Conductance between nodes k and l

- g<sub>kk</sub>: Conductance between node k and ground

- v<sub>k</sub>: Voltage at node k

- *i<sub>k</sub>*: Current source into node *k*

# Nodal analysis—Independent voltage source

$$\vdots$$

$\vdots$   $g_{k1} extstyle V_1 + g_{k2} extstyle V_2 + \ldots + g_{kN} extstyle V_N = extstyle i_k$  node  $k$   $\vdots$   $v_k = V_o$  node  $k$

Ideal voltage source V<sub>o</sub> connected to node k

## Nodal analysis—Controlled voltage source

$$\begin{array}{cccc}

\vdots & & \vdots \\

g_{k1}v_1 + g_{k2}v_2 + \ldots + g_{kN}v_N & = & i_k & \text{node } k \\

\vdots & & \vdots & \\

v_k - kv_l & = & 0 & \text{node } k

\end{array}$$

• Voltage controlled voltage source  $v_k = kv_l$  driving node k

## Nodal analysis—Controlled voltage source

$$g_{k1}v_1 + g_{k2}v_2 + \ldots + \frac{g_{kl}v_l}{R_m} + \ldots + g_{kN}v_N = i_k$$

node  $k$

$g_{k1}v_1 + g_{k2}v_2 + \ldots + \frac{v_k}{R_m} + \ldots + g_{kN}v_N = i_k$  node  $k$

$g_{l1}v_1 + g_{l2}v_2 + \ldots + \frac{g_{lk}v_k}{R_m} + \ldots + g_{lN}v_N = i_l$  node  $l$

$g_{l1}v_1 + g_{l2}v_2 + \ldots - \frac{v_k}{R_m} + \ldots + g_{lN}v_N = i_l$  node  $l$

• Current controlled voltage source  $v_k = R_m i_{kl}$  driving node k

#### Nodal analysis—Controlled current source

$$g_{k1}v_1 + g_{k2}v_2 + \ldots + g_{kl}v_l + \ldots + g_{kN}v_N = i_k + g_mv_l$$

$$g_{k1}v_1 + g_{k2}v_2 + \ldots + g_{kl}v_l - g_mv_l + \ldots + g_{kN}v_N = i_k$$

• Current controlled voltage source  $i_0 = g_m v_l$  driving node k

## Nodal analysis—Ideal opamp

$$\vdots \\ g_{m1}v_1 + g_{m2}v_2 + \ldots + g_{mN}v_N &= i_m \quad \text{node } m \\ \vdots \\ v_k - v_l &= 0 \quad \text{node } m$$

Ideal opamp with input terminals at nodes k, l and output at node m

# Nodal analysis—solution

$$\begin{bmatrix} g_{11}g_{12} \dots g_{1N} \\ g_{21}g_{22} \dots g_{2N} \\ \vdots \\ g_{N1}g_{N2} \dots g_{NN} \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \\ \vdots \\ v_N \end{bmatrix} = \begin{bmatrix} i_1 \\ i_2 \\ \vdots \\ i_N \end{bmatrix}$$

$$G\overline{V} = \overline{i}$$

$$V = G^{-1}\overline{i}$$

- g<sub>kl</sub>: Conductance between nodes k and l

- g<sub>kk</sub>: Conductance between node k and ground

- v<sub>k</sub>: Voltage at node k

- *i<sub>k</sub>*: Current source into node *k*

- Modified terms for voltage sources or controlled sources

- Matrix inversion yields the solution

#### Nodal analysis—solution

$$v_{k} = \frac{\begin{vmatrix} g_{11}g_{12} \dots i_{1} \dots g_{1N} \\ g_{21}g_{22} \dots i_{2} \dots g_{2N} \\ \vdots \\ g_{N1}g_{N2} \dots i_{N} \dots g_{NN} \end{vmatrix}}{\begin{vmatrix} g_{11}g_{12} \dots g_{1k} \dots g_{1N} \\ g_{21}g_{22} \dots g_{2k} \dots g_{2N} \\ \vdots \\ g_{N1}g_{N2} \dots g_{Nk} \dots g_{NN} \end{vmatrix}}$$

Cramer's rule can be used for matrix inversion

# Circuits with capacitors and inductors

$$\begin{bmatrix} Y_{11}(s)Y_{12}(s)\dots Y_{1N}(s) \\ Y_{21}(s)Y_{22}(s)\dots Y_{2N}(s) \\ \vdots \\ Y_{N1}(s)Y_{N2}(s)\dots Y_{NN}(s) \end{bmatrix} \begin{bmatrix} V_1(s) \\ V_2(s) \\ \vdots \\ V_N(s) \end{bmatrix} = \begin{bmatrix} I_1(s) \\ I_2(s) \\ \vdots \\ I_N(s) \end{bmatrix}$$

$$\mathbb{Y}(s)\overline{V}(s) = \overline{I}(s)$$

$$\overline{V}(s) = \mathbb{Y}^{-1}\overline{I}(s)$$

- Conductances  $g_{kl}$  replaced by admittances  $Y_{kl}(s)$

- Roots of the determinant of  $\mathbb{Y}(s)$  are system poles

# Laplace transform analysis for linear systems

```

Input Output  X(s) = H(s)X(s)   e^{st} = H(s)e^{st}   X(j\omega) = H(j\omega)X(j\omega)   e^{j\omega t} = H(j\omega)e^{j\omega t}   \cos(\omega t) = |H(j\omega)|\cos(\omega t + \angle H(j\omega))  (Steady state solution)

```

- Linear time invariant system described by its transfer function H(s)

- H(s) is the laplace transform of the impulse response

- $s = j\omega$  represents a sinusoidal frequency  $\omega$

## Laplace transform analysis for linear systems

Transfer function H(s) (no poles at the origin)

$$H(s) = A_{dc} \frac{1 + b_1 s + b_2 s^2 + \ldots + b_M s^M}{1 + b_1 s + b_2 s^2 + \ldots + b_N s^N}$$

$$= A_{dc} \frac{\prod_{k=1}^{M} 1 + s/z_k}{\prod_{k=1}^{N} 1 + s/p_k}$$

Single pole at the origin

$$H(s) = \frac{\omega_u}{s} \frac{\prod_{k=1}^{M} 1 + s/z_k}{\prod_{k=2}^{N} 1 + s/p_k}$$

All poles p<sub>k</sub> must be in the left half plane for stability

## Frequency and time domain analyses

#### Frequency domain

- Algebraic equations-easier solutions

- Only for linear systems

#### Time domain

- Differential equations-more difficult to solve

- Can be used for nonlinear systems as well

- Piecewise linear systems occur quite frequently (e.g. saturation)

#### Bode plots

- Sinusoidal steady state response characterized by  $|H(j\omega)|$ ,  $\angle H(j\omega)$

- Bode plot: Plot of  $20 \log |H(j\omega)|$ ,  $\angle H(j\omega)$  versus  $\log \omega$  approximated by straight line segments

- Good approximation for real poles and zeros

#### **Simulators**

Very powerful tools, indispensable for complex calculations, but GIGO!

- Matlab: System level analysis (Frequency response, pole-zero, transfer functions)

- Spice: Circuit analysis

- Maxima: Symbolic analysis

#### References: Recorded lectures

EC201: Analog Circuits

EE539: Past years' lectures

URL: http://www.ee.iitm.ac.in/~nagendra/videolectures/

#### References

- Behzad Razavi, Design of Analog CMOS Integrated Circuits, McGraw-Hill, August 2000.

- Hayt and Kemmerly, Engineering Circuit Analysis, McGraw Hill, 6/e.

- B. P. Lathi, Linear Systems and Signals, Oxford University Press, 2 edition, 2004.

- Sergio Franco, Design with operational amplifiers and analog ICs, Tata McGraw Hill.

- H. Takahashi et al., "A 3.9 μm pixel pitch VGA format 10b digital image sensor with 1.5-transistor/pixel," IEEE International Solid-State Circuits Conference, vol. XVII, pp. 108 - 109, February 2004.

- M. Zargari et al., "A single-chip dual-band tri-mode CMOS transceiver for IEEE 802.11a/b/g WLAN," IEEE International Solid-State Circuits Conference, vol. XVII, pp. 96 - 97, February 2004.

- K. Hardee et al. "A 0.6V 205MHz 19.5ns tRC 16Mb embedded DRAM," IEEE International Solid-State Circuits Conference, vol. XVII, pp. 200 - 201, February 2004.