### Topics

- Introduction to memory

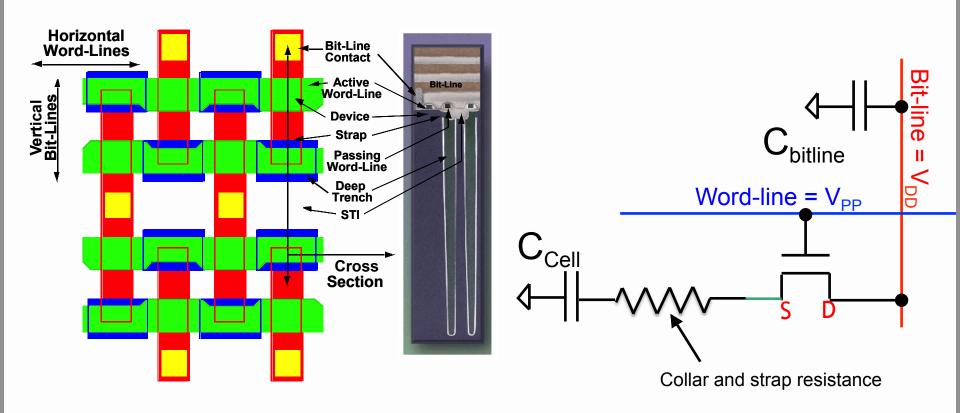

- □ DRAM basics and bitcell array

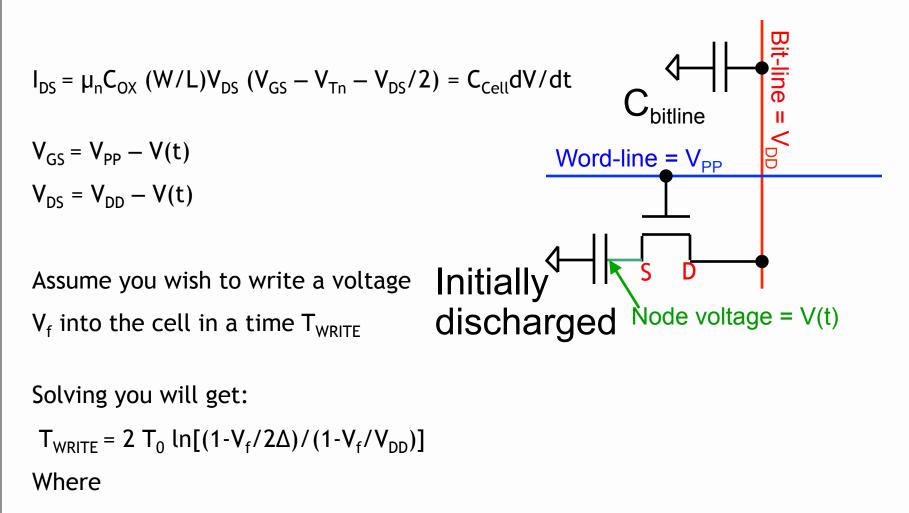

- eDRAM Write Analysis

- DRAM Sense-Amplifier Specification

- eDRAM operational details (case study)

- Noise concerns

- □ Wordline driver (WLDRV) and level translators (LT)

- □ Challenges in eDRAM

- Understanding Timing diagram An example

Introduction of eDRAM

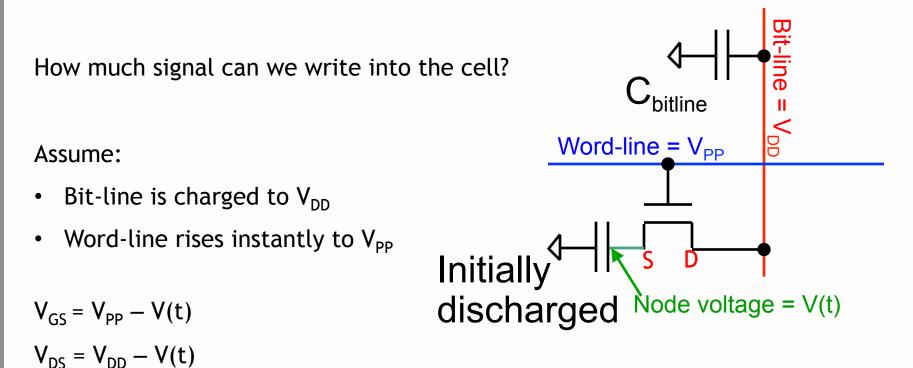

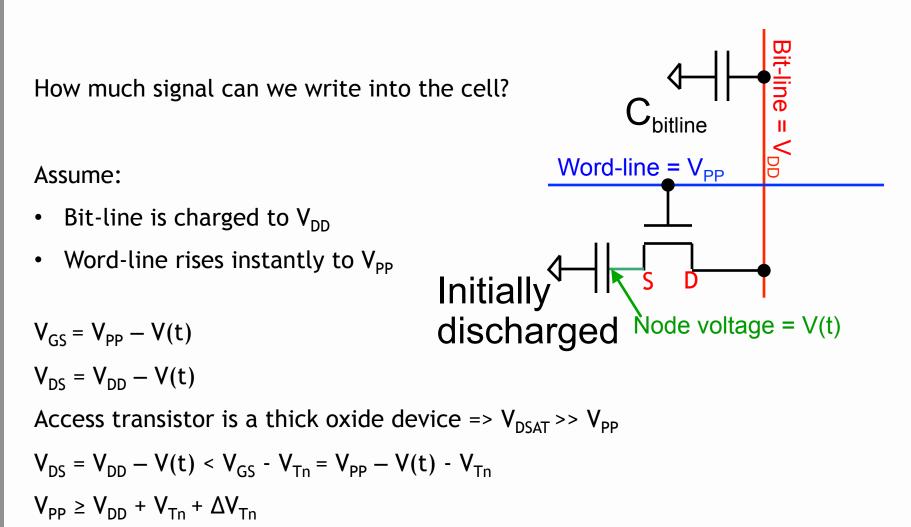

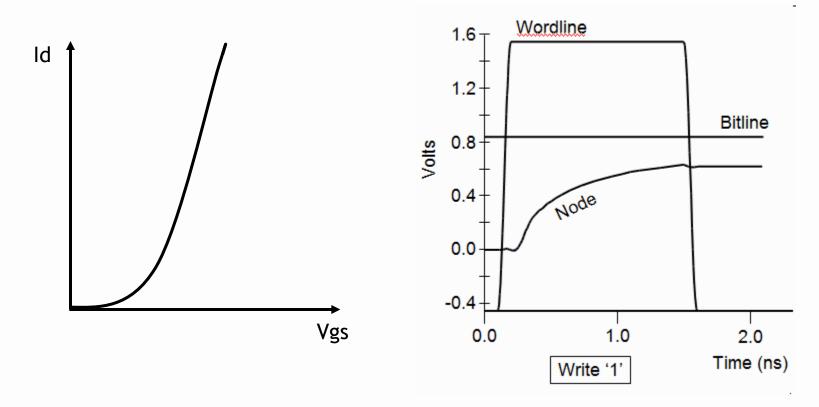

Access device is in the linear region throughout

Introduction of eDRAM

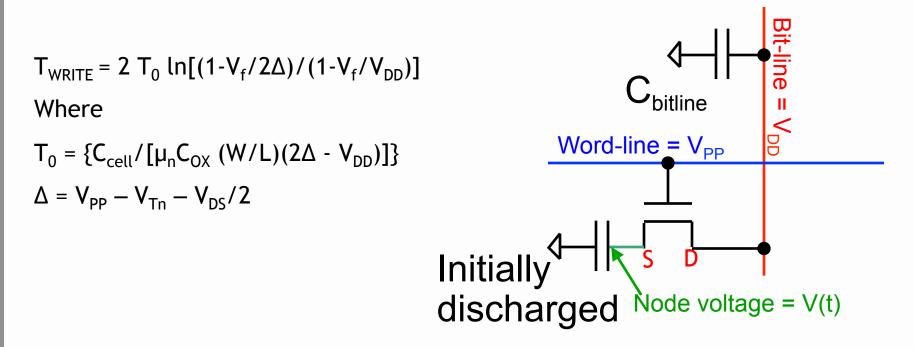

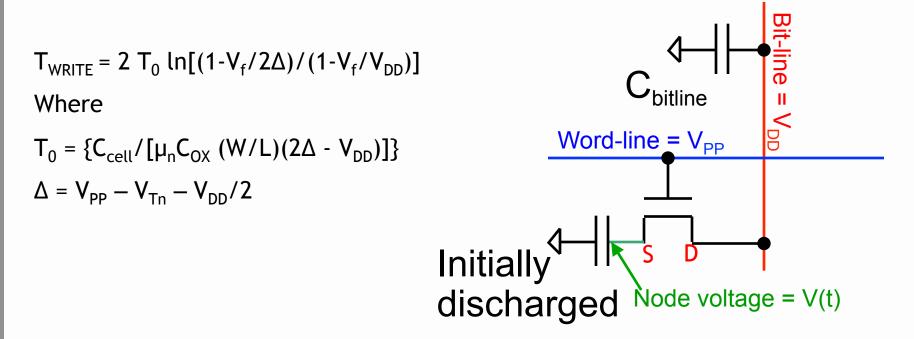

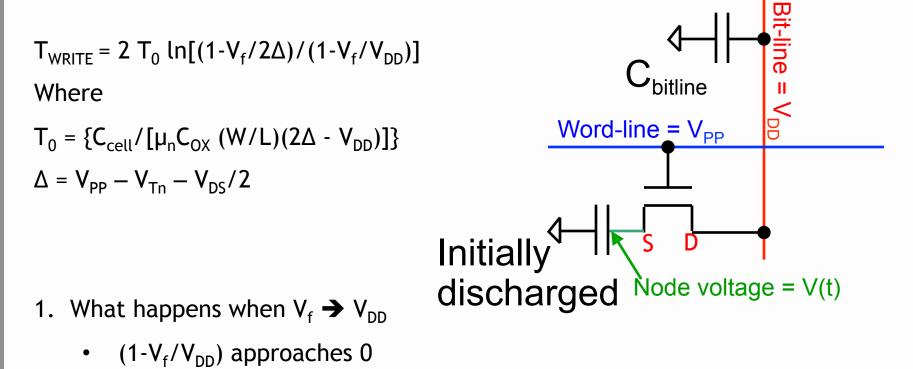

$$T_0 = \{C_{cell} / [\mu_n C_{OX} (W/L)(2\Delta - V_{DD})]\}$$

$$\Delta = V_{PP} - V_{Tn} - V_{DD}/2$$

IDS = MACOX W. VDS (VGS. VTn - VDS) IDS= C<u>dv</u> (C= Ccell) K VDS (VGS-VFn-VDS) = GOW K= Mn Cox (W)  $\frac{K}{C} \cdot (V_{DD} - V) (V_{PP} - V - V_{T_{H}} - \frac{V_{DP} - V}{2}) = \frac{CW/dt}{2}$  $= \left(\frac{K}{C}\right) \left(\frac{V_{DD}-V}{C}\right) \left(\frac{V_{DD}-V_{TN}-V_{DD}}{2}-\frac{V}{2}\right) = \frac{dV}{dt}$ =>  $\frac{\pi}{C} dt = \frac{dV}{(V_{DD-V})(\Delta - \frac{V}{2})}$ Where  $\Delta = (Vpp - VTn - VDD/2)$  $\Rightarrow \frac{K}{C} dt = \frac{2 dN}{(2A - VD)} \times \left[\frac{1}{VDD - V} - \frac{1}{2A - V}\right]$ =>  $\frac{K}{C}$  (WRITE =  $\frac{2}{2A}$  ·  $\ln \left[\frac{2A-V}{VDD-V}\right]^{V_{f}}$

=>  $\mathcal{C}_{\text{UDRITE}} = \frac{2C}{K(24-V_{DD})} \ln \left[ \frac{24-V_{f}}{V_{DD}-V_{f}} \right] \left[ \frac{V_{DD}}{24} \right]$  $T_{\text{CORITE}} = \frac{2C}{K(20 - V_{DD})} \ln \left[ \frac{1 - V_{\text{F}}/2D}{1 - V_{\text{F}}/4D} \right]$

#### Introduction of eDRAM

### Write-Margin – Analysis

- 1. What happens when VPP is increased?

- 2. What happens when  $V_f \rightarrow V_{DD}$

## Write-Margin – Analysis

- 1. What happens when VPP is increased?

- $\Delta$  increases and T<sub>0</sub> decreases

- $ln[(1-V_f/2\Delta)/(1-V_f/V_{DD})]$  increases logarithmically

- T<sub>WRITE</sub> effectively decreases.

- However WL power goes up as  $(V_{PP} V_{WL})^2$

## Write-Margin – Analysis

•  $\ln[(1-V_f/2\Delta)/(1-V_f/V_{DD})]$  shoots to  $\infty$

You cannot write a FULL  $V_{DD}$  into the cell in finite time

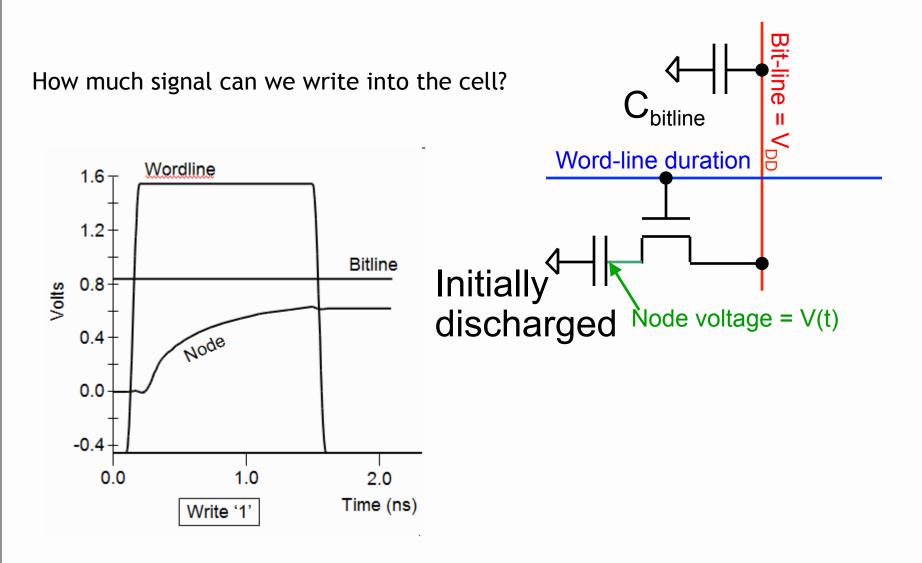

## Storing data '1' in the cell

Vgs for pass transistor reduces as bitcell voltage rises, increasing Ron

Why there is a reduction in cell voltage after WL closes? Experiment

# Reality

The node takes longer to charge than what we calculated analytically Conclusions do not change:

- Increasing V<sub>PP</sub> decreases the write time

- Cannot write a full V<sub>DD</sub> in finite time

### Topics

- Introduction to memory

- □ DRAM basics and bitcell array

- eDRAM Write Analysis

- DRAM Sense-Amplifier Specification

- educational details (case study)

- Noise concerns

- □ Wordline driver (WLDRV) and level translators (LT)

- □ Challenges in eDRAM

- Understanding Timing diagram An example

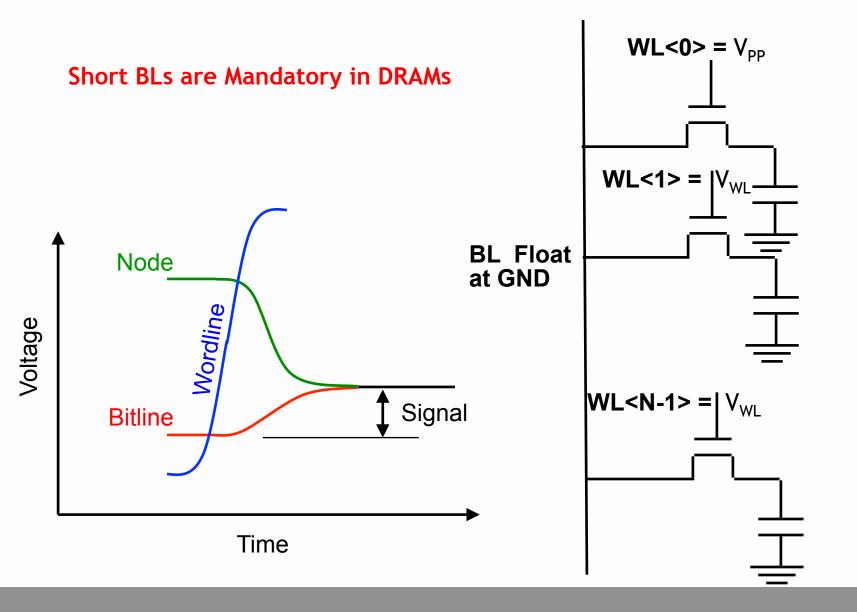

### Signal: # WLs on a BL

DRAM

# SRAM vs DRAM

#### Assume a 1Mb memory with 512 WLs and 2048 BLs and 8 Columns. i.e. 256 DLs

|                                             | SRAM | DRAM      |

|---------------------------------------------|------|-----------|

| #WLs per BL                                 | 512  | 32        |

| # BLs per DL                                | 8    | 8         |

| Sharing Sense Amps across columns           | Yes  | Possible? |

| Effective number of cells connected to a SA | 4096 | ?         |

| # Sense Amps                                | 256  | ?         |

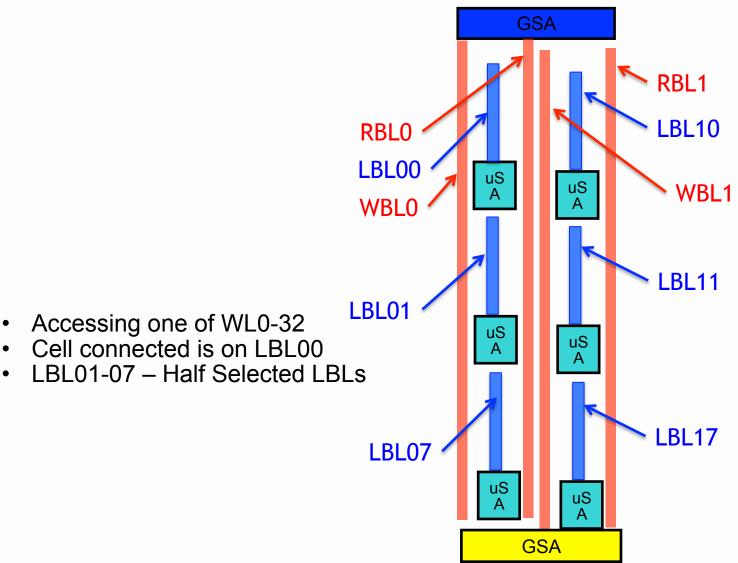

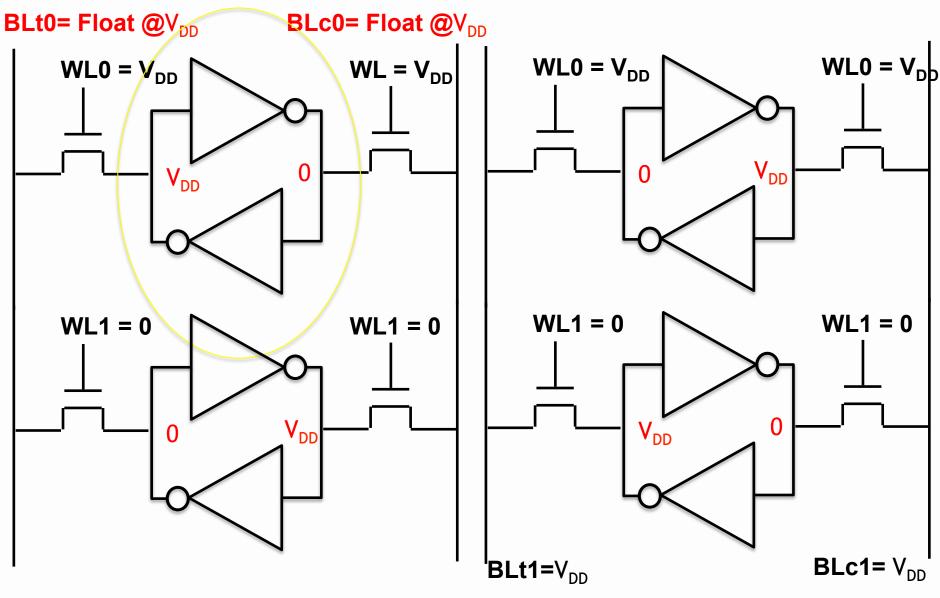

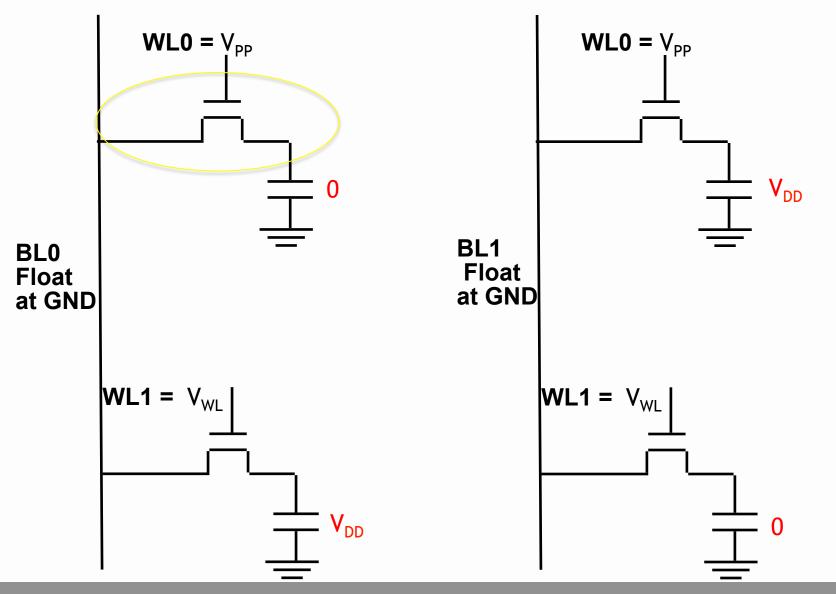

## Half Select Condition - SRAM

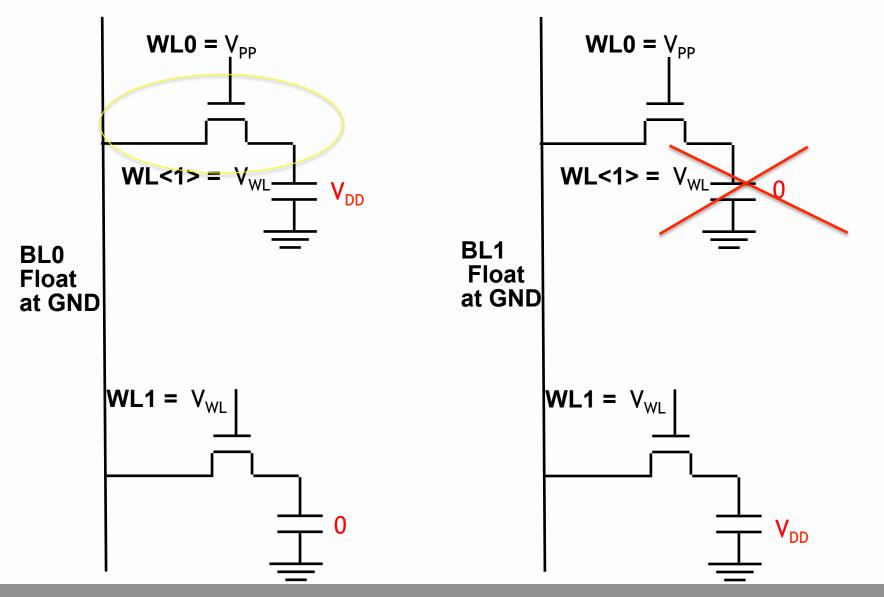

# Half Select Condition - eDRAM

Introduction of eDRAM

# Half Select Condition - eDRAM

Introduction of eDRAM

# SRAM vs DRAM

#### Assume a 1Mb memory with 512 WLs and 2048 BLs and 8 Columns. i.e. 256 DLs

|                                             | SRAM | DRAM |

|---------------------------------------------|------|------|

| #WLs per BL                                 | 512  | 32   |

| # BLs per DL                                | 8    | 8    |

| Sharing Sense Amps across columns           | Yes  | No   |

| Effective number of cells connected to a SA | 4096 | 32   |

| # Sense Amps                                | 256  |      |

Extremely small SA

- Number of transistors

- Sizes of transistors

### Topics

- Introduction to memory

- □ DRAM basics and bitcell array

- eDRAM Write Analysis

- DRAM Sense-Amplifier Specification

- eDRAM operational details (case study)

- Noise concerns

- □ Wordline driver (WLDRV) and level translators (LT)

- □ Challenges in eDRAM

- Understanding Timing diagram An example

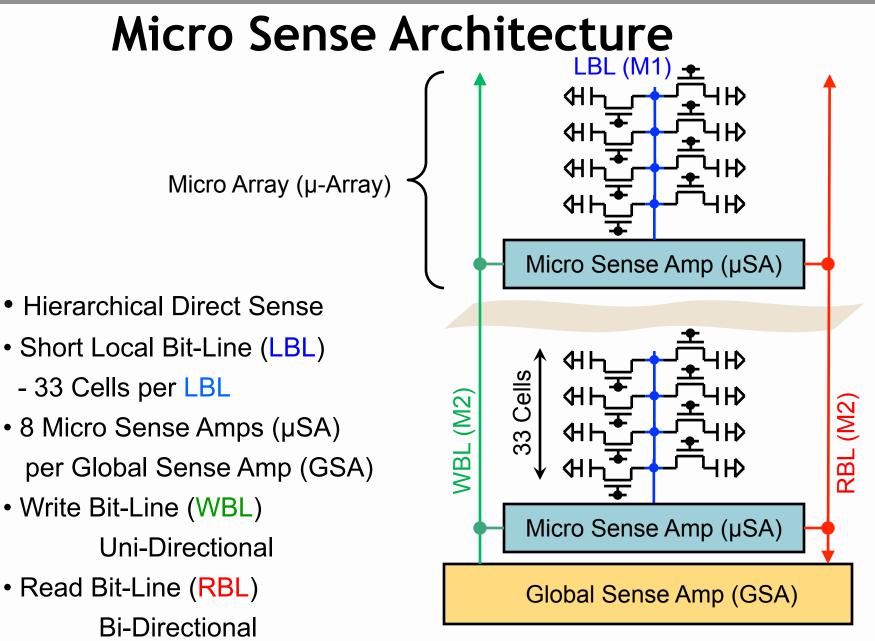

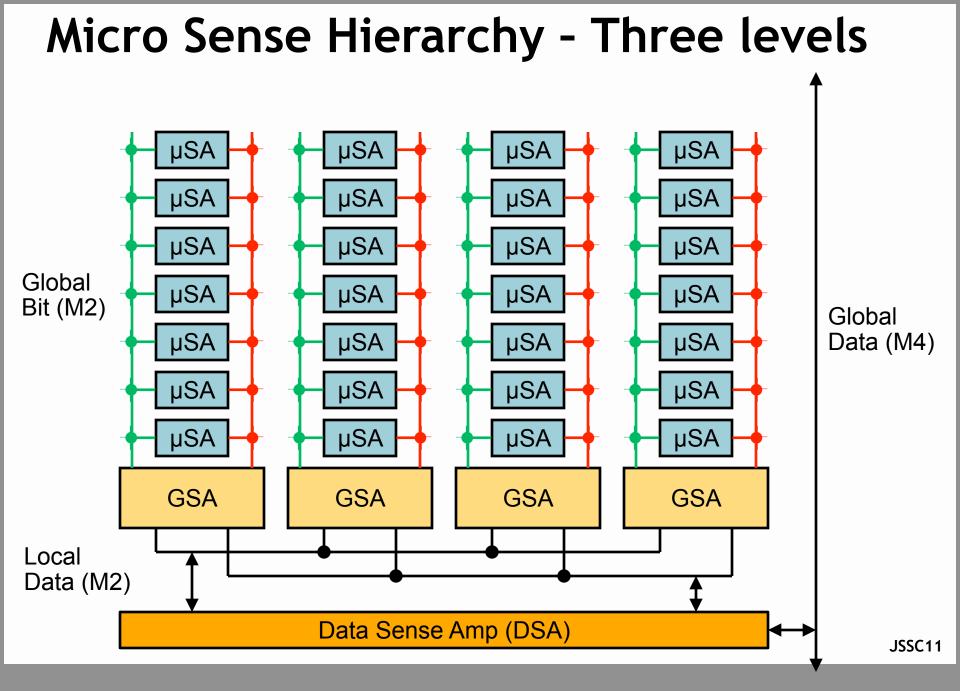

## DRAM Operation Details (Case Study)

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 43, NO. 1, JANUARY 2008

A 500 MHz Random Cycle, 1.5 ns Latency, SOI Embedded DRAM Macro Featuring a Three-Transistor Micro Sense Amplifier (John Barth/IBM)

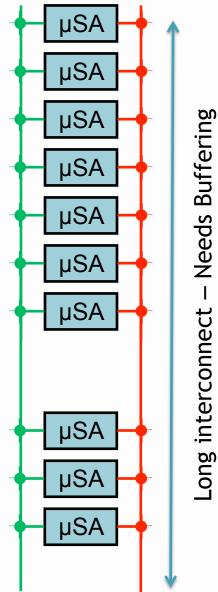

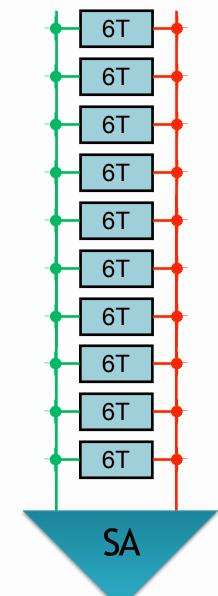

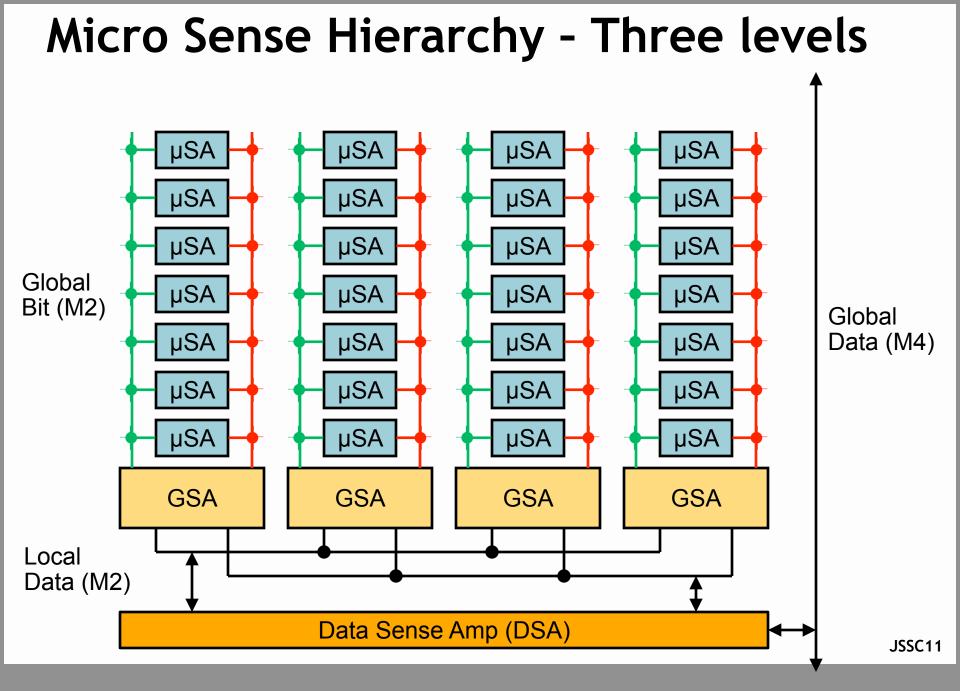

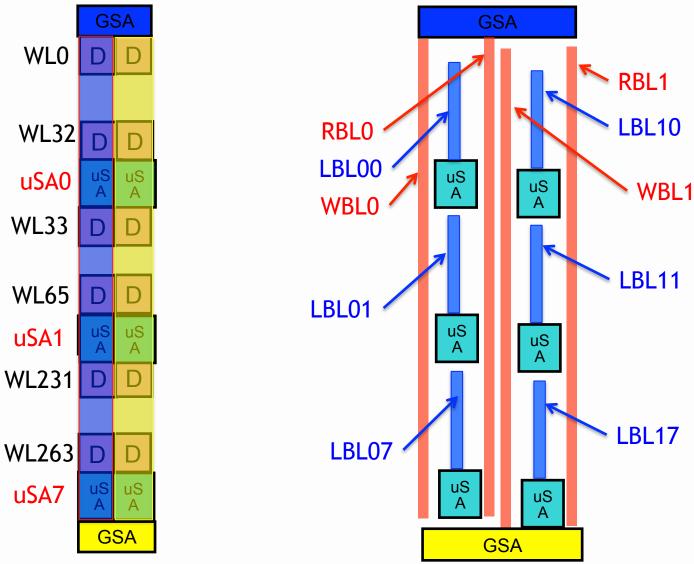

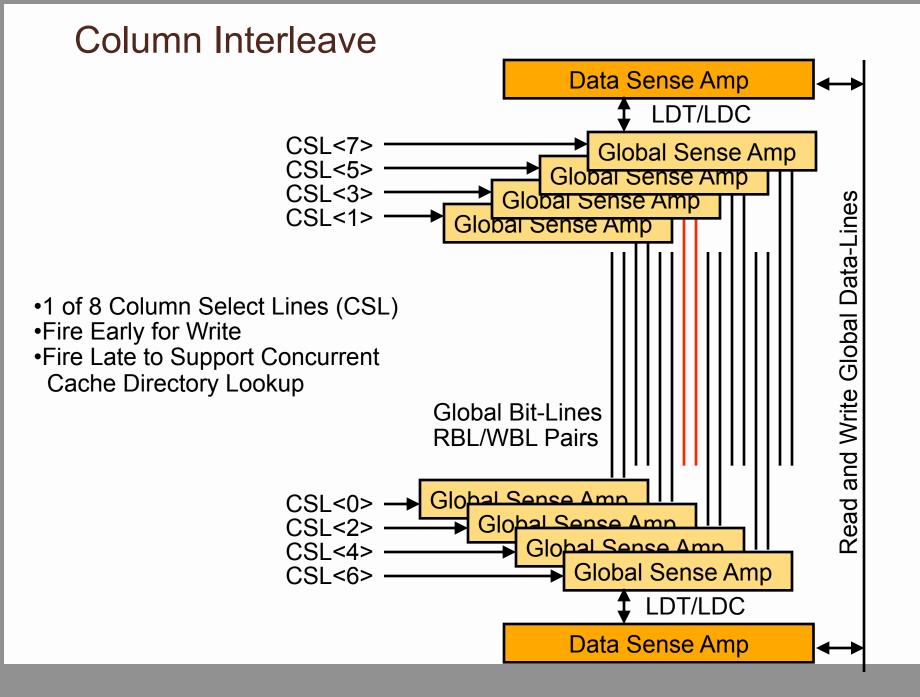

## **Sense Hierarchy - Motivation**

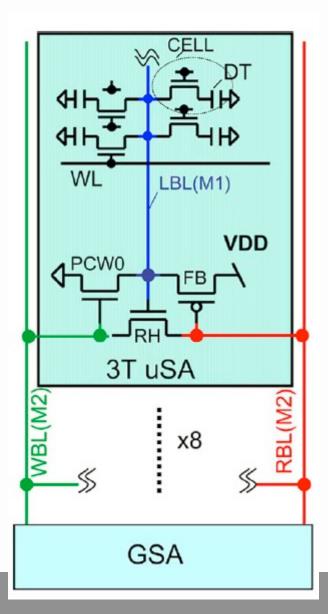

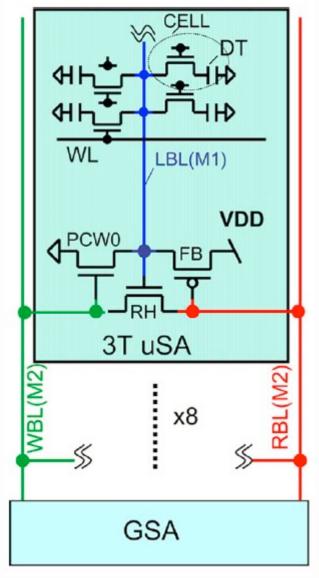

## 3T uSA operation

#### **Pre-charge**

WL is low. WBL and RBL both pre-charged to HIGH. Next GSA drives WBL low. LBL floats to GND level

**Read "0"** LBL remains LOW. RBL is HIGH. Sensed as a "0"

#### **Read "1"**

LBL is HIGH. Turns on RH, pulls RBL LOW. + feedback as pFET FB turns ON. Sensed as a "1"

#### Write "1"

GSA pulls RBL to GND. FB pFET turns ON Happens while WL rises (direct write)

#### Write "0"

WBL is HIGH, PCW0 ON. Clamps LBL to GND As WL activates.

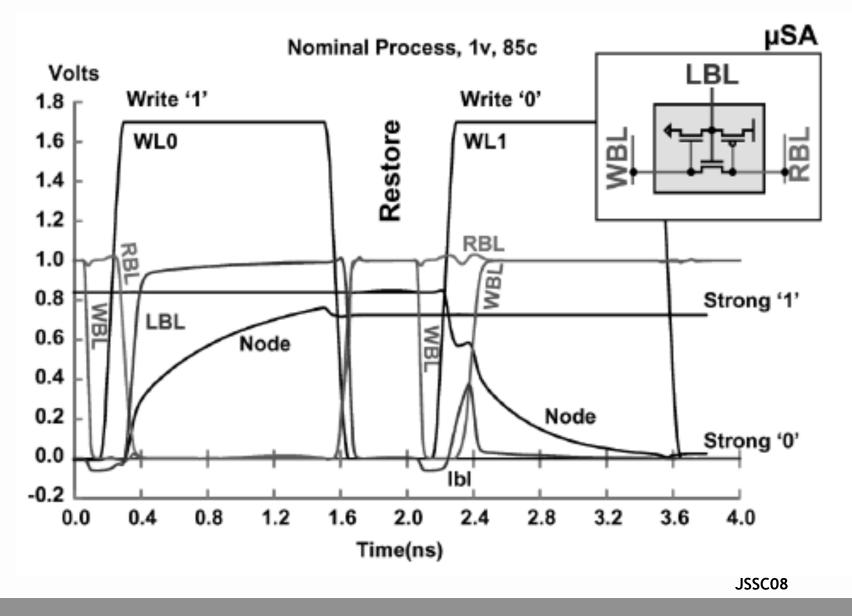

## Simulations - Write

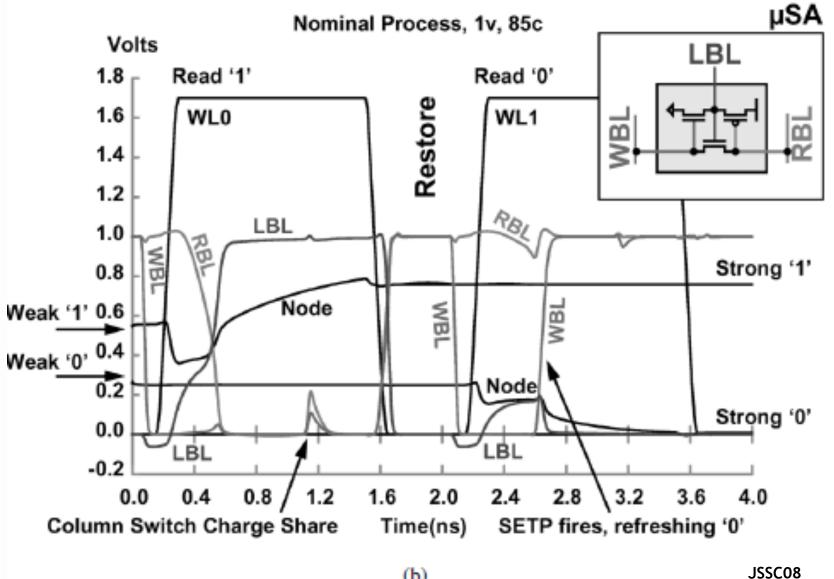

### Simulations - Read

(b)

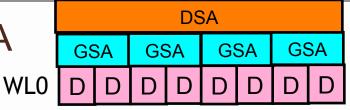

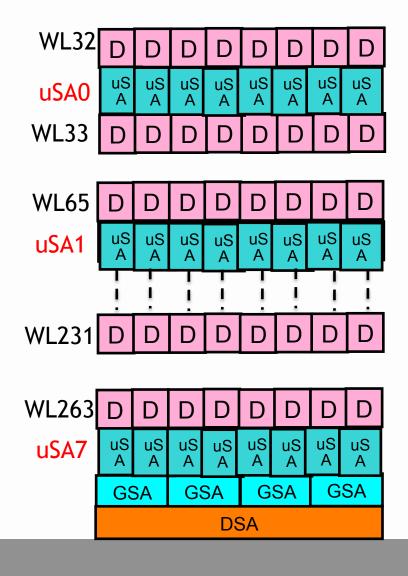

### Layout Floor plan of Array+SA

GSA Should fit into the bitcell width or n\*bitcell width

Thus, distributed GSA on two sides of bitcell array

### Layout Floor plan of Array+SA

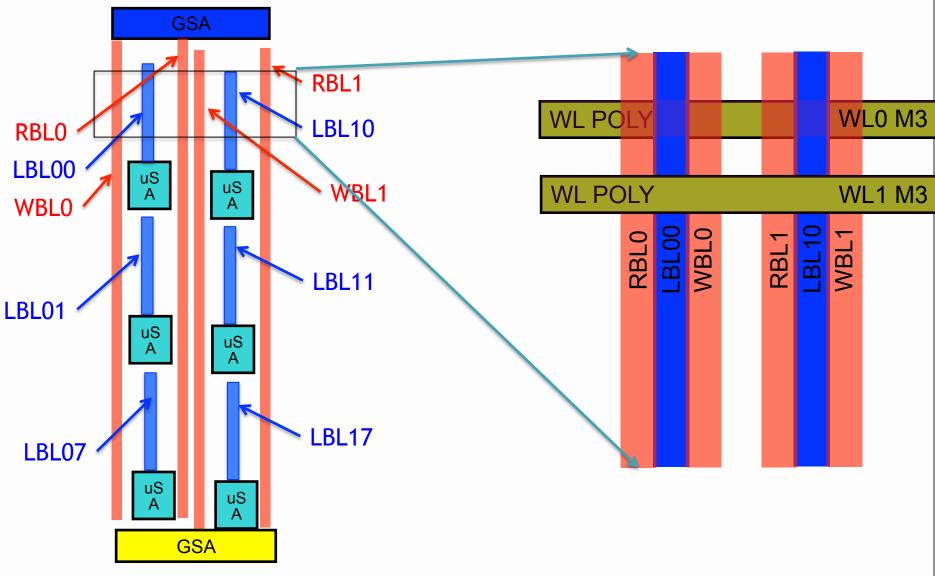

# LAYOUT of array

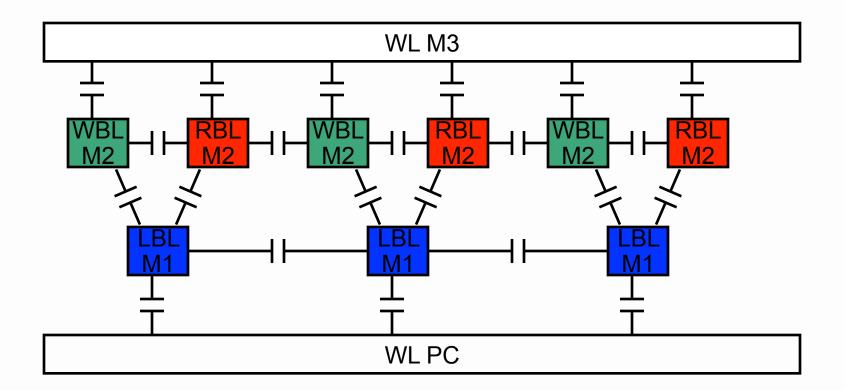

# Micro Sense Local Bit-line Cross Section

Single Ended Sense – Twist not effective Line to Line Coupling must be managed

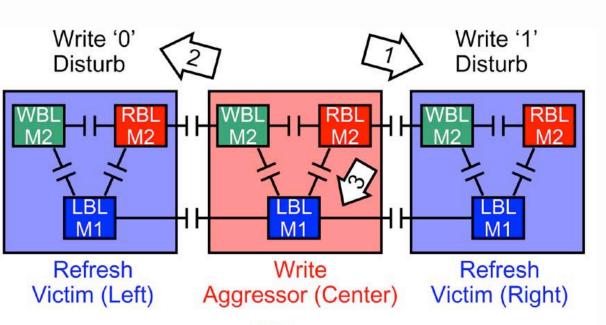

# **Micro Sense Coupling Mechanisms**

- 1. Write '1' Couples WBL below Ground Increasing RH leakage during Refresh '0'

- Write '0' Couples RBL above VDD Delaying Feedback during Refresh '1'

- 3. Read '1' Couples Half-Selected LBL Below GND Increasing Array Device Sub-VT Leakage

# Half Selected LBL