### **Variation Characterization**

#### Rahul Rao

IBM Systems and Technology Group

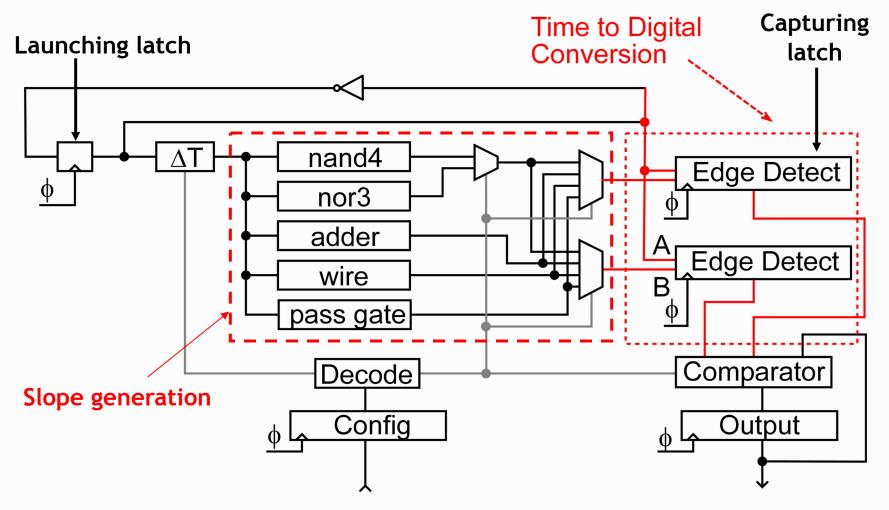

# Time-to-Digital Conversion Using an Edge Detector

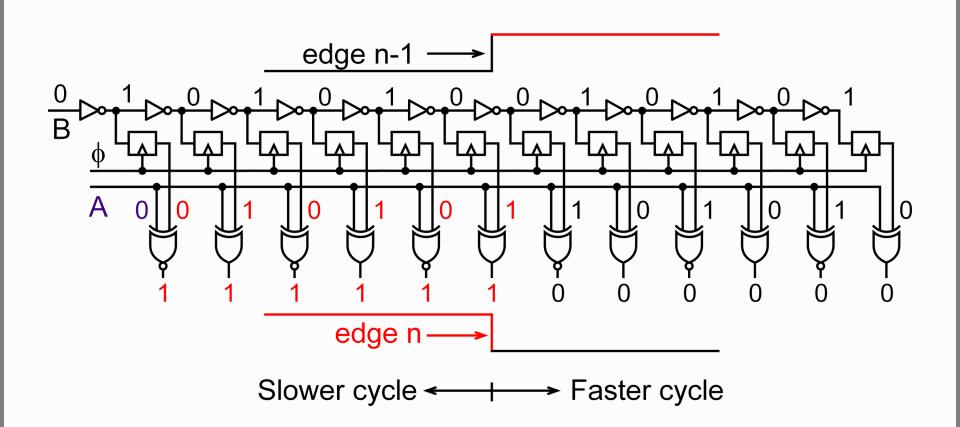

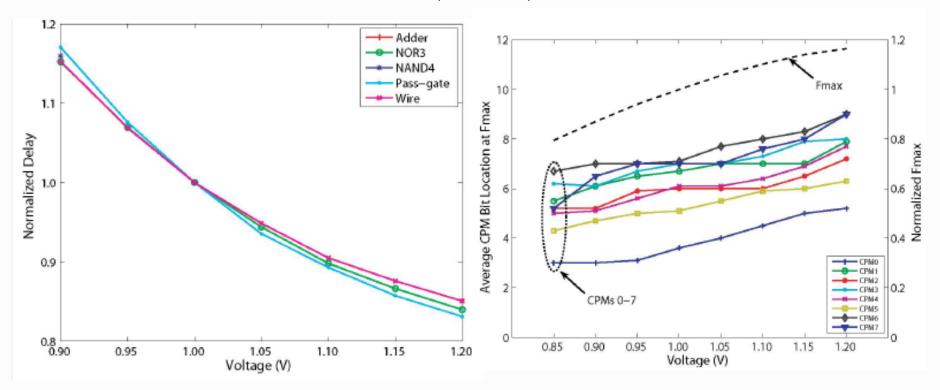

# Delay based Sensing - Critical Path Monitor (CPM)

# Delay based Sensing - Critical Path Monitor (CPM)

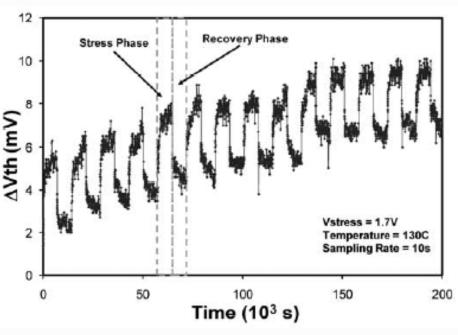

## Characterizing Bias Temperature Instability

### Challenge

- Characterize the extent of  $V_{TH}$  shift due to aging

- Isolate the contributions of NBTI vs. PBTI while minimizing noise due to other effects (hot carrier effects, device breakdown)

- Rapid post-stress measurement (or during stress measurement) to prevent recovery

#### Methods

- I-V measurement of devices using stress pulses

- Delay (Oscillator Frequency) based measurement

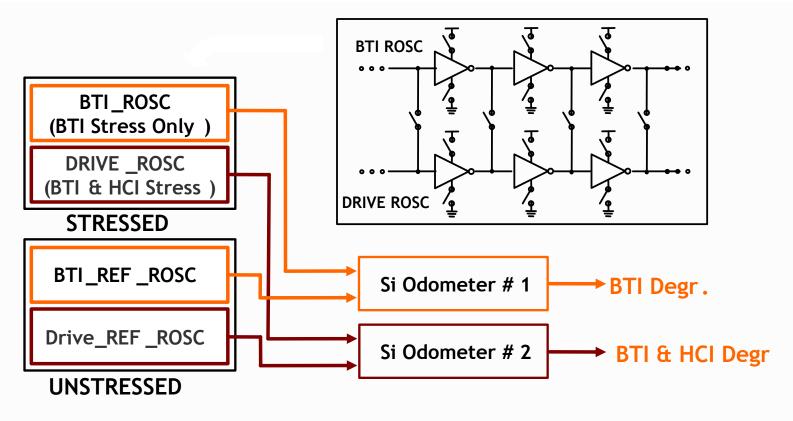

#### All-in-One Silicon Odometer

- Isolates BTI, HCI and TDDB effects

- 4 ROSCs: 2 stressed, and 2 unstressed

- BTI\_ROSC degrades due to BTI only; "DRIVE" ROSC ages due to BTI & HCI

- Frequency degradation measured with beat frequency detection circuits

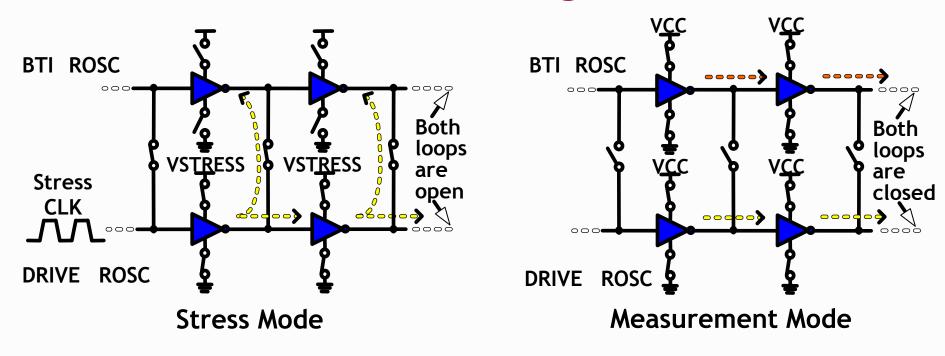

## **BackDrive Configuration**

- Stress Mode (ROSC loops opened)

- BTI\_ROSC gated off, DRIVE\_ROSC drives transitions; I/P driven by VCO

- Measurement Mode (ROSC loops closed)

- Both ROSCs connected to the power supply @ VCC, switches between them are opened

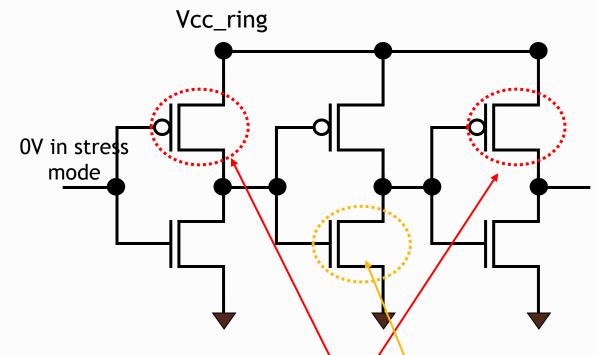

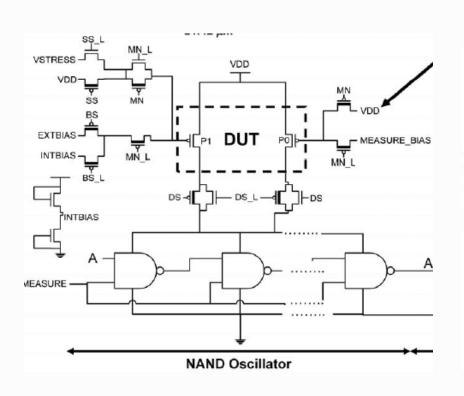

## **Ring Oscillator Based Circuit**

#### In Stress Mode:

Vcc\_ring and/or temperature are raised. Primary input = 0

#### In Measurement Mode:

Vcc\_ring and/or temperature brought back to normal condition

PMOS with 0V input (with RED Circle in the figure) is stressed.

Measure the frequency difference between **stressed** case and **unstressed** case

Impossible to isolate the effect from each of NBTI and PBTI

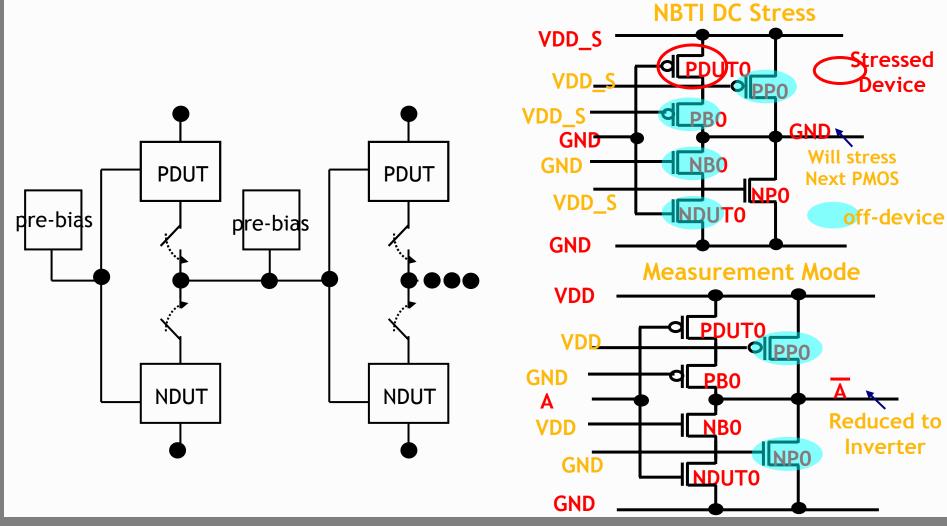

### **Unified NBTI - PBTI Sensor**

Objective: Maintain the simplicity of RSC style monitoring circuit, while isolating NBTI and PBTI

#### Sub-Threshold BTI Sensor

PMOS Device Biased in sub-threshold region controls current to a Oscillator

Measured threshold voltage shift during Stress and Recovery

# Can we directly characterize more complex circuit properties?

- Read and Write margin of SRAM

- Depends on both local variation and global variations

- Individual device characterization can help but direct characterization of read/write margin can provide better information

- Temperature

- Using Delay

- Using Leakage

- Power

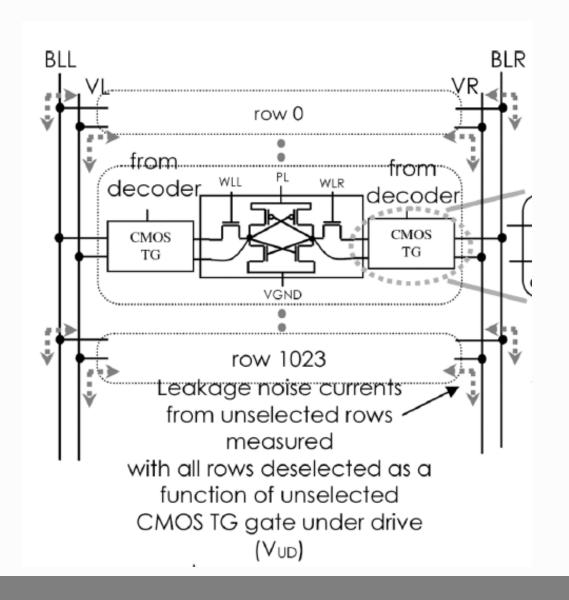

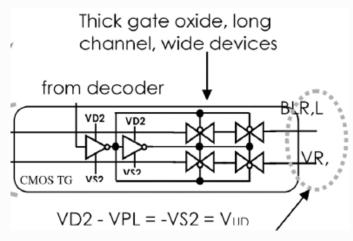

## **SRAM Fluctuation Monitor**

For unselected cells, underdrive pass gates to reduce leakage noise

For selected cell, overdrive pass gate to minimize ON resistance

## **SRAM Fluctuation Monitor**

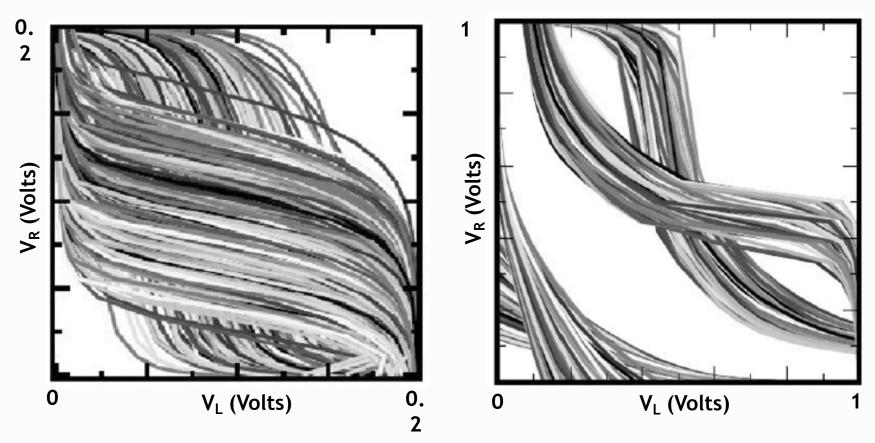

Voltage Transfer Characteristics (measured) for 1k cells for different supply voltages

## Sensing Temperature Through Delay

- Delay increases with Temperature

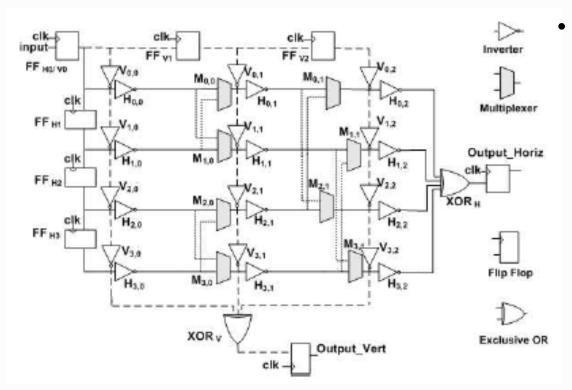

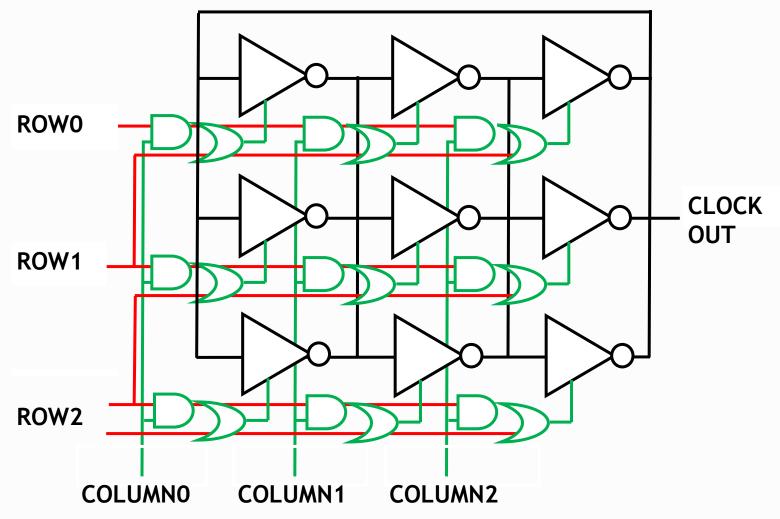

- Matrix structure of gates with multiplexers that enable activation of any path (using scan-chain controls)

- Adjust clock frequency to detect path-delay (temperature)

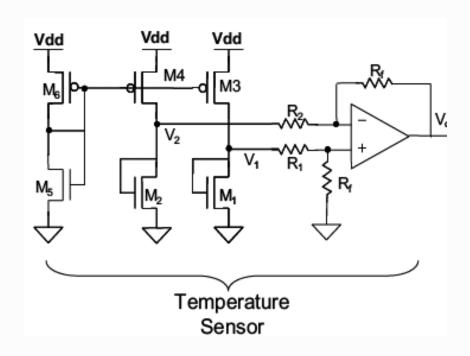

## Sensing Temperature Through Leakage

Leakage is exponential function of temperature

(Make devices large to eliminate RDF, LER effects)

Voltage effects cancelled out

$$V_{out} = \frac{R_f}{R_1} \sqrt[a]{\frac{L}{\mu C_{ox}}} \left( \sqrt[a]{\frac{I_1}{W_1}} - \sqrt[a]{\frac{I_2}{W_2}} \right)$$

Variation Adaptation

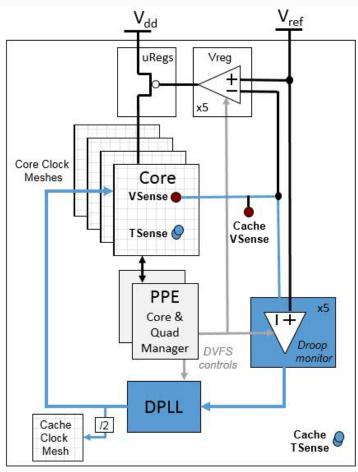

## Block diagram of Detection and **Compensation System**

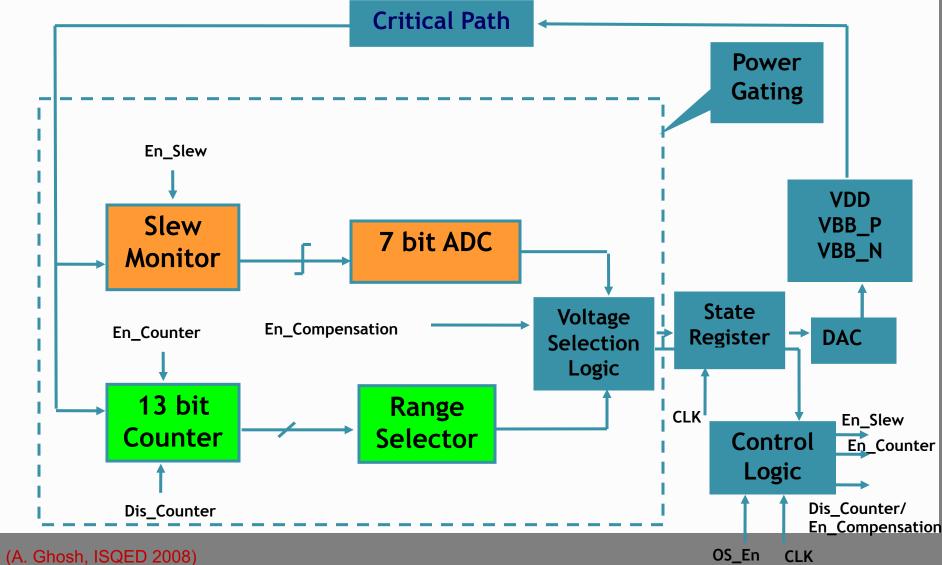

# Adaptive Body-biasing Based on Delay and Rise/Fall Slew Difference

|               |             | $\Delta t_{	ext{R-F}} > \Delta t_{	ext{R-Fnom}}$ | $\Delta t_{R-F} = \Delta t_{R-Fnom}$ | $\Delta t_{	ext{R-F}} < \Delta t_{	ext{R-Fnom}}$ |

|---------------|-------------|--------------------------------------------------|--------------------------------------|--------------------------------------------------|

| $f > f_{nom}$ | NMOS        | LRBB                                             | RBB                                  | SRBB                                             |

|               | <b>PMOS</b> | SRBB                                             | RBB                                  | LRBB                                             |

| $f = f_{nom}$ | NMOS        | RBB                                              | No bias                              | FBB                                              |

|               | <b>PMOS</b> | FBB                                              | No bias                              | RBB                                              |

| $f < f_{nom}$ | NMOS        | SFBB                                             | FBB                                  | LFBB                                             |

|               | <b>PMOS</b> | LFBB                                             | FBB                                  | SFBB                                             |

- RBB is effective to reduce leakage

- FBB is effective to improve operating frequency of a design in active mode

- PMOS & NMOS need independent body biasing

(A. Ghosh, ISQED 2008)

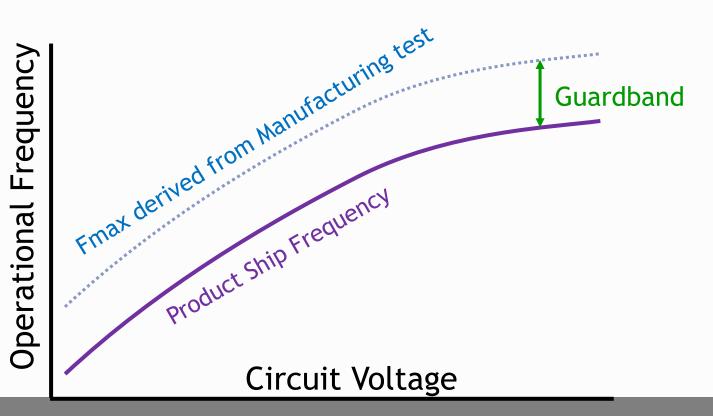

#### **Guard bands**

- Designs must account for changes over time:

- permanent physical degradation

- temporary operational transients

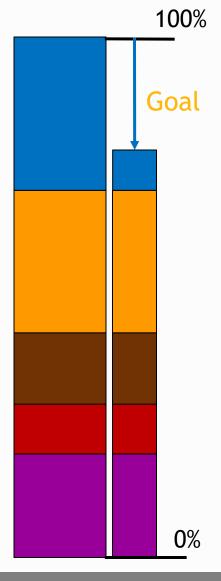

## Typical guardband components

Voltage variation

power supply & system load-line inaccuracy, droop & noise

Thermal variation

environment & workload

Wear out

lifetime degradation

Manufacturing Test Inaccuracy

correlation error

Uncertainty

margin for the "unknown"

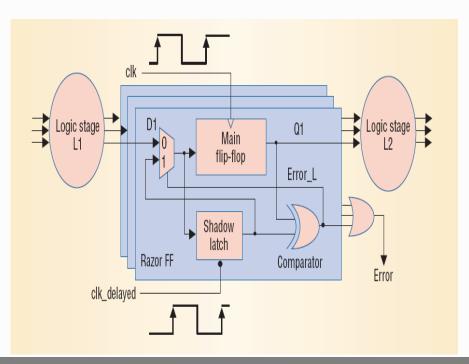

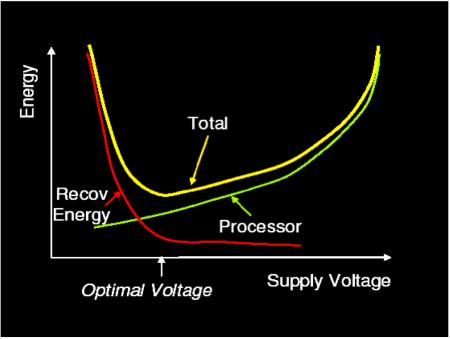

## Razor CMOS

- Shadow latch with delayed clock used to detect and recover setup time violation at high-frequency or low-voltage

- Tune voltage by monitoring error rate to remove voltage margin

- 64b processor implementing subset of Alpha instruction set in 0.18 μm CMOS

- Eliminate V<sub>DD</sub> safety margin, allowing V<sub>DD</sub> to be scaled 120 mV below 1<sup>st</sup> failure point

- 44% energy saving over W.C. conditions @ 0.1% target error rate & 120 MHz

(S. Das, VLSI 2005) page 20

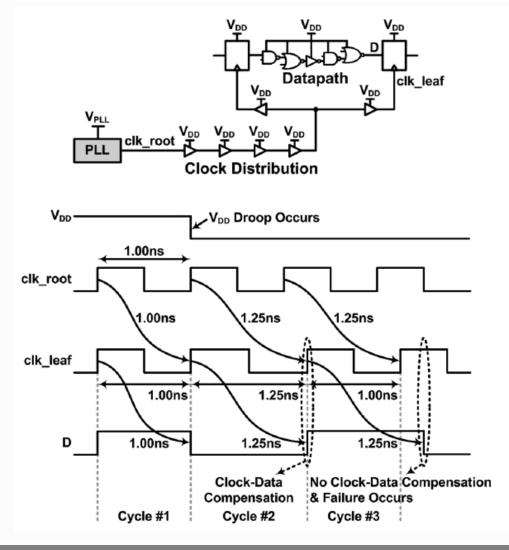

## **Clock Data Compensation**

- Auto Compensation for Cycle 2

- No compensation for Cycle 3

(K. Bowman, JSSC 2016)

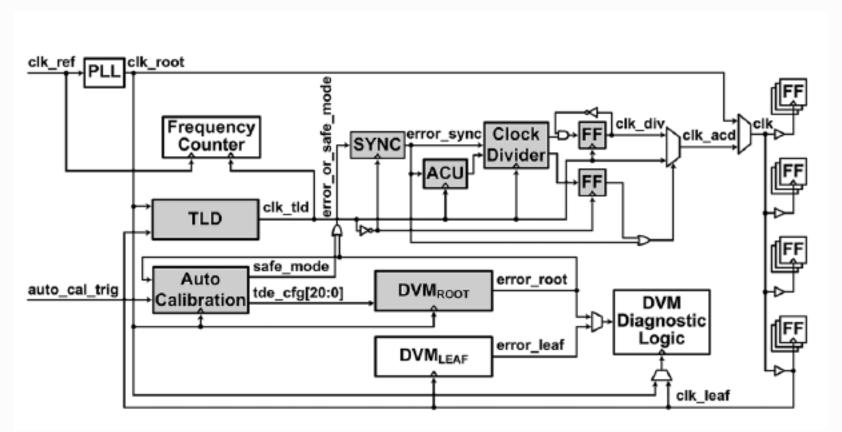

## **Dynamic Voltage Monitor**

- TLD: Determines delay added to clk in case of 'error' detection

- DVM\_root: Detection at the source of the tree

- DVM\_leaf: Detection at the sink of the tree (@ the latches)

(K. Bowman, JSSC 2016) 22

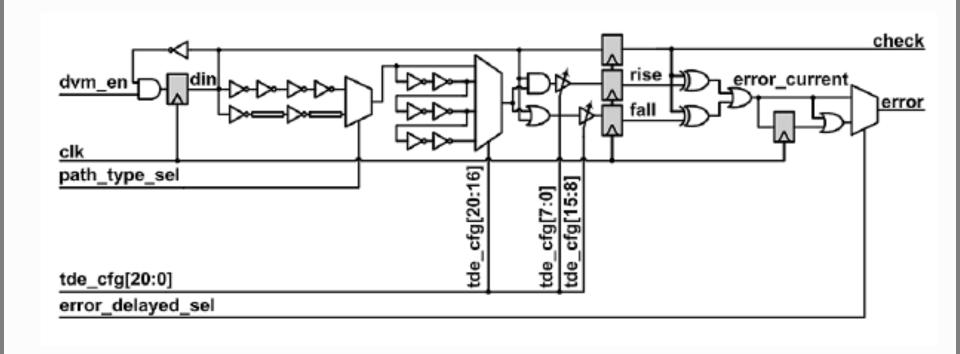

## **Dynamic Voltage Monitor**

- Alternate cycles measure rise and fall transitions

- Can use path selection (similar to CPM)

(K. Bowman, JSSC 2016)

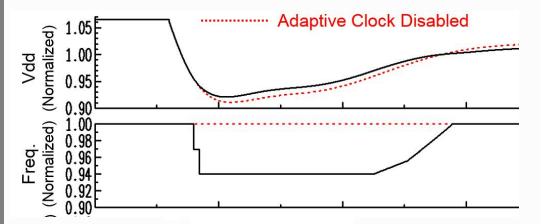

## **Adaptive Clock Solution**

- 1. Detect voltage droop

- 2. Respond with immediate action

- 3. Recover quickly after droop subsides

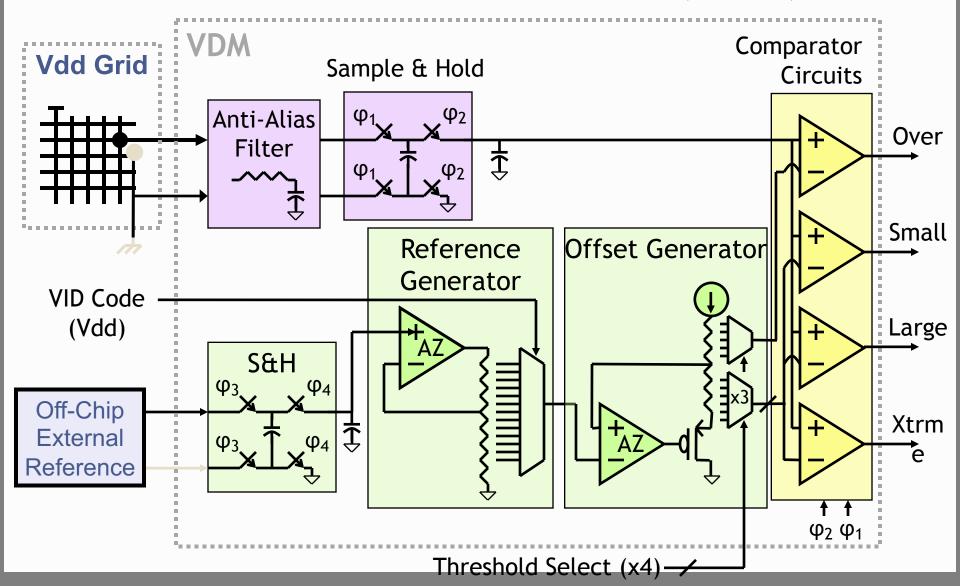

# Voltage Droop Monitor (VDM)

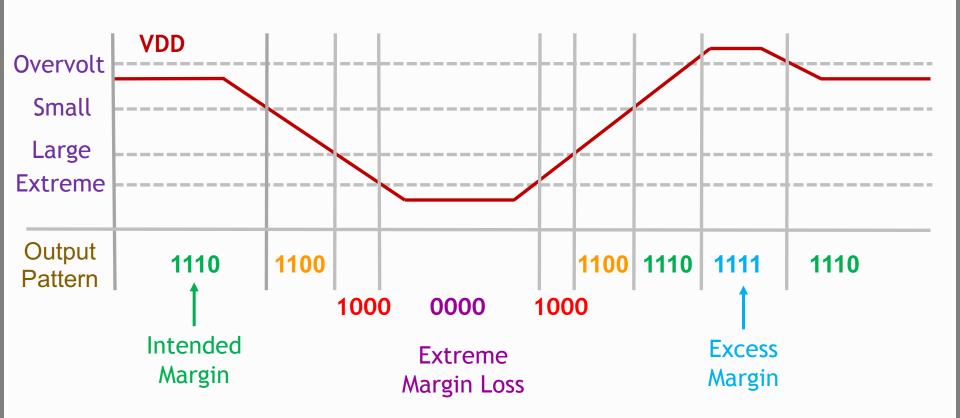

### **VDM Behavior**

Digital output response to analog input voltage (thermometer code)

## Respond

- DPLL immediate frequency reduction

- "jump" almost instantly to protect timing margin

- cleanly without extra clock jitter or noise

- Key = Core frequency is not locked to chip

- digital PLL = adjustment per Quad group of cores

- frequency of each Quad is asynchronous to rest of the POWER9 processor chip

# Digitally controlled Oscillator (DCO)

Constantly calculate number of active devices to remove in response to droop events

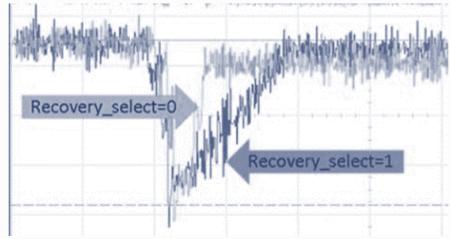

## **Droop Recovery Technique**

### 1. Recover DCO setting

- either gradually or instantly (modeable)

- to prevent frequency overshoot, fewer devices are added back initially

## 2. Restore nominal frequency filter multiplier

- normal DPLL dynamics complete the restoration

- naturally slews and locks to the original target

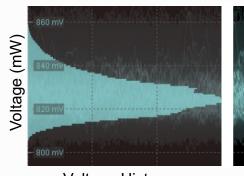

#### **Adaptive Clocking**

Voltage Histogram

V<sub>dd</sub> Noise

- Provides 50% noise margin reduction

- Reduces power up to 8%