# INVESTIGATION OF HYBRID FILTER BANK BASED ANALOG-TO-DIGITAL CONVERSION

A THESIS

submitted by

### **RAJESH INTI**

for the award of the degree

of

### **MASTER OF SCIENCE**

(by Research)

## DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY, MADRAS.

**NOV 2007**

## THESIS CERTIFICATE

This is to certify that the thesis titled **INVESTIGATION OF HYBRID FILTER BANK BASED ANALOG-TO-DIGITAL CONVERSION**, submitted by **RAJESH INTI**, to the Indian Institute of Technology, Madras, for the award of the degree of **Master of Science**, is a bona fide record of the research work done by him under our supervision. The contents of this thesis, in full or in parts, have not been submitted to any other Institute or University for the award of any degree or diploma.

#### Prof. Y. SHANTHI PAVAN

Research Guide Assistant Professor Dept. of Electrical Engineering IIT-Madras, 600 036

Place: Chennai

Date: 3<sup>rd</sup> Dec, 2007

## ACKNOWLEDGEMENTS

At the outset, I am grateful to Dr. Y. Shanthi Pavan, my project advisor, for his valuable guidance throughout the entire duration of my project work. His approach to teaching the operation of analog circuits has always amazed me.

Dr. Nagendra Krishnapura introduced me to the area of VLSI data conversion circuits through his course EE658. His emphasis on Pipeline A/D converters during this course helped me a lot during the design phase. I have also learnt a lot about Linux system administration from him. I would like to thank Dr. David Koilpillai and Dr. Babu Viswanathan for taking time off their busy schedules to serve as my GTC members.

Among my lab mates, I will for a long time, cherish the company of Laxminidhi, Srini, Reddy, Murali, T. Rajesh, Nanda Govind, MNV Prasad and Prabu Sankar. TI lab has always been a real great place of work and fun. Special thanks to Laxminidhi for all his help with populating the PCB.

Finally I dedicate this thesis to my parents for their understanding, patience and encouragement through all these years. This work would not have been possible without their support.

## ABSTRACT

High sampling rate and high resolution analog-to-digital converters (ADCs) are required in a variety of applications, like wide band radio receivers, oscilloscopes and spectrum analyzers. Sample rates of hundreds of MSamples/sec and 10-12 bits of resolution is desirable. Traditionally, high speed converters have been implemented using time interleaving techniques, where an array of converters are used to sample the input data using skewed clocks. Circuit non-idealities like the deviation of skew between clocks from their intended value, gain and offset error in the ADC degrade the performance of this class of converters.

To circumvent the aforementioned problems in time interleaved converters, a hybrid filter bank (HFB) based approach is investigated in this thesis. In the HFB approach, all the converters sample using a single clock, but the input to each of these converters is separated in frequency domain by using continuous time analog filters. One way of separating the input signal in the frequency domain was proposed by Velazquez [Ve-lazquez *et al.* (1998)]. In Velazquez's implementation, analog filters with a very sharp roll off were used mandating high order analog filters. Since integrating high order analog filters is a challenge in itself, we investigate the use of simpler filter transfer functions for signal separation. A 2-channel HFB with 10-bit resolution sampling at 80 MSamples/sec was designed in AMS (Austria Microsystems) 0.35  $\mu$ m CMOS process. The IC was fabricated and characterized. Measured results are presented.

## TABLE OF CONTENTS

| ACKN   | OWLEI  | OGEMENTS                                                      | i   |

|--------|--------|---------------------------------------------------------------|-----|

| ABSTR  | ACT    |                                                               | ii  |

| LIST O | F TABI | LES                                                           | vii |

| LIST O | F FIGU | JRES                                                          | xi  |

| СНАР   | TER 1  | INTRODUCTION                                                  | 1   |

| 1.1    | Motiva | ation                                                         | 1   |

| 1.2    | Organi | ization                                                       | 2   |

| CHAP'  | TER 2  | ADC PERFORMANCE METRICS                                       | 4   |

| 2.1    | Analog | g-to-Digital Converter (ADC)                                  | 4   |

|        | 2.1.1  | Resolution (N)                                                | 5   |

|        | 2.1.2  | Sampling rate $(f_s)$                                         | 5   |

|        | 2.1.3  | Integral Nonlinearity (INL) / Differential Nonlinearity (DNL) | 5   |

|        | 2.1.4  | THD, SFDR, SNR, SNDR                                          | 6   |

|        | 2.1.5  | Effective number of bits (ENOB)                               | 8   |

|        | 2.1.6  | Figure of Merit (FOM)                                         | 8   |

| 2.2    | Charac | cterization techniques                                        | 9   |

|        | 2.2.1  | Static characteristics INL / DNL                              | 9   |

|        | 2.2.2  | Dynamic characteristics SNDR / SNR / SFDR / THD               | 10  |

| СНАР   | TER 3  | FILTER BANK BASED A/D CONVERSION                              | 11  |

| 3.1    | Time-  | Interleaving based A/D conversion                             | 11  |

| 3.2    | Hybric | d Filter Bank based A/D conversion                            | 12  |

| 3.3    | System | n level design aspects of a HFB based ADC                     | 14  |

|        | 3.3.1  | Operation of the M-channel HFB                                | 14  |

|      | 3.3.2   | Two-channel HFB                                                                 | 16 |

|------|---------|---------------------------------------------------------------------------------|----|

|      | 3.3.3   | System specifications                                                           | 17 |

| 3.4  | Maxim   | um achievable SFDR in a 2-channel HFB system                                    | 18 |

| 3.5  | Choice  | of Optimal Analysis filters                                                     | 19 |

| 3.6  | Compu   | ting the Synthesis filters                                                      | 20 |

|      | 3.6.1   | Delay optimization by minimizing energy loss due to synthesis filter truncation | 20 |

|      | 3.6.2   | Synthesis filters satisfying the LMSE criterion for white noise input           | 21 |

|      | 3.6.3   | SNR degradation in HFB based ADCs                                               | 23 |

| CHAP | FER 4   | DESIGN OF A 10-BIT, 40 MSPS PIPELINE ADC                                        | 27 |

| 4.1  | Archite | ecture of the pipelined ADC                                                     | 27 |

| 4.2  | MDAC    | Stage input-output characteristics                                              | 29 |

| 4.3  | Design  | of MDAC stage                                                                   | 31 |

|      | 4.3.1   | Arriving at the opamp specifications                                            | 31 |

|      | 4.3.2   | Opamp topology                                                                  | 32 |

|      | 4.3.3   | Design of the telescopic opamp                                                  | 34 |

|      | 4.3.4   | Design of the gain boosting amplifiers - nMOS folded cascode opamp              | 35 |

|      | 4.3.5   | Design of the gain boosting amplifiers - pMOS folded cascode opamp              | 36 |

|      | 4.3.6   | Biasing the opamp                                                               | 37 |

|      | 4.3.7   | Common-mode feedback loop                                                       | 39 |

|      | 4.3.8   | Opamp noise analysis                                                            | 40 |

|      | 4.3.9   | Summary of simulated results                                                    | 41 |

|      | 4.3.10  | Design of bootstrapped sampling switches                                        | 41 |

|      | 4.3.11  | Comparator design                                                               | 42 |

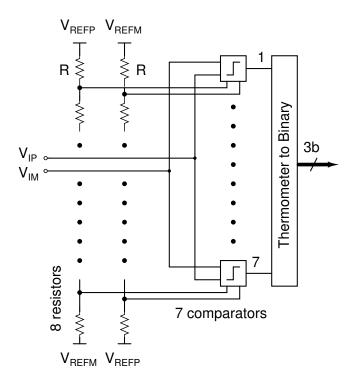

| 4.4  | Design  | of a 3-bit Flash ADC                                                            | 46 |

|      | 4.4.1   | Flash comparator design                                                         | 47 |

|      | 4.4.2   | Thermometer to binary converter                                                 | 49 |

| 4.5  | Digital | error correction (DEC)                                                          | 49 |

| 4.6  | Clock g | generator design                                                                | 52 |

| 4.7  | Voltag  | e references                                                                    | 53 |

|------|---------|---------------------------------------------------------------------------------|----|

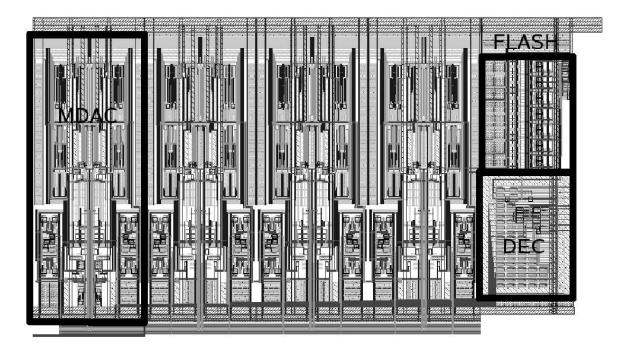

|      | 4.7.1   | MDAC stage Layout                                                               | 54 |

|      | 4.7.2   | Pipelined ADC Layout                                                            | 55 |

| 4.8  | Simula  | ation results for the entire 10-bit ADC                                         | 55 |

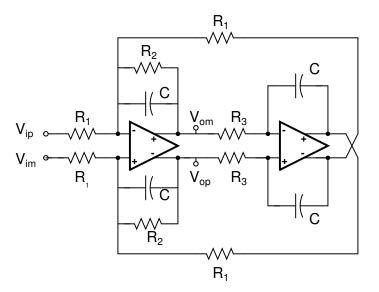

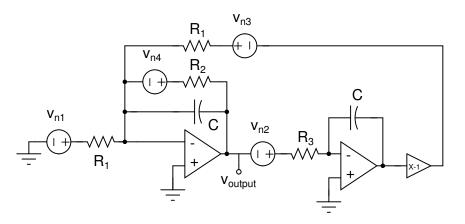

| СНАР | TER 5   | FILTER DESIGN                                                                   | 57 |

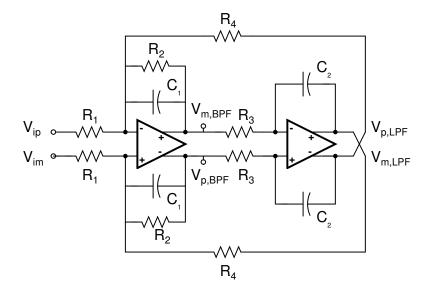

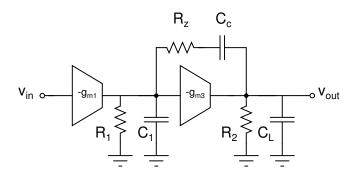

| 5.1  | Biqua   | d topology                                                                      | 57 |

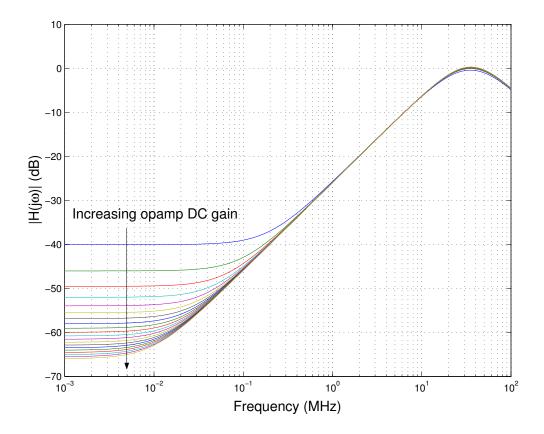

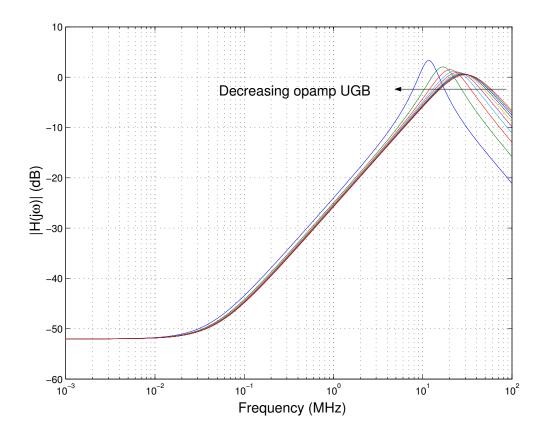

| 5.2  | Arrivi  | ng at the opamp specifications                                                  | 58 |

| 5.3  | Opam    | p topology                                                                      | 59 |

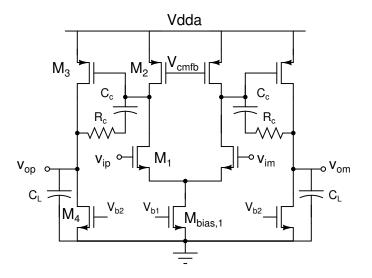

|      | 5.3.1   | Common mode feedback loop                                                       | 62 |

| 5.4  | Biqua   | d implementation                                                                | 64 |

| 5.5  | Procee  | lure for obtaining the integrating R,C values                                   | 64 |

| 5.6  | Integra | ated noise at the filter output                                                 | 68 |

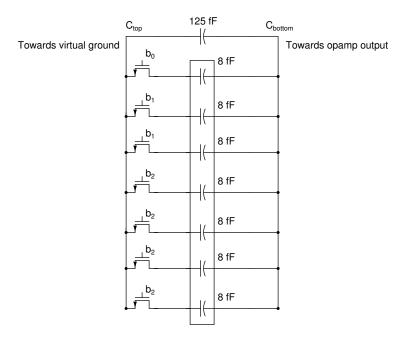

| 5.7  | Tuning  | g the center frequency $f_c$ of the biquad $\ldots \ldots \ldots \ldots \ldots$ | 68 |

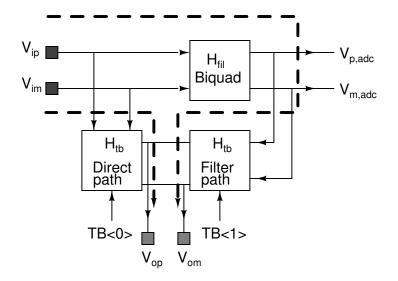

| 5.8  | Measu   | rement of the frequency response                                                | 70 |

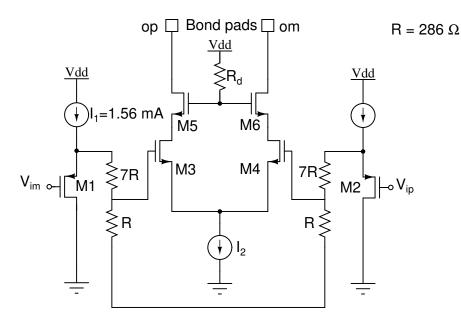

|      | 5.8.1   | Test buffer design                                                              | 71 |

|      | 5.8.2   | Simulation results                                                              | 72 |

|      | 5.8.3   | BPF Layout                                                                      | 75 |

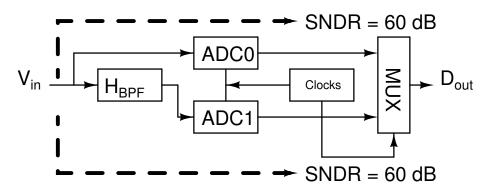

| 5.9  | System  | n integration                                                                   | 76 |

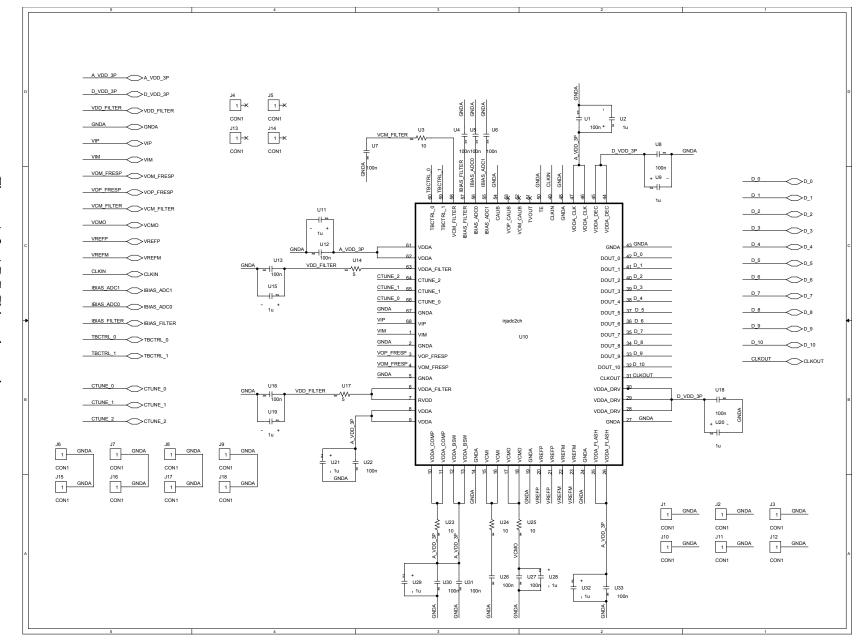

| СНАР | TER 6   | PCB DESIGN AND IC CHARACTERIZATION                                              | 78 |

| 6.1  | PCB [   | Design                                                                          | 78 |

| 6.2  | IC Cha  | aracterization                                                                  | 80 |

| 6.3  | Charao  | cterization of the sub band ADC                                                 | 80 |

|      | 6.3.1   | DNL/INL using histogram technique                                               | 80 |

|      | 6.3.2   | SNR/SNDR measurement                                                            | 84 |

| 6.4  | Charac  | cterization of the Bandpass filter (BPF)                                        | 85 |

|      | 6.4.1   | Frequency response of the BPF                                                   | 85 |

|      | 6.4.2   | Distortion of the BPF                                                           | 85 |

|      | 6.4.3   | IIP3 characterization of the BPF                                                | 86 |

| 6.5  | Proble  | ems encountered during IC characterization                                      | 87 |

| 6.6  | HFB s   | system characterization.                                                        | 88 |

|      |         |                                                                                 |    |

| CHAPTER 7 |        | DEBUG OF ERROR SOURCES IN THE PROTOTYPE                                                   | 92  |

|-----------|--------|-------------------------------------------------------------------------------------------|-----|

| 7.1       | Explai | ining missing codes in pipeline ADC at 10-bit level                                       | 92  |

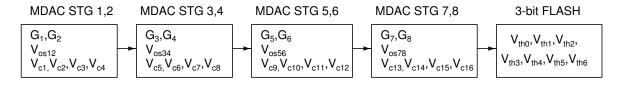

|           | 7.1.1  | MDAC stage parameters (gain, opamp offset, comparator off-<br>set)                        | 92  |

|           | 7.1.2  | ADC model parameters (gain, opamp offset, comparator offset, flash comparator thresholds) | 93  |

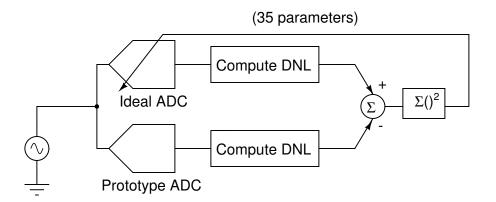

|           | 7.1.3  | Estimating ADC model parameters                                                           | 94  |

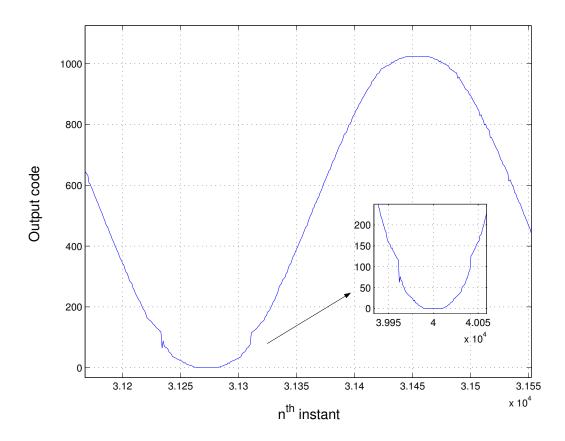

|           | 7.1.4  | Missing codes in the IC prototype                                                         | 94  |

| 7.2       | BPF o  | ffset and its effect on distortion                                                        | 98  |

|           | 7.2.1  | Input referred offset of the opamp                                                        | 100 |

| CHAP      | FER 8  | CONCLUSIONS                                                                               | 101 |

| 8.1       | Work   | done                                                                                      | 101 |

| 8.2       | Furthe | er work                                                                                   | 101 |

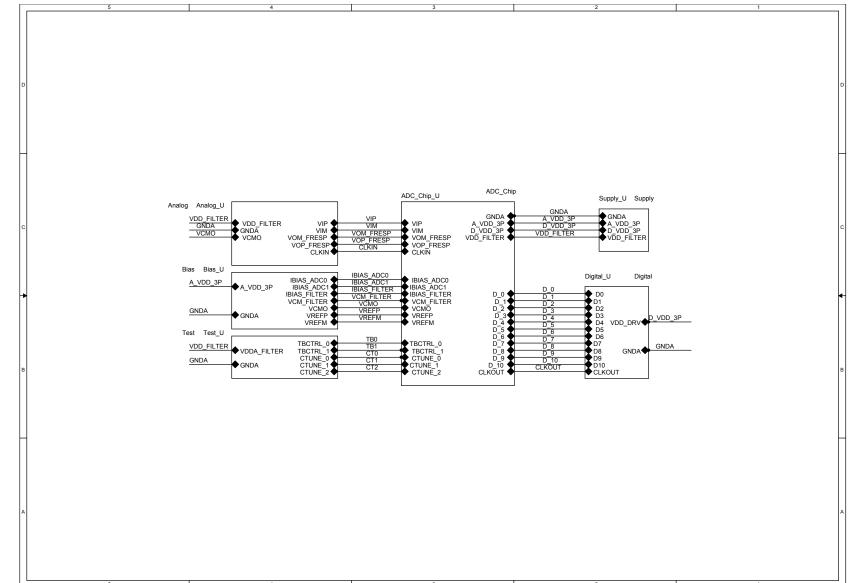

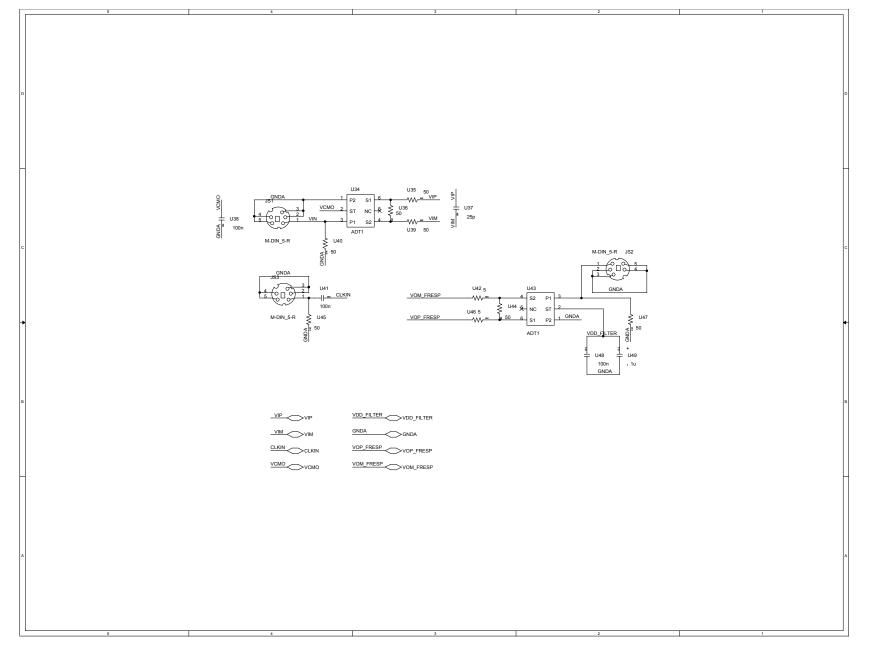

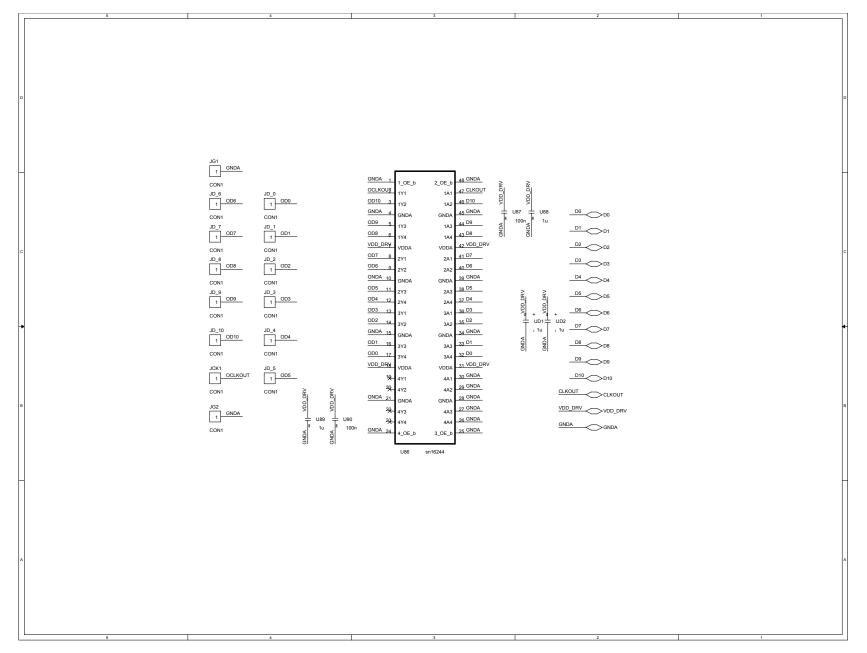

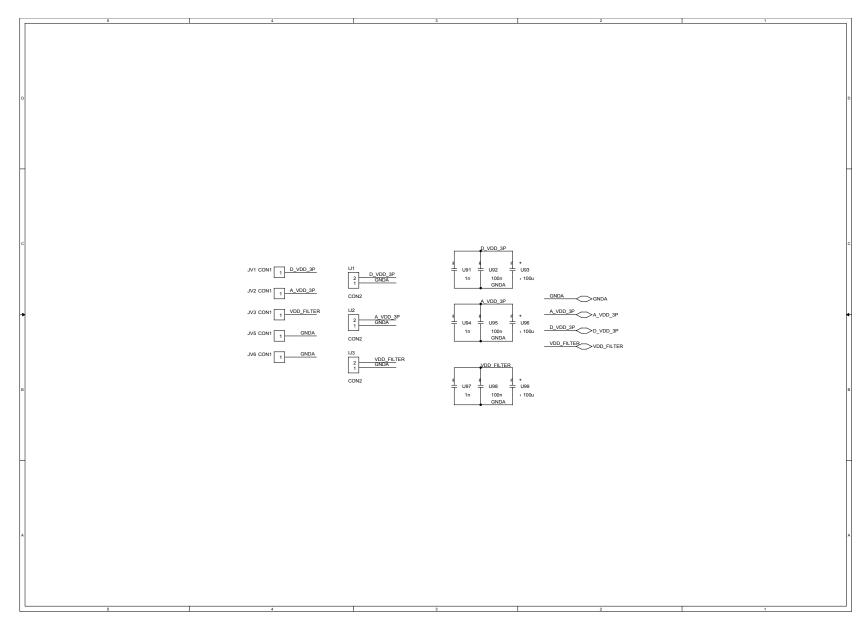

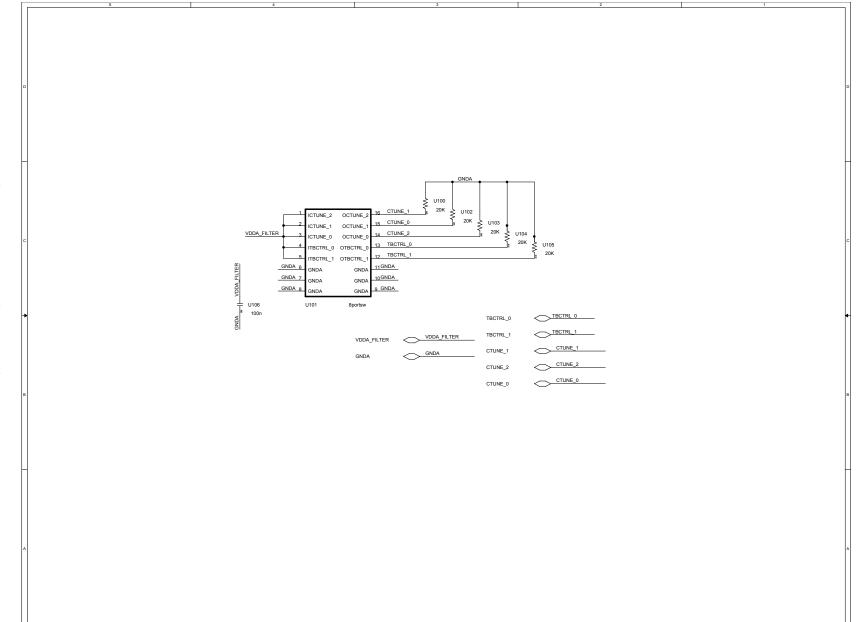

| CHAP      | FER A  | PCB DESIGN SCHEMATICS                                                                     | 102 |

| A.1       | PCB I  | Design                                                                                    | 102 |

|           | A.1.1  | ADC Chip schematic                                                                        | 102 |

|           | A.1.2  | Analog inputs & outputs schematic                                                         | 103 |

|           | A.1.3  | Bias & References inputs schematic                                                        | 103 |

|           | A.1.4  | Digital Buffer schematic                                                                  | 103 |

|           | A.1.5  | Supply input & Bypass capacitors schematic                                                | 104 |

|           | A.1.6  | Test logic schematic                                                                      | 104 |

## LIST OF TABLES

| 3.1 | Achievable SFDR in a 2-channel HFB measured at $\frac{f_{in}}{f_s} = \frac{7371}{8192}$ | 18 |

|-----|-----------------------------------------------------------------------------------------|----|

| 3.2 | SNR results on a 2-channel HFB                                                          | 26 |

| 4.1 | Achieved open loop response of the telescopic cascode opamp                             | 35 |

| 4.2 | Transistor sizes of the nMOS folded cascode opamp                                       | 36 |

| 4.3 | Achieved open loop response of nMOS folded cascode opamp                                | 36 |

| 4.4 | Transistor sizes of the pMOS folded cascode opamp                                       | 37 |

| 4.5 | Achieved open loop response of pMOS folded cascode opamp                                | 37 |

| 4.6 | Achieved open loop response                                                             | 41 |

| 4.7 | Corner simulations                                                                      | 56 |

| 4.8 | Pipeline ADC simulated results                                                          | 56 |

| 5.1 | Transistor sizes and operating point.                                                   | 62 |

| 5.2 | Achieved specifications                                                                 | 62 |

| 5.3 | Transistor sizes and operating point of the CMFB loop                                   | 62 |

| 5.4 | Noise contribution                                                                      | 69 |

| 5.5 | Transistor sizes and Operating point of the Test buffer                                 | 71 |

| 5.6 | Achieved specifications                                                                 | 72 |

| 5.7 | $HD_3$ for 2 $V_{pp}$ input signal                                                      | 73 |

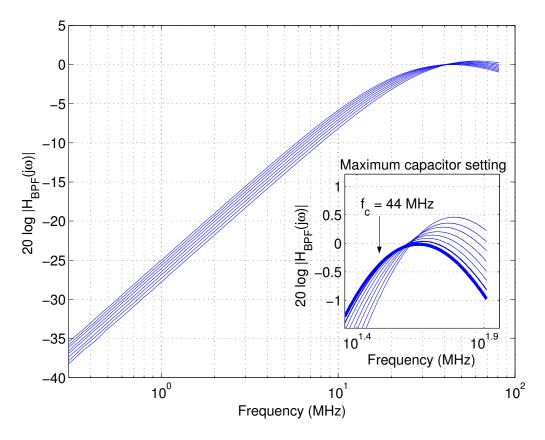

| 6.1 | Center frequency $f_c$ , Gain at $f_c$ for various capacitor settings                   | 86 |

| 6.2 | Distortion measurement                                                                  | 86 |

| 7.1 | Effect of opamp offsets                                                                 | 99 |

## **LIST OF FIGURES**

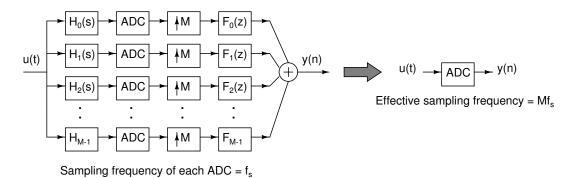

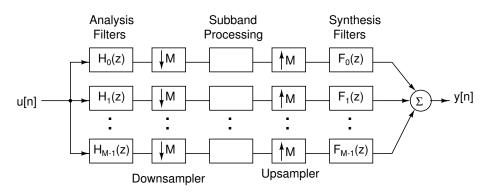

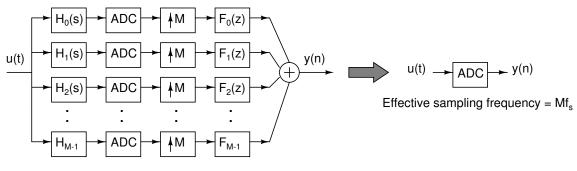

| 1.1  | Velazquez's M-channel HFB implementation                                                  | 2  |

|------|-------------------------------------------------------------------------------------------|----|

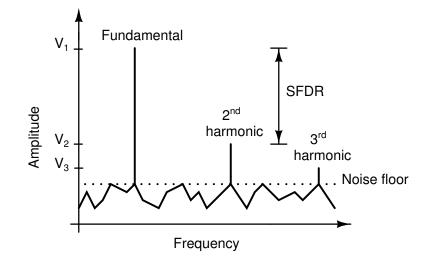

| 2.1  | Spectrum of the output of an ADC to a single-tone input                                   | 7  |

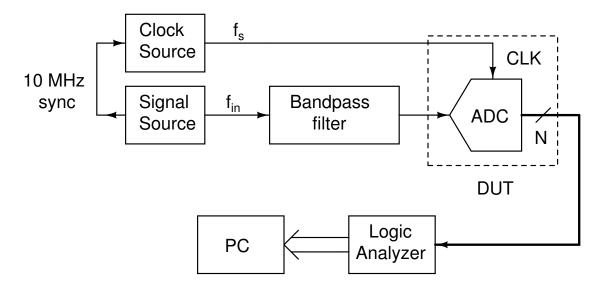

| 2.2  | Setup for characterizing an ADC                                                           | 9  |

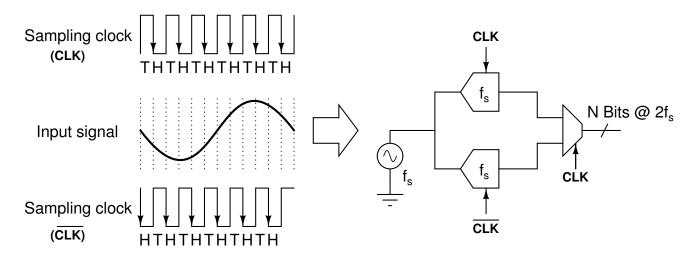

| 3.1  | 2-channel time interleaved ADC                                                            | 12 |

| 3.2  | M-channel discrete-time filter bank                                                       | 13 |

| 3.3  | M-channel HFB based ADC                                                                   | 14 |

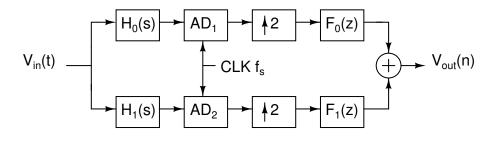

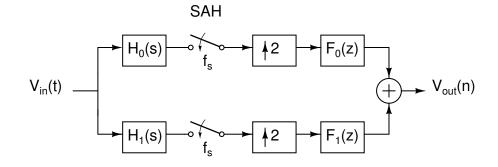

| 3.4  | 2-channel HFB based ADC                                                                   | 17 |

| 3.5  | Setup to measure SFDR in a 2-channel HFB based ADC                                        | 18 |

| 3.6  | 2 channel HFB analysis filters                                                            | 20 |

| 3.7  | 2 channel HFB synthesis filters for 32-tap filters                                        | 21 |

| 3.8  | Synthesis filter identification using LMSE criteria                                       | 22 |

| 3.9  | Computing SNR at the output in a 2-channel HFB based ADC                                  | 23 |

| 3.10 | Interpolation by factor 2                                                                 | 24 |

| 3.11 | Effect of filtering on $S_{v,qn,up}(e^{j\omega})$                                         | 25 |

| 3.12 | SNR simulation for a 2-channel HFB realized using "All pass & Bi-<br>quad" analog filters | 26 |

| 4.1  | Architecture of a generic pipelined ADC                                                   | 27 |

| 4.2  | Architecture of the 10-bit pipelined ADC                                                  | 28 |

| 4.3  | Important sub-blocks in a MDAC stage                                                      | 29 |

| 4.4  | MDAC stage input-output characteristic                                                    | 30 |

| 4.5  | Opamp shared MDAC stage                                                                   | 30 |

| 4.6  | MDAC stage opamp architecture                                                             | 33 |

| 4.7  | Telescopic opamp without the gain boosting amplifiers                                     | 34 |

| 4.8  | nMOS folded cascode gain boosting amplifier                                               | 35 |

| 4.9  | pMOS folded cascode gain boosting amplifier                                               | 37 |

| 4.10 | Biasing - Generation of vcmi, nbias4                                                      | 38 |

| 4.11 | Biasing - Generation of pbias1                                         | 38 |

|------|------------------------------------------------------------------------|----|

| 4.12 | Biasing - Generation of pbias2, nbias3                                 | 39 |

| 4.13 | Switched capacitor CMFB                                                | 39 |

| 4.14 | Equivalent circuit for noise analysis                                  | 40 |

| 4.15 | Schematic of bootstrapped switch                                       | 42 |

| 4.16 | Output spectrum of the bootstrapped switch                             | 43 |

| 4.17 | Nakagome charge pump output                                            | 43 |

| 4.18 | MDAC stage comparator                                                  | 44 |

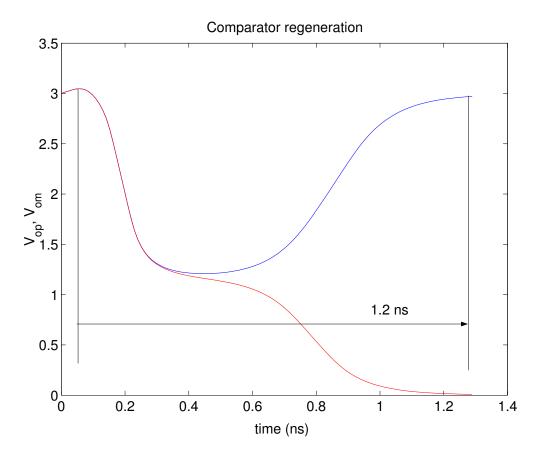

| 4.19 | MDAC stage comparator regeneration                                     | 45 |

| 4.20 | Latch signal timing                                                    | 45 |

| 4.21 | 3-bit Flash architecture                                               | 46 |

| 4.22 | Flash comparator                                                       | 48 |

| 4.23 | Equivalent circuit for latch offset calculation                        | 48 |

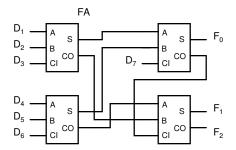

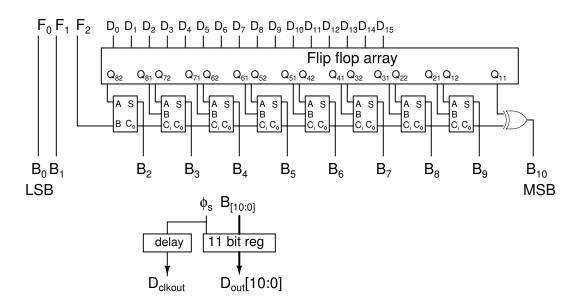

| 4.24 | Thermometer to binary converter for 3-bit Flash ADC                    | 49 |

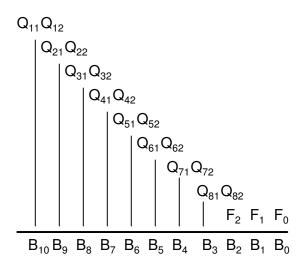

| 4.25 | Signal flow in the DEC block                                           | 50 |

| 4.26 | DEC addition algorithm                                                 | 51 |

| 4.27 | DEC addition                                                           | 51 |

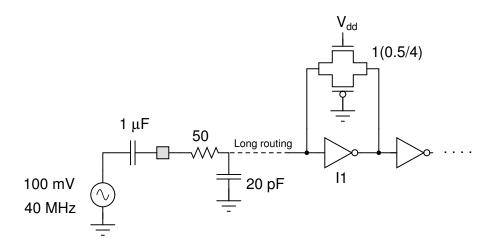

| 4.28 | Converting sine wave clock to square wave                              | 52 |

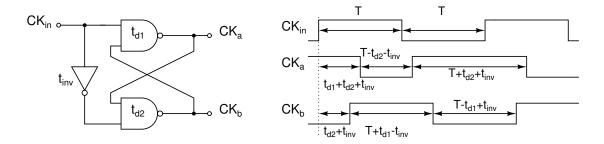

| 4.29 | Non-overlapping clock generator                                        | 53 |

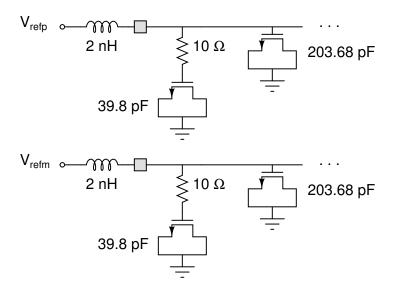

| 4.30 | Bypass capacitor on external voltage references                        | 53 |

| 4.31 | Layout of the MDAC stage                                               | 54 |

| 4.32 | Layout of the sub band ADC                                             | 55 |

| 4.33 | ADC output spectrum for a 10 MHz input                                 | 56 |

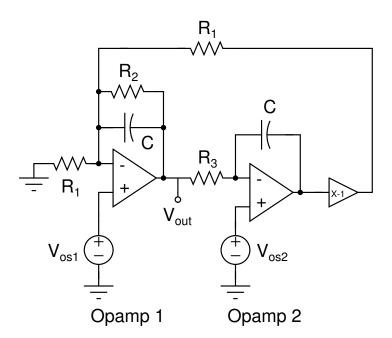

| 5.1  | Biquad schematic                                                       | 58 |

| 5.2  | Variation of stop band response in a biquad with varying opamp DC gain | 59 |

| 5.3  | Variation of stop band response in a biquad with varying opamp UGB     | 60 |

| 5.4  | Opamp topology used in the biquad realization                          | 61 |

| 5.5  | Small signal equivalent showing pole-zero compensation                 | 61 |

| 5.6  | Common mode feedback loop                                              | 63 |

| 5.7  | Common mode feedback loop stability                                    | 63 |

| 5.8  | Biquad schematic                                                     | 64 |

|------|----------------------------------------------------------------------|----|

| 5.9  | Opamp and its small signal equivalent circuit                        | 66 |

| 5.10 | Ideal, Obtained responses after $[R_1, R_2, R_3, C]$ optimization    | 67 |

| 5.11 | Noise contributors                                                   | 68 |

| 5.12 | Capacitor tuning                                                     | 69 |

| 5.13 | Tunable frequency response. Simulated $f_c$ ranges from 33 to 48 MHz | 70 |

| 5.14 | Setup for measuring frequency response of the biquad                 | 71 |

| 5.15 | Test buffer schematic                                                | 72 |

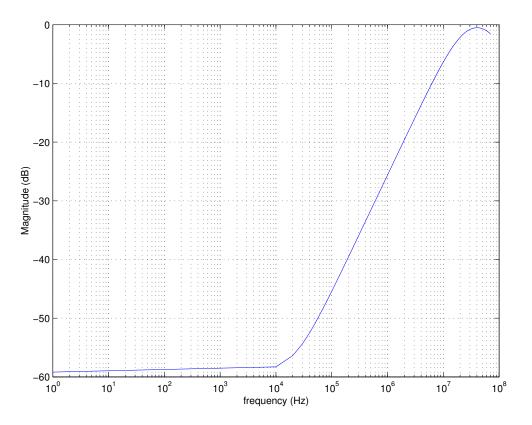

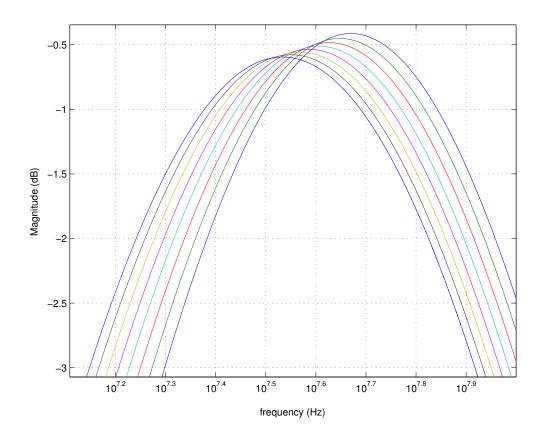

| 5.16 | Frequency response. Simulated $f_c = 10^{7.605} = 40.27 \text{ MHz}$ | 73 |

| 5.17 | Passband details                                                     | 74 |

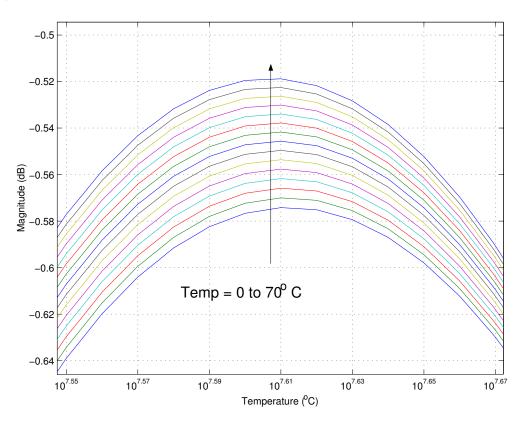

| 5.18 | Frequency response variation across temperature                      | 74 |

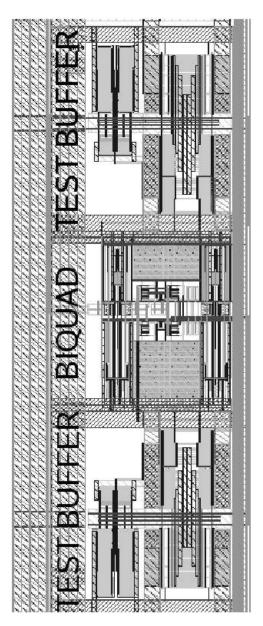

| 5.19 | Layout of the BPF                                                    | 75 |

| 5.20 | 2-channel HFB system                                                 | 76 |

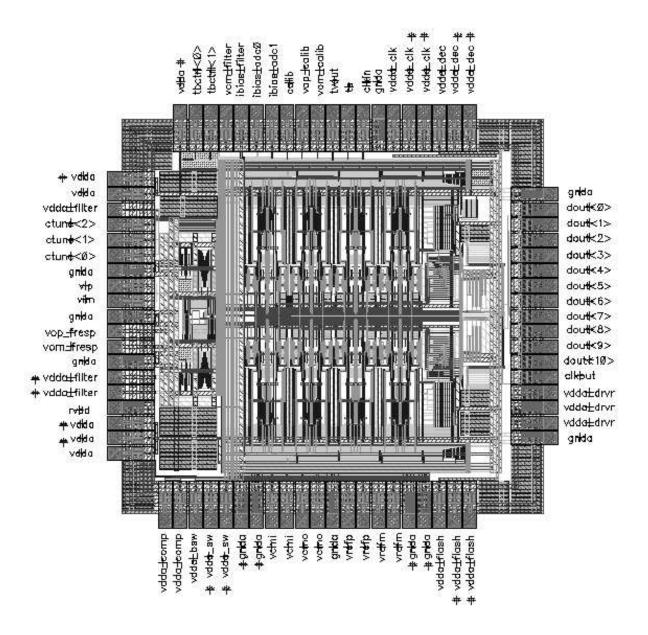

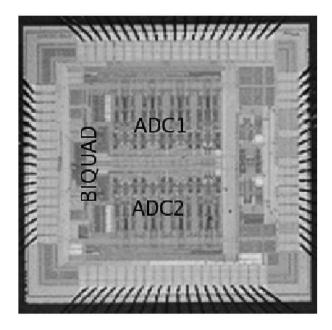

| 5.21 | 2-channel HFB ADC layout.                                            | 77 |

| 6.1  | Die photograph                                                       | 78 |

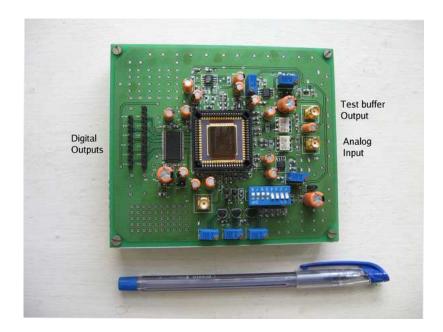

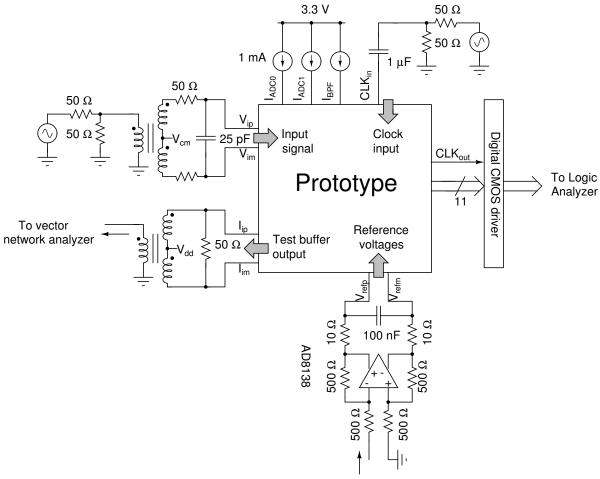

| 6.2  | PCB designed for prototype characterization                          | 79 |

| 6.3  | PCB top level schematic                                              | 79 |

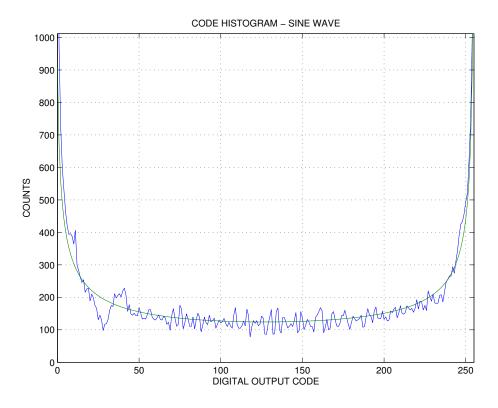

| 6.4  | Output histogram for full scale input at 20 MHz sampling rate        | 81 |

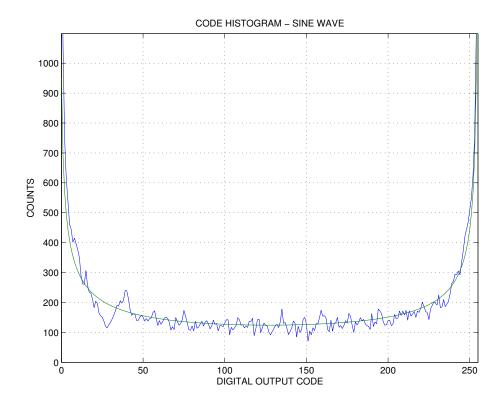

| 6.5  | Output histogram for full scale input at 40 MHz sampling rate        | 81 |

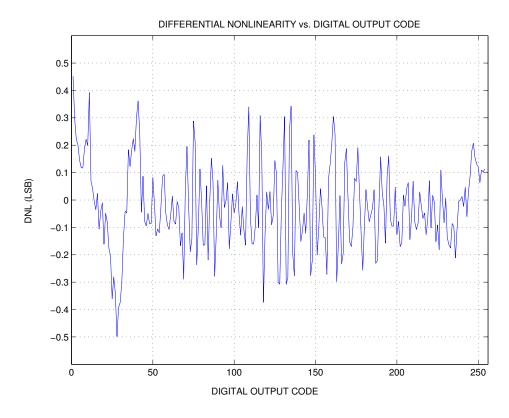

| 6.6  | DNL plot for full scale input at 20 MHz sampling rate                | 82 |

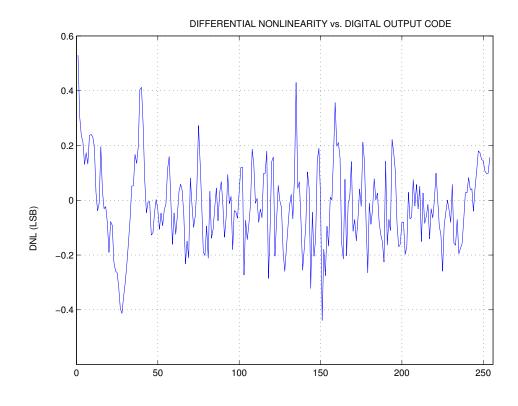

| 6.7  | DNL plot for full scale input at 40 MHz sampling rate                | 82 |

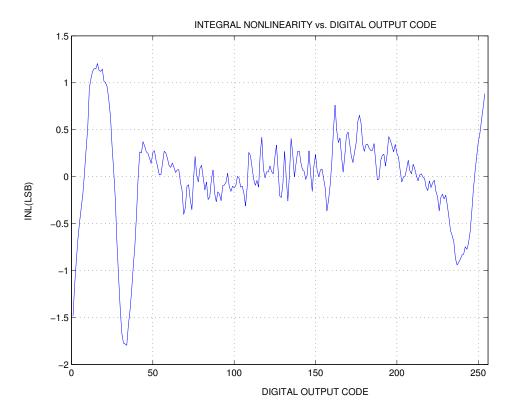

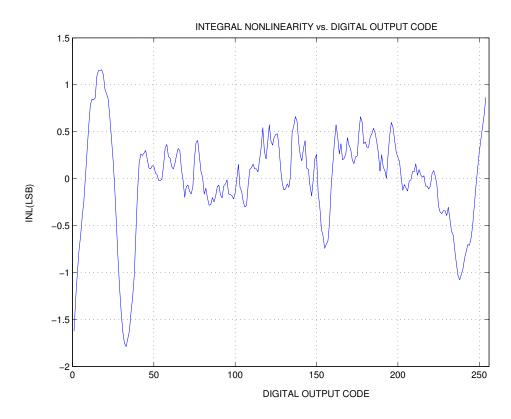

| 6.8  | INL plot for full scale input at 20 MHz sampling rate                | 83 |

| 6.9  | INL plot for full scale input at 40 MHz sampling rate                | 83 |

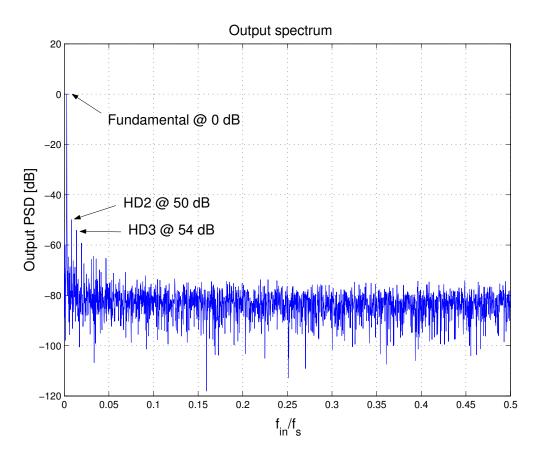

| 6.10 | Output spectrum for Channel 0 ADC using 4K point FFT                 | 84 |

| 6.11 | Frequency response of the bandpass filter for 7 capacitor settings   | 85 |

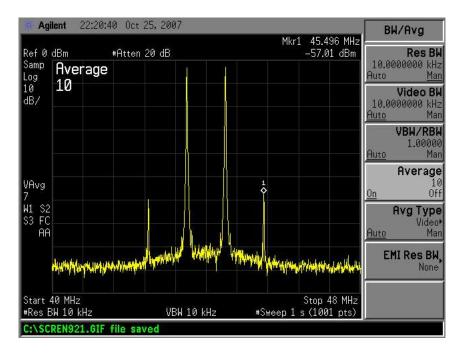

| 6.12 | IIP3 measurement of the filter                                       | 87 |

| 6.13 | Equivalent model at 8-bit accuracy level                             | 89 |

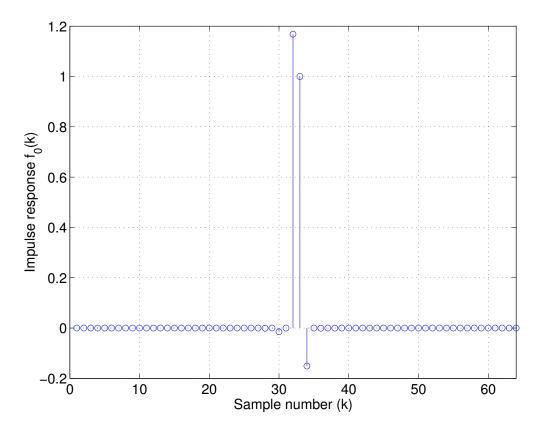

| 6.14 | 64 tap impulse response of $F_0(z)$                                  | 90 |

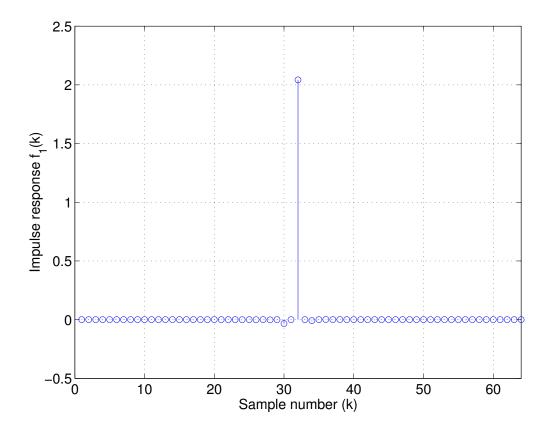

| 6.15 | 64 tap impulse response of $F_1(z)$                                  | 90 |

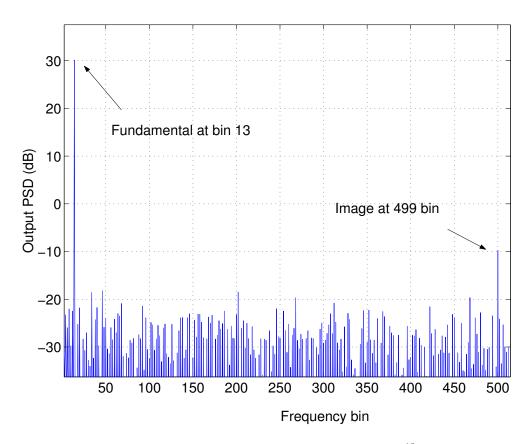

| 6.16 | Output spectrum to input of $f_{in} = \frac{13}{512}f_s$             | 91 |

| 7.1  | 3 MDAC stage parameters that affect the stage characteristic                                                       | 93  |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

| 7.2  | 35 ADC parameters that need to estimated                                                                           | 93  |

| 7.3  | Estimation technique to fit prototype behavior to ideal ADC with pro-<br>grammable parameters using histogram test | 94  |

| 7.4  | Distortion introduced in sine wave in negative cycle only indicative of errors in MDAC comparator thresholds       | 95  |

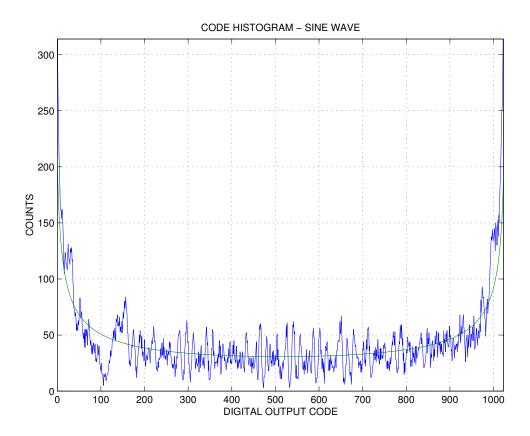

| 7.5  | Measured Histogram at 10-bit level                                                                                 | 95  |

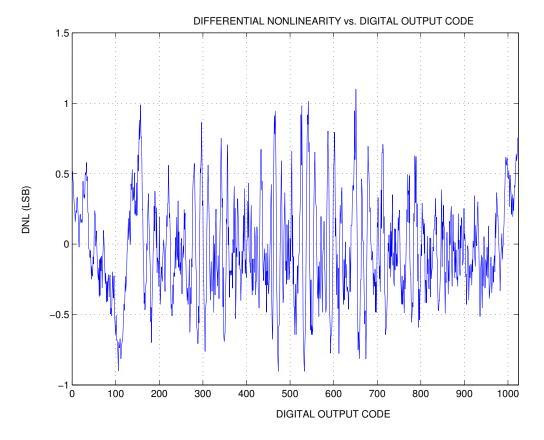

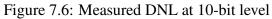

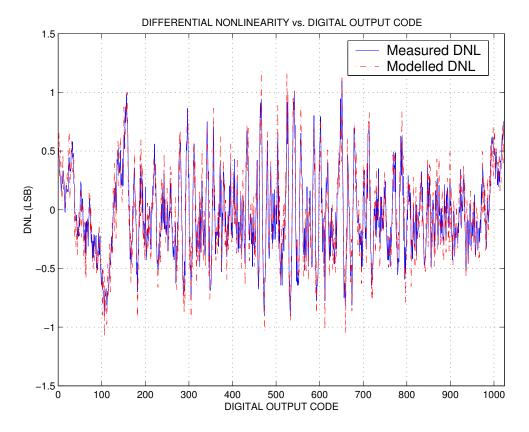

| 7.6  | Measured DNL at 10-bit level                                                                                       | 96  |

| 7.7  | Measured INL at 10-bit level                                                                                       | 96  |

| 7.8  | Measured and Estimated DNL at 10-bit level                                                                         | 97  |

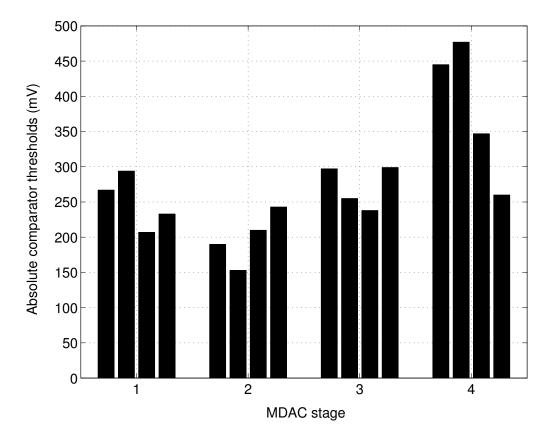

| 7.9  | Absolute comparator thresholds in the 4 MDAC stages                                                                | 98  |

| 7.10 | Effect of input referred opamp offsets                                                                             | 99  |

| 7.11 | Opamp first stage                                                                                                  | 100 |

| A.1  | PCB top level schematic                                                                                            | 105 |

| A.2  | ADC Chip schematic                                                                                                 | 106 |

| A.3  | Analog inputs schematic                                                                                            | 107 |

| A.4  | Bias & References schematic                                                                                        | 108 |

| A.5  | Digital Buffer schematic                                                                                           | 109 |

| A.6  | Supply input & Bypass capacitors schematic                                                                         | 110 |

| A.7  | Test logic schematic                                                                                               | 111 |

## **CHAPTER 1**

### **INTRODUCTION**

#### 1.1 Motivation

Analog-to-Digital Converters (ADCs) are key design blocks in modern communication systems. With tremendous advances in CMOS fabrication technology, most signal-processing functions are being moved to the digital domain for a low power, low cost, high yield and highly reconfigurable implementation. Many communication standards like Bluetooth and IEEE 802.11 a/b require ADCs with a resolution of 8-10 bits sampling at around 10-100 MSamples/sec [Xia *et al.* (2006)].

The achievable sampling rate and resolution of an ADC in a particular technology is dictated by the rate at which switched-capacitor circuits in the ADC can be operated. To achieve higher sampling rates, many ADCs sampling at lower rates can be used in parallel. Exploiting parallelism in A/D conversion can be done either in the time or frequency domains.

Traditionally, high speed converters have been implemented using time interleaving techniques, where an array of converters are used to sample the input data using skewed clocks. Non-idealities in the realization of multiple skewed clocks degrades the performance of this class of converters. To circumvent the problem of multiple clock generation in time interleaved converters, a new technique called hybrid filter bank (HFB) based A/D conversion was proposed in [Velazquez *et al.* (1998)]. As shown in Fig 1.1, the continuous time analog input signal V<sub>in</sub> whose bandwidth is  $\frac{Mf_s}{2}$  is split into M frequency bands with bandwidth  $\frac{f_s}{2}$  using analog continuous time filters  $H_0(s), H_1(s), \dots, H_{M-1}(s)$ . The effective bandwidth of the signal after filtering is only  $\frac{f_s}{2}$ , which is suitable for conversion by  $AD_0, AD_1, \dots, AD_{M-1}$  whose sampling rates are  $f_s$ . FIR filters  $F_0(z), F_1(z), \dots, F_{M-1}(z)$  are used to reconstruct the digitized samples provided by  $AD_0, AD_1, \dots, AD_{M-1}$ . In Velazquez's implementation, analog filters with

Figure 1.1: Velazquez's M-channel HFB implementation

sharp roll off are used mandating higher order analog filters. Designing such high order filters is a challenge in itself. High order filters are also sensitive to component variations. In this work, we will investigate the use of simpler analog filters. We investigate the use of simpler filters to accomplish the task of frequency domain A/D conversion. Specifically, we explore the possibility of building a 10-bit, two channel ADC sampling at 80 MSPS (Mega Samples Per Second) using the frequency domain approach.

#### 1.2 Organization

**Chapter 2** introduces the concepts and terminology in A/D conversion circuits. Dynamic and static characteristics of an ADC are discussed.

**Chapter 3** describes HFB based A/D conversion. The procedure for the design of HFB based ADCs are outlined. Details regarding the design specifications of a 10-bit,

2-channel HFB based 80 MSPS ADC are provided.

**Chapter 4** presents the design of a 10-bit, 40 MSPS pipeline ADC. The design of the multiplying DAC (MDAC) stage, the 3-bit termination Flash ADC and the digital error correction (DEC) logic will be dealt with.

**Chapter 5** gives the design of an opamp-RC based band-pass filter with center frequency at 40 MHz. Techniques employed to measure the frequency response of the on-chip band-pass filter are discussed.

Chapter 6 presents details regarding printed circuit board (PCB) design, prototype IC characterization and measured results.

**Chapter 7** gives the possible reasons for the observed error sources in the prototype IC. The differential nonlinearity (DNL) characteristic has been used to extract information pertaining to the multiplying DAC stages.

Chapter 8 concludes the thesis.

### **CHAPTER 2**

## **ADC PERFORMANCE METRICS**

In this chapter, we review the important metrics involved in the performance measurement of ADCs [AN748 (2001)] like integral/differential nonlinearity (INL/DNL), signal-to-quantization noise ratio (SNR), signal-to-quantization noise+distortion ratio (SNDR), spurious free dynamic range (SFDR), effective number of bits (ENOB) and figure of merit (FOM).

#### 2.1 Analog-to-Digital Converter (ADC)

An ADC converts real time analog signals into digital codes. An ADC has a reference voltage or current against which the analog input is compared. The N-bit digital output word indicates what fraction of the reference quantity  $V_{ref}$  the input quantity  $V_{in}$ is. The input-output transfer function is described by

Output-code

$$D_{\text{out}} = \frac{2^n V_{in}}{V_{ref}}$$

(or)  $\frac{2^N I_{in}}{I_{ref}}$

where N is the number of bits that can be resolved by the ADC,  $V_{in}$  or  $I_{in}$  correspond to the input quantity and  $V_{ref}$  or  $I_{ref}$  correspond to the reference value against which the input will be compared. In the sections henceforth, we will look at the metrics involved in performance characterization of ADCs.

#### 2.1.1 Resolution (N)

The resolution of an ADC is the number of bits in the digital output code. Alternatively, it can be defined as the size of the least significant bit (LSB). In a N-bit ADC, we will have  $2^N$  possible levels. If the full scale range of the ADC is FSR, then

$$1 LSB = \frac{FSR}{2^N}$$

#### **2.1.2** Sampling rate $(\mathbf{f}_s)$

Sampling frequency defines the number of samples per second taken from a continuous signal to obtain a discrete version of the signal. The common notation for sampling frequency is  $f_s$ .

#### 2.1.3 Integral Nonlinearity (INL) / Differential Nonlinearity (DNL)

Each code width (LSB) of an ADC's transfer function should be uniform in size. Deviations of the code width from the ideal value of 1 LSB can be accounted using DNL/INL.

#### **Differential nonlinearity (DNL)**

Ideally, the voltage difference between each code transition should be equal to one LSB. Deviation of each code from an LSB is measured as DNL. For an ideal ADC, in which the differential nonlinearity coincides with DNL = 0 LSB, each analog step equals 1 LSB and the transition values are spaced exactly 1 LSB apart. It is defined as

follows:

$$DNL(n) = \frac{V_{actual}(n) - V_{actual}(n-1)}{LSB} - 1$$

where  $V_{actual}(n)$  is the voltage corresponding to input at which the ADC transitions from code (n-1) to n. A DNL error specification of less than or equal to 1 LSB guarantees a monotonic transfer function with no missing codes. An ADC's monotonicity is guaranteed when its digital output increases (or remains constant) with an increasing input signal. DNL is specified after gain error correction and offset error correction.

#### **Integral nonlinearity (INL)**

Integral Non-linearity, INL, describes the deviation from an ideal linear transfer curve for an ADC . The size and distribution of the DNL errors will determine the integral linearity of the converter. It is defined as follows:

$$INL(n) = \frac{V_{actual}(n) - V_{ideal}(n)}{LSB}$$

#### 2.1.4 THD, SFDR, SNR, SNDR

An ADC's dynamic performance is specified using parameters obtained via spectral analysis and is measured by performing a Discrete Fourier transform (DFT) on the output codes of the ADC. In Fig 2.1, the fundamental frequency is the input signal frequency. This is the signal measured with the ADC. Contributors to noise include harmonic distortion, thermal noise, 1/f noise, and quantization noise. Nonlinearity in

Figure 2.1: Spectrum of the output of an ADC to a single-tone input

the ADC results in harmonic distortion (HD). Such distortion is observed as "spurs" in the FFT at harmonics of the measured signal as showing in Fig 2.1. This distortion is referred to as total harmonic distortion (THD), and its power is calculated using

$$THD = 10 \log \left[ \frac{V_2^2 + V_3^2 + \ldots + V_n^2}{V_1^2} \right] dB$$

Spurious-free dynamic range (SFDR) is the difference between the magnitude of the measured signal and its highest spur peak. This spur is typically a harmonic of the measured signal. SFDR measurement is shown in Fig 2.1.

The signal-to-noise ratio (SNR) is the ratio of the root mean square (RMS) power of the input signal to the RMS noise power (excluding harmonic distortion), expressed in dB. SNR can be computed using,

$$SNR = 20 \log \left[ \frac{V_{signal,rms}}{V_{noise,rms}} \right] \, \mathrm{dB}$$

For a N-bit ADC, the theoretical peak SNR = 6.02N + 1.76 dB for a full-scale sinusoidal

input.

Signal-to-noise plus distortion ratio (SNDR) gives a description of how the measured signal will compare to the noise and distortion. SNDR can be computed using

$$SNDR = 10 \log \left[ \frac{V_1^2}{V_2^2 + V_3^2 + \ldots + V_n^2 + V_{noise}^2} \right] d\mathbf{B}$$

#### 2.1.5 Effective number of bits (ENOB)

SNDR is often converted to effective-number-of-bits (ENOB) using the relationship for the theoretical SNR of an ideal N-bit ADC. It is a measure of the effective resolution of the ADC accounting for quantization noise and distortion.

$$ENOB = \frac{\text{SNDR} - 1.76}{6.02}$$

bits

#### 2.1.6 Figure of Merit (FOM)

FOM is used as an universal measure of ADC performance [Walden (1999)]. It enables us to compare the performances for ADC irrespective of the architecture, effective resolution (ENOB), sampling rate ( $f_s$ ) and power dissipation ( $P_{diss}$ ). It is computed using

$$FOM = \frac{P_{diss}}{2^{ENOB} f_s}$$

#### 2.2 Characterization techniques

Any ADC prototype needs to be characterized to determine its static (INL, DNL) and dynamic (SNR,SNDR, SFDR and THD) specifications. Fig 2.2 shows the setup used for characterization of an ADC. In the sections that follow, techniques that are adopted for static and dynamic characterization are described.

To avoid spectral leakage, the clock and signal input sources should be synchronized. An bandpass/lowpass filter should be used in the signal path to suppress the second and third harmonics corresponding to the input signal, such that the harmonics do not limit the SNR measurement of the device under test (DUT).

Figure 2.2: Setup for characterizing an ADC

#### 2.2.1 Static characteristics INL / DNL

The histogram technique has been widely used for characterizing the static characteristics of an ADC [Doernberg *et al.* (1984), AN2085 (2003)]. This approach, also referred to as the code density test, is performed in the amplitude-domain of a data converter. In a histogram test, a sine-wave signal is applied to the ADC, generating a corresponding distribution of digital codes at the output of the converter. Deviation from the corresponding output code distribution from the ideal distribution is used to estimate the INL/DNL.

#### 2.2.2 Dynamic characteristics SNDR / SNR / SFDR / THD

Typically, single-tone inputs are used to compute the SNDR, SFDR and THD of an ADC prototype. To ensure that the  $2^{nd}$  and  $3^{rd}$  order distortion terms of the signal source does not affect the measurements, the harmonic suppressing filter should be a bandpass filter centered around the input frequency  $f_{in}$  and should provide sufficient attenuation of the distortion components.

### **CHAPTER 3**

### **FILTER BANK BASED A/D CONVERSION**

In this chapter, we briefly review time-interleaving A/D conversion. An alternative architecture i.e. the hybrid filter bank (HFB) based A/D conversion that overcomes the problems with the time-interleaved architecture is discussed. System level design aspects like choice of optimal analysis filters and computing the synthesis filters in a HFB based ADC are provided. The degradation of SNR due to the HFB technique in a generic M-channel ADC is derived.

#### 3.1 Time-Interleaving based A/D conversion

Time interleaving in A/D conversion was introduced in [Black and Hodges (1980)]. Time-interleaved ADC systems employ the concept of running M ADCs at a sample rate that is 1/M of the overall system sample rate. Each channel is clocked at a phase that enables the system as a whole to sample at equally spaced increments of time, imitating the behavior of a single A/D converter sampling at full speed. In a twoconverter example as shown in Fig 3.1, both ADC channels are clocked at one-half of the overall system's sample rate, and are 180° out of phase with one another.

Matching between the individual channels has a direct impact on the dynamic range (DR) performance of a time-interleaved ADC system. Mismatches between the ADC channels result in DR degradation that in the output spectrum (to a single tone sine wave input) show up as spurious frequency components called image spur and offset

spur. The image spur associated with time-interleaved ADC systems are a direct result of gain and phase mismatches between the ADC channels. The offset spur is generated by offset differences between the ADC channels. The offset spur is independent of the input signal unlike the image spur.

Time interleaved ADCs with M-channels require clocks which are separated in phase by  $\frac{360^{\circ}}{M}$  degrees. Clock skew degrades the performance of the system. For a detailed study of the behavior of the gain, phase and offset mismatches in time-interleaved ADC systems, the reader is referred to [Kurosawa *et al.* (2001)].

Figure 3.1: 2-channel time interleaved ADC

#### 3.2 Hybrid Filter Bank based A/D conversion

Filter banks are used in a wide range of communication applications like sub-band coding, digital audio and image coding. The operation operation of a filter bank depicted in Fig 3.2 can be outlined as follows. Assume that the input signal has a bandwidth of  $f_B$ . The analysis filters  $H_k(z)$  channelize the input signal u[n] into M sub-band each with a bandwidth of  $\frac{f_B}{M}$ . The sub-band signals are further down sampled by a factor M. Sub-band processing (operations like coding, compression, quantization etc.) now happens at a rate which is  $\frac{f_B}{M}$ , which is M times smaller than the Nyquist frequency corresponding to u. After sub-band processing, the signal is upsampled by a factor M. Digital interpolation filters are used to generate the output.

Figure 3.2: M-channel discrete-time filter bank

[Petraglia and Mitra (1992)] have reported a discrete-time filter bank based 2-channel ADC. The ADC uses 12-bit successive approximation ADCs sampling at 10 kHz to build a system whose effective sampling rate is 20 kHz. One of the disadvantages of a discrete time implementation is that it requires an up-front sample and hold circuit which operates the systems effective sampling rate i.e. 20 kHz in this example. Implementation of the discrete time analysis filters requires switched capacitor (SC) circuits whose maximum frequency of operation is limited.

Unlike the discrete-time filter bank, the hybrid filter bank (HFB) [Velazquez *et al.* (1998)] uses analog analysis filter  $H_k(s)$  to allocate a frequency band to each ADC in the array and digital synthesis filters  $F_k(z)$  to reconstruct the digitized signal. As will be seen in the sections that follow, HFB improves the speed and resolution of the conversion by attenuating the effects of mismatches between the converters, which would otherwise limit the maximum resolution achievable by the system [Velazquez *et al.* (1998)].

#### 3.3 System level design aspects of a HFB based ADC

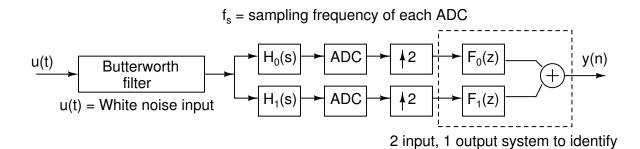

In this section, we will examine a generic M-channel HFB ADC. We assume analog analysis filters  $H_k(s)$  and digital synthesis filters  $F_k(z)$  as shown in the Fig 3.3. The sampling rate of each ADC shown is Fig 3.3 is denoted as is  $f_s$  Hz. The whole system emulates an ADC sampling at  $Mf_s$  Hz.

Sampling frequency of each ADC =  $f_s$

Figure 3.3: M-channel HFB based ADC

#### 3.3.1 Operation of the M-channel HFB

For operation of the M-channel discrete time FB, the reader is referred to [Vaidyanathan (1993)]. In the M-channel HFB case, the outputs after each stage are as shown below -

After each analysis filter:

$$X_k(j\Omega) = U(j\Omega)H_k(j\Omega)$$

where  $\Omega$  denotes the frequency in the continuous-time domain (in radians/sec).

After A/D conversion in each sub-band channel: Using  $\omega = \Omega T_s$

$$V_k(j\omega) = \sum_{m=-\infty}^{m=+\infty} U(j(\omega - 2\pi m)/T_s)H_k(j(\omega - 2\pi m)/T_s)$$

After upsampling by M and the synthesis filter section:

$$W_{k}(j\omega) = \sum_{m=0}^{m=M-1} F_{k}(j\omega)U(j(M\omega - 2\pi m)/T_{s})H_{k}(j(M\omega - 2\pi m)/T_{s})$$

After the summer, the output is:

$$Y(j\omega) = \sum_{k=0}^{k=M-1} \sum_{m=0}^{m=M-1} F_k(j\omega) U(j(M\omega - 2\pi m)/T_s) H_k(j(M\omega - 2\pi m)/T_s)$$

Rearranging the output equation

$$Y(j\omega) = \sum_{m=0}^{m=M-1} U(j(M\omega - 2\pi m)/T_s) \sum_{k=0}^{k=M-1} H_k(j(M\omega - 2\pi m)/T_s)F_k(j\omega)$$

The desired output is  $U(Mj\omega/T_s)$ , which is the input  $U(j\Omega)$  sampled at  $f'_s = Mf_s = \frac{M}{T_s}$ . The components  $U(j(M\omega - 2\pi)/T_s)$ ,  $U(j(M\omega - 4\pi)/T_s) \dots U(j(M\omega - (M-1)\pi)/T_s))$  are the aliasing components. To achieve perfect reconstruction, the scaling functions for the desired output should be a ideal delay element and the aliasing components should be zero. We use the the following definitions for the aliasing and distortion functions.

Distortion function :

$$T_0(j\omega) = \sum_{k=0}^{k=M-1} H_k(Mj\omega/T_s)F_k(j\omega) = Me^{-j\omega d}$$

(3.1)

Aliasing functions :

$$T_m(j\omega) = \sum_{k=0}^{k=M-1} H_k(j(M\omega - 2\pi m)/T_s)F_k(j\omega) = 0 \text{ for } m = 1,2,3... M-1$$

(3.2)

Equations [3.1,3.2] form a set M linear equations which can solved over the frequency range  $0 < \omega \le \pi$  to obtain the frequency response of the synthesis filters for pre-defined set of analysis filters  $H_k(s)$ . Using the standard Matlab **ifft** routine, we can obtain the impulse response for each  $F_k(z)$ .

#### 3.3.2 Two-channel HFB

All our discussions henceforth will be based on the 2-channel HFB. In the sections that ensue, we will look into how to choose the continuous time analog filters  $H_k(s)$ , the computation of filter taps by solving for the synthesis filters  $F_k(z)$ , the maximum achievable SFDR and the SNR at the output of a 2-channel HFB ADC for the chosen analog filters.

The generic 2-channel HFB system shown in Fig 3.4 can be described by

$$\begin{bmatrix} H_0(2j\omega/T_s) & H_1(2j\omega/T_s) \\ H_0(j2(\omega-\pi)/T_s) & H_1(j2(\omega-\pi)/T_s) \end{bmatrix} \begin{bmatrix} F_0(j\omega) \\ F_1(j\omega) \end{bmatrix} = \begin{bmatrix} 2e^{-j\omega d} \\ 0 \end{bmatrix}$$

(3.3)

The synthesis filters  $F_0(z)$  and  $F_1(z)$  can be solved using Eqn 3.3. The variable **d** is the

Figure 3.4: 2-channel HFB based ADC

delay of the system (typically an integer number of clock cycles). It is usually chosen to be approximately equal to half the length of the FIR filter i.e. if each of  $F_k(z)$  are realized using 32 taps then d = 16. The desired distortion and aliasing functions  $T_0$  and  $T_1$  are given by -

$$T_{0}(j\omega) = H_{0}(2j\omega/T_{s})F_{0}(j\omega) + H_{1}(2j\omega/T_{s})F_{1}(j\omega) = 2e^{-j\omega d}$$

$$T_{1}(j\omega) = H_{0}(2j(\omega - \pi)/T_{s})F_{0}(j\omega) + H_{1}(2j(\omega - \pi)/T_{s})F_{1}(j\omega) = 0$$

#### 3.3.3 System specifications

We aim to build a 10-bit 80 MSPS ADC using the 2-channel HFB architecture described above. The important building blocks are the analog analysis filters, the subband ADCs with a sampling rate of 40 MHz. The digital synthesis filters are implemented in software.

In the following sections, we will describe how the analog analysis filters are chosen, methods for computing the synthesis filter taps and the SNR computation of a HFB system.

#### 3.4 Maximum achievable SFDR in a 2-channel HFB system

The resolution of the ADC to be used in an HFB system is limited by the maximum achievable SFDR of the HFB system. To compute SFDR, the ADCs are replaced by sample and hold (SAH) blocks which do not add quantization noise to the system. The value of SFDR can be computed by feeding a single tone input and measuring the power in the input tone to that of the aliasing tone. In a 2-channel HFB, SFDR is given by

Figure 3.5: Setup to measure SFDR in a 2-channel HFB based ADC

$$SFDR (\mathbf{dB}) = 20 \log \left| \frac{T_0(j\omega)}{T_1(j\omega)} \right|_{\omega = \omega_{ij}}$$

Table 3.1 shows the simulated and theoretically computed SFDR for three different cases of analog analysis filters.

| Analysis Filters H <sub>0</sub> & H <sub>1</sub> | FIR length L | <b>SFDR</b> <sub>theoretical</sub> | SFDR <sub>simulation</sub> |

|--------------------------------------------------|--------------|------------------------------------|----------------------------|

| All pass & Biquad                                | 32           | 112.1                              | 112.5                      |

| 3 <sup>rd</sup> order Butterworth LPF & HPF      | 128          | 144.2                              | 144.9                      |

| $5^{th}$ order Butterworth LPF & HPF             | 128          | 153.2                              | 152.6                      |

Table 3.1: Achievable SFDR in a 2-channel HFB measured at  $\frac{f_{in}}{f_s} = \frac{7371}{8192}$

#### 3.5 Choice of Optimal Analysis filters

High order analog analysis filters have a sharp roll off and result in synthesis filters which require a large number of taps for realization [Velazquez *et al.* (1998)]. RLC circuit based  $2^{nd}$  order filter banks have been studied in [Petrescu *et al.* (2005)]. Lower order analysis filters result in synthesis filters with smooth roll off thereby requiring lesser number of taps. In this work, we use simple second order active-RC filters.

We will have to trade off SNR with the complexity of the analysis filters and number of taps in the synthesis filters. Use of lower order analysis filters implies that the quantization noise added by each ADC is will now be shaped by a synthesis filter with smoother roll off. The loss in SNR in HFB based ADCs is illustrated below.

We use two second order filter for  $H_0(s)$  and  $H_1(s)$  and optimize ( $\omega_{LP}$ ,  $\omega_{BP}$ ,  $Q_{LP}$ ,  $Q_{BP}$ ) to minimize the error constraint (which accounts for the deviation of the distortion function from a delay d cycles, and a scaled version of the aliasing function) given by

$$\epsilon = \int_0^{\pi} \left[ \left| T_0(j\omega) - 2e^{-j\omega d} \right|^2 + 100 \left| T_1(j\omega) \right|^2 \right] d\omega$$

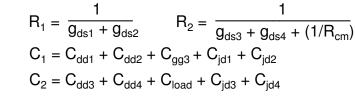

The generic  $H_0(s)$  and  $H_1(s)$  are given as

$$H_0(s) = \frac{b_0 + b_1 s}{a_0 + a_1 s + a_2 s^2}, \quad H_1(s) = \frac{c_0 + c_1 s}{d_0 + d_1 s + d_2 s^2}$$

We use **fminsearch** in Matlab to minimize  $\epsilon$  which is a function of  $(\omega_{LP}, \omega_{BP}, \mathbf{Q}_{LP}, \mathbf{Q}_{LP})$

$Q_{BP}$ ). The transfer functions of the optimized filters are

$$H_0(s) = 1, \ H_1(s) = \frac{\frac{\omega_0}{Q}s}{s^2 + \frac{\omega_0}{Q}s + \omega_0^2}$$

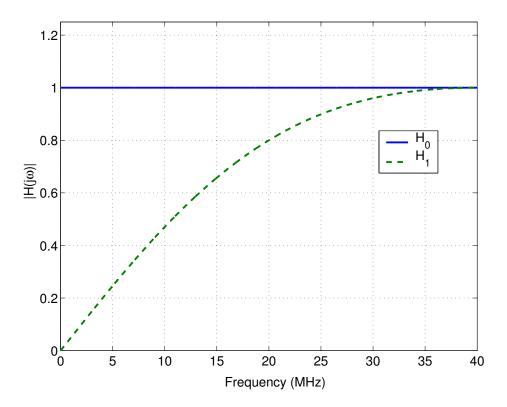

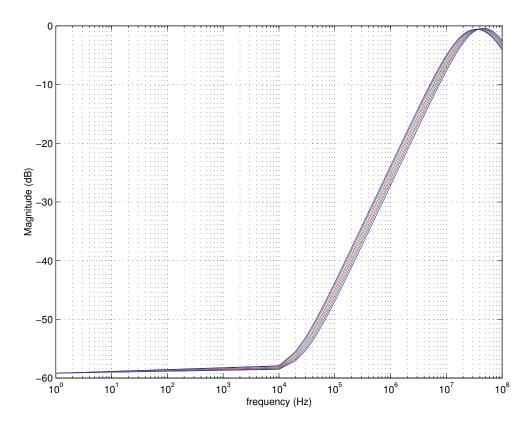

where  $\omega_0 = 2\pi \times 40$  Mrad/sec, Q = 0.5. The frequency responses of the optimized analog analysis filters are shown in Fig 3.5 and the digital synthesis filters in Fig 3.5.

Figure 3.6: 2 channel HFB analysis filters

#### 3.6 Computing the Synthesis filters

## 3.6.1 Delay optimization by minimizing energy loss due to synthesis filter truncation

Calculating the **ifft** of the ideal frequency response expressions obtained by solving equations [3.1,3.2] over N-points yields synthesis filters whose length is equal to N. By

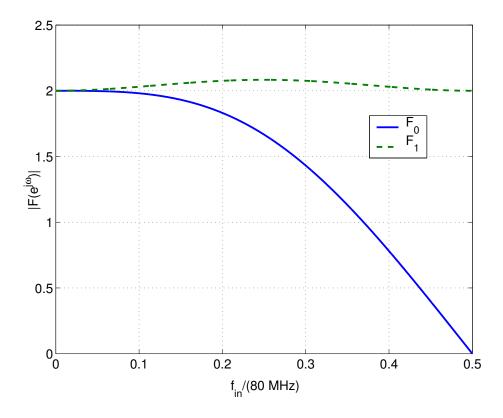

Figure 3.7: 2 channel HFB synthesis filters for 32-tap filters

using Parseval's theorem, the energy loss due to filter windowing to length L is given by

$$\epsilon = \sum_{k=0}^{1} \epsilon_{k} = \sum_{k=0}^{1} \int_{0}^{\pi} \left[ \left| \overline{F}_{k}(j\omega) \right|^{2} - \left| F_{k}(j\omega) \right|^{2} \right] d\omega = \sum_{k=0}^{1} \sum_{n=L}^{N-1} (f_{k}(n))^{2}$$

. where  $\overline{F}_k(j\omega)$  is the frequency response of the truncated filter of length L. The standard Matlab routine **fminsearch** is used to iteratively adjust delay d in equation [3.2] which will minimize energy loss  $\epsilon$ .

#### 3.6.2 Synthesis filters satisfying the LMSE criterion for white noise input

A white noise input sequence is generated and is band-limited to  $f_{in,max} = f_s$  Hz using a high order Butterworth filter. We assume a length L for all the FIR synthesis filters. The length of the input sequence to the system is M. The length of the resulting output sequence will be M + L - 1.

Figure 3.8: Synthesis filter identification using LMSE criteria

Since we have chosen the input sequence length as M and synthesis filter with L taps, the length of output y will be M + L - 1. Denoting the inputs to the system shown in hashed lines as  $x_0(n), x_1(n)$  of length M, we can express the output as

$$y(n) = \sum_{i=0}^{M+L-1} x_0(i) f_0(n-i) + \sum_{i=0}^{M+L-1} x_1(i) f_1(n-i)$$

The resultant output sequence y(n) can be represented in vector form as

$$Y = \sum_{k=0}^{1} X_k F_k$$

where the dimensions of Y, X, F<sup>1</sup> are  $(M + L - 1) \times 1$ ,  $(M + L - 1) \times (M + L - 1)$ ,  $(M + L - 1) \times 1$ . The class of filters  $f_k$  which result in the least reconstruction error  $E^2$  can be obtained by solving

$$\frac{dE^2}{dF} = 0 \text{ where } E^2 = (Y - \sum_{k=0}^1 X_k F_k)^T (Y - \sum_{k=0}^1 X_k F_k)$$

(3.4)

<sup>&</sup>lt;sup>1</sup>Y,X,F are used to denote vectors and should not be confused with frequency response.

The solution to equation [3.4] can be written as

$$\begin{bmatrix} X_1^T X_1 & X_1^T X_2 \\ X_2^T X_1 & X_2^T X_2 \end{bmatrix}_{dxd} \begin{bmatrix} F_1 \\ F_2 \end{bmatrix}_{dx1} = \begin{bmatrix} X_1^T Y \\ X_2^T Y \end{bmatrix}_{dx1}$$

where the dimension d = 2(M + L - 1). Solving the above equation will yield the synthesis filters satisfying LMSE criteria for white noise input.

#### 3.6.3 SNR degradation in HFB based ADCs

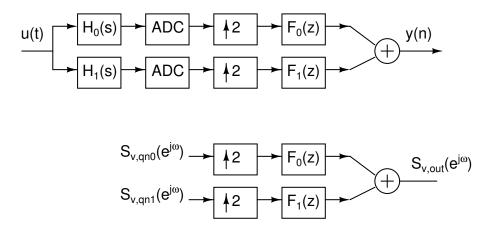

Figure 3.9: Computing SNR at the output in a 2-channel HFB based ADC

Fig 3.9 shows a two channel HFB based ADC. The quantization noise signal path is also shown in the figure. We need to compute  $S_{v,out}(e^{j\omega})$  as a function of  $S_{v,qn0}(e^{j\omega})$ ,  $S_{v,qn1}(e^{j\omega})$  and integrate over frequency to compute the quantization noise power at the output. We will first look at the effect of upsampling on quantization noise power.

#### Effect of upsampling on $S_{v,qn}(e^{j\omega})$

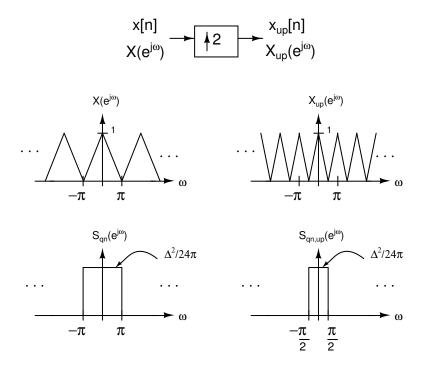

Fig 3.10 shows examples of the input and output spectrum's of two different inputs when passed through an upsample by 2 block. From Fig 3.10 it can be seen that the

integrated quantization noise power comes down by a factor 2 due to upsampling. But there will be no change in SNR due to upsampling because the signal power will also come down by a factor 2. Assuming that the input sequence length is N,

$$X(e^{j\omega}) = x[0] + x[1]e^{-j\omega} + x[2]e^{-j2\omega} \dots + x[N-1]e^{-j(N-1)\omega}$$

$$= \sum_{n=0}^{N-1} x[n]e^{-j\omega n}$$

After upsampling by a factor 2,

$$X_{up}(e^{j\omega}) = x[0] + x[1]e^{-j2\omega} + x[2]e^{-j4\omega} \dots + x[2N-2]e^{-j(2N-2)\omega}$$

$$= \sum_{n=0}^{N-1} x[n]e^{-j2\omega n} = X(e^{j2\omega})$$

From Fig 3.10, it can be seen that upsampling compresses the discrete time fourier transform (DTFT) by a factor of 2 along with the  $\omega$  axis.

Figure 3.10: Interpolation by factor 2

$$S_{v,in}(e^{j\omega}) \longrightarrow H(e^{j\omega}) \longrightarrow S_{v,out}(e^{j\omega}) = |H(e^{j\omega})|^2 S_{v,in}(e^{j\omega})$$

Figure 3.11: Effect of filtering on  $S_{v,qn,up}(e^{j\omega})$

Effect of filtering on  $S_{v,qn,up}(e^{j\omega})$

Fig 3.11 shows the effect of filtering of process with spectral density  $S_{v,in}(e^{j\omega})$  with a filter H( $e^{j\omega}$ ). From Fig 3.9, the integrated quantization noise power at the output can be written as

$$\begin{split} P_{qn,out} &= \int_{\frac{-\pi}{2}}^{\frac{\pi}{2}} S_{v,qn0,up}(e^{j\omega}) |F_0(e^{j\omega})|^2 \, d\omega + \int_{\frac{-\pi}{2}}^{\frac{\pi}{2}} S_{v,qn1,up}(e^{j\omega}) |F_1(e^{j\omega})|^2 \, d\omega \\ &= \frac{\Delta^2}{24\pi} \Big[ \int_{\frac{-\pi}{2}}^{\frac{\pi}{2}} |F_0(e^{j\omega})|^2 \, d\omega + \int_{\frac{-\pi}{2}}^{\frac{\pi}{2}} |F_1(e^{j\omega})|^2 \, d\omega \Big] \\ &= \frac{\Delta^2}{24\pi} \times \pi \Big[ \sum_{i=0}^{L-1} f_0(i)^2 + \sum_{i=0}^{L-1} f_1(i)^2 \Big] \qquad \text{(By using Parseval's theorem)} \\ &= \frac{\Delta^2}{12} \Big[ \frac{1}{2} \times \sum_{k=0}^{1} \sum_{i=0}^{L-1} f_k(i)^2 \Big] \end{split}$$

In general, for a M channel HFB, the integrated quantization noise power is given by

$$P_{qn,out} = \frac{\Delta^2}{12} \left[ \frac{1}{M} \times \sum_{k=0}^{M-1} \sum_{i=0}^{L-1} f_k(i)^2 \right]$$

and the SNR for a M channel HFB is given by

$$SNR_{out}[dB] = 6.02N + 1.76 - 10 \log_{10} \left[ \frac{1}{M} \times \sum_{k=0}^{M-1} \sum_{i=0}^{L-1} f_k(i)^2 \right]$$

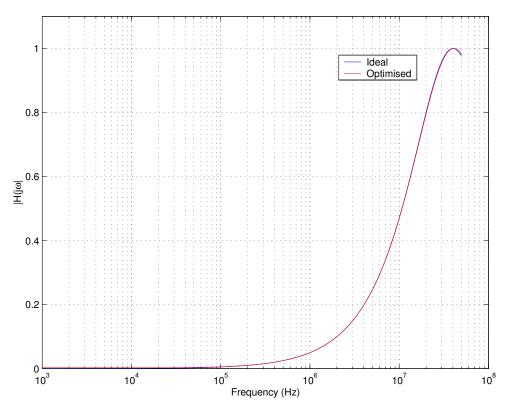

Simulation results on various 2-channel HFBs are shown in in Table 3.2. The simulation SNR is in close agreement with the theoretically computed SNR.

| Analysis Filters H <sub>0</sub> & H <sub>1</sub> | FIR length L | <b>SNR</b> <sub>theoretical</sub> | <b>SNR</b> <sub>simulation</sub> | ENOB     |

|--------------------------------------------------|--------------|-----------------------------------|----------------------------------|----------|

| All pass & Biquad                                | 32           | 56.7                              | 56.5                             | 9.1 bits |

| 3 <sup>rd</sup> order Butterworth LPF & HPF      | 128          | 58.9                              | 59.1                             | 9.5 bits |

| $5^{th}$ order Butterworth LPF & HPF             | 128          | 58.8                              | 58.5                             | 9.4 bits |

Table 3.2: SNR results on a 2-channel HFB

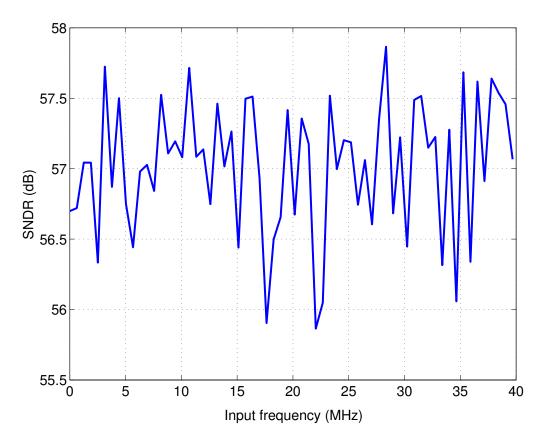

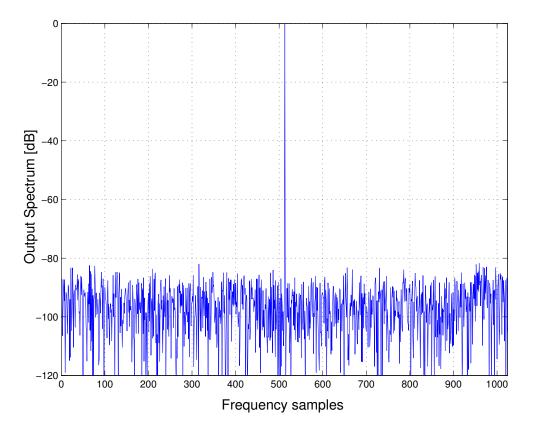

Fig 3.12 shows the simulated SNDR for a 2-channel HFB realized using "All pass &

Biquad" analog filters. The resolution of the ADC used in the simulations was 10-bits.

Figure 3.12: SNR simulation for a 2-channel HFB realized using "All pass & Biquad" analog filters

# **CHAPTER 4**

# **DESIGN OF A 10-BIT, 40 MSPS PIPELINE ADC**

In this chapter we discuss the design details of a 10-bit 40 MSPS pipeline ADC in a 0.35  $\mu$ m CMOS process.

# 4.1 Architecture of the pipelined ADC

Pipeline ADCs are being employed in a wide range of applications, including digital receiver, base station, CCD imaging, ultrasonic medical imaging, digital video (e.g. HDTV), xDSL, cable modem and fast Ethernet. Pipeline ADCs provide high resolutions at high throughput rates at the expense of latency.

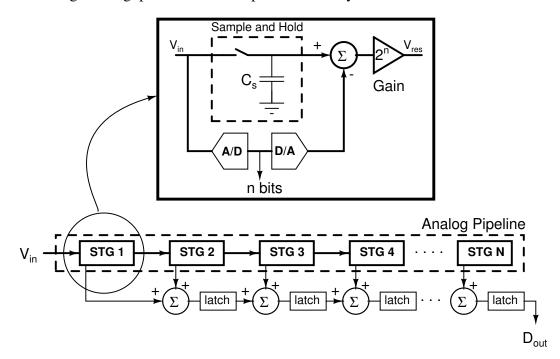

Figure 4.1: Architecture of a generic pipelined ADC

The sample and hold in the first stage is used to sample the input. Subsequent stages sample the residue of the previous stage. Thus the throughput rate is independent of the

number of stages in the pipeline. The amplifier with gain 2 is used to amplify the residue before passing it onto the next stage [Cho *et al.* (1994)]. By doing this, the resolution requirements for the subsequent stages can be relaxed. The DAC and gain 2 amplifier together will be termed as Multiplying-DAC (MDAC).

Fig 4.1 shows the block diagram of a generic pipeline ADC with N-bit resolution. Comparator offsets for the architecture shown in Fig 4.1 needs to be atleast one bit better than the overall resolution of the ADC. The use of the 1.5 bits/stage architecture [Lewis *et al.* (1992)] alleviates the offset requirements on the MDAC comparators.

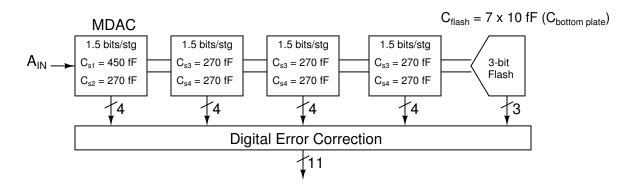

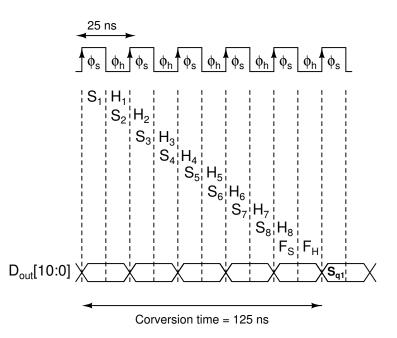

Fig 4.2 shows the architecture of the 10-bit pipelined ADC. The ADC is designed for 10-bit resolution (capacitors chosen for 10-bit resolution) but utilizes 11-bit arithmetic. The opamp sharing technique is used to reduce the number of opamps [Nagaraj *et al.* (1997)]. By using opamp sharing, two stages as shown in Fig 4.1 can be merged into a single stage and the number of required opamps can be halved.

Figure 4.2: Architecture of the 10-bit pipelined ADC

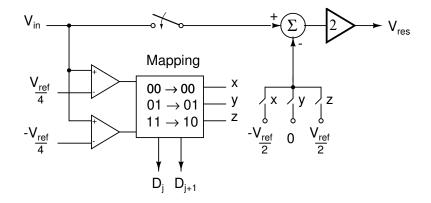

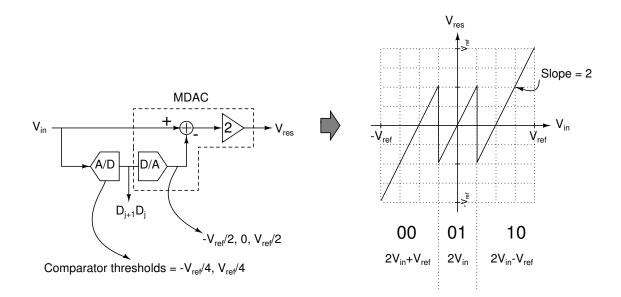

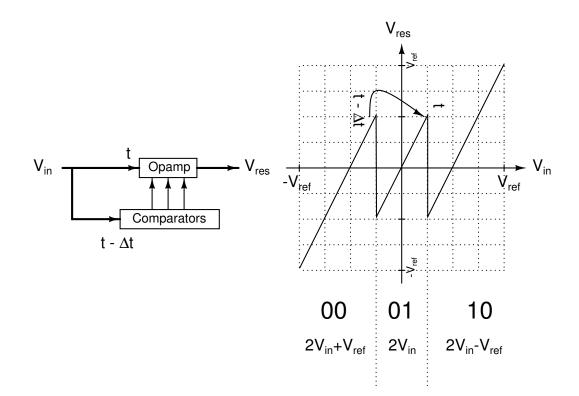

#### 4.2 MDAC stage input-output characteristics

The input-output characteristic of each 1.5 bits/stage MDAC is defined below :

$$V_{\text{RES}} = \begin{cases} 2V_{\text{IN}} + V_{\text{REF}} & \text{if } V_{\text{IN}} < -\frac{V_{\text{REF}}}{4} \\ 2V_{\text{IN}} & \text{if } |V_{\text{IN}}| \le \frac{V_{\text{REF}}}{4} \\ 2V_{\text{IN}} - V_{\text{REF}} & \text{if } V_{\text{IN}} > \frac{V_{\text{REF}}}{4} \end{cases}$$

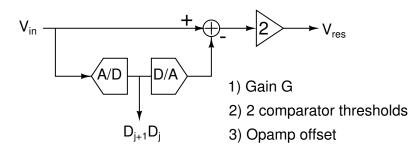

In the above equations,  $2V_{\text{REF}}$  denotes the peak-peak swing of the input signal to be quantized. As shown in Fig 4.3, the three important blocks in each MDAC stage are:

- Closed amplifier with gain = 2

- Bootstrapped sampling switches

- Comparators which generate the V<sub>dac</sub>

Figure 4.3: Important sub-blocks in a MDAC stage

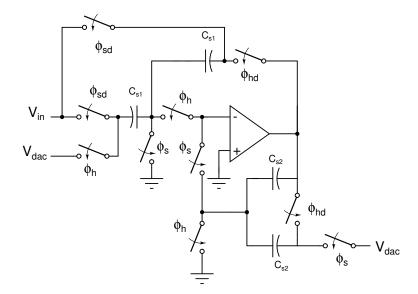

Implementation details of each of the constituent blocks are described in subsequent sections. Fig 4.4 shows the input/output characteristics of a single MDAC stage. Using the opamp sharing technique, two MDAC stages can be realized using only opamp rather than two. Fig 4.5 shows the implementation of two MDAC stages in which the hold phase for first stage is  $\phi_h$  and the hold phase for the second stage is  $\phi_s$ . Clocks  $\phi_{sd}$  and  $\phi_{hd}$  are delayed versions of  $\phi_s$  and  $\phi_h$ .

Figure 4.4: MDAC stage input-output characteristic

Figure 4.5: Opamp shared MDAC stage

#### 4.3 Design of MDAC stage

MDAC stage is the most critical block. Before starting the design of the MDAC stage, the specifications for all the following parameters need to fixed. They are -

- Value of sampling capacitor  $C_{sample}$ .

- Open loop DC gain of the opamp.

- Unity-Gain Bandwidth (UGB) of the opamp.

## 4.3.1 Arriving at the opamp specifications

Value of C<sub>sample</sub>

The choice of a particular  $C_{sample}$  is constrained by two parameters - thermal noise and capacitor matching. Poly-Poly capacitors are used for realizing the capacitors. Constraining the noise contribution due to the sampling capacitor to be 0.1 LSB, we get

$$\sqrt{\frac{kT}{C_{sample}}} < 0.195 \text{ mV} \Rightarrow C_{sample} > 108 \text{ fF}$$

The matching between the capacitors should be of 10-bit accuracy.

$$\sigma_{\underline{\Delta C}} = \frac{1.2}{\sqrt{WL}} \% \mu m \Rightarrow WL \ge 151 \mu m^2$$

We will choose a sampling capacitor of 450 fF which will require an area of 380  $\mu m^2$ .

## Value of $A_{dc}$ , Unity-gain Bandwidth $f_u$

The open loop dc gain of the first MDAC opamp has to atleast  $2^{n+1}$  where n is the effective resolution of the opamp.

$$A_{dc} \ge 2^{11} = 2048 \approx 66 \,\mathrm{dB}$$

The UGB of the opamp is determined the required setting time and the feedback factor of the MDAC stage. The MDAC stage has an ideal feedback factor  $\beta = 0.5$ , but due to the presence of parasitic capacitances at the opamp inputs, we will see a degradation in the  $\beta$  factor. Assuming a settling error in half a clock period (12.5 ns) for the first stage  $\leq \frac{V_{LSB}}{2}$  of 10-bit ADC,

$$V_{FS}.e^{-\frac{t}{\tau}} \leq \frac{V_{LSB}}{2}$$

$$\frac{1}{\tau} = \beta w_u \Rightarrow f_u \geq 200 \text{ MHz}$$

The opamp to be designed should have minimum dc gain of 66 dB and UGB of 200 MHz.

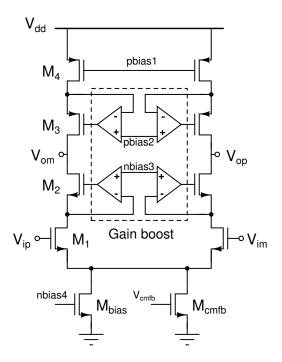

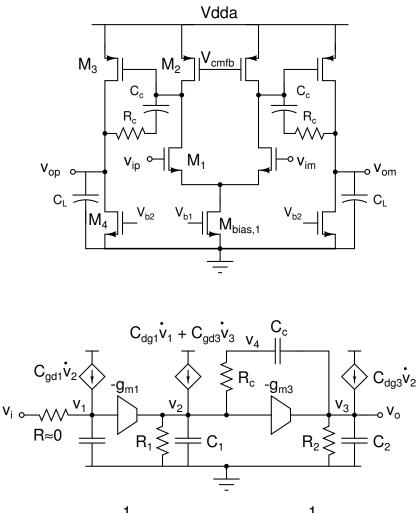

## 4.3.2 Opamp topology

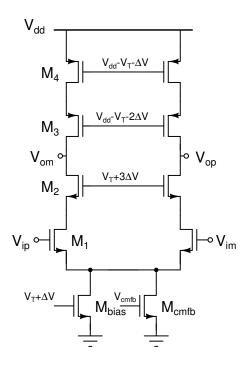

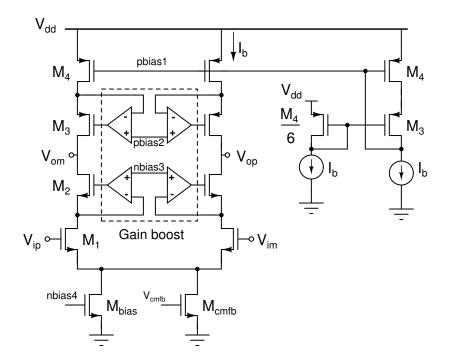

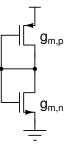

A gain boosted telescopic opamp is used in the MDAC stage [Bult and Geelen (1990)]. The schematic of the gain boosted amplifier is shown in Fig 4.6. The gain boosted amplifier consists of 5 individual amplifiers to achieve the entire gain - one main telescopic cascode opamp, 2 nMOS folded cascode amplifiers and 2 pMOS folded

cascode amplifiers.

Assuming that the overdrive of each device in the telescopic cascode opamp is chosen as  $\Delta$ , the gain-boost amplifier (GBA) for device M<sub>2</sub> will sense voltages of the order of 2 $\Delta$  and drive outputs in the order V<sub>T</sub> + 3 $\Delta$ . Hence a pMOS folded cascode is used as the GBA for device M<sub>2</sub>. Similarly the GBA for device M<sub>3</sub> will sense voltages of the order of V<sub>DD</sub> –  $\Delta$  and drive outputs in the order V<sub>DD</sub> - V<sub>T</sub> - 2 $\Delta$ . Hence a nMOS folded cascode is used as the GBA for device M<sub>3</sub>.

We study the design of each of the 3 opamps (telescopic cascode, nMOS folded cascode and pMOS folded cascode) independently and finally arrive at the gain boosted telescopic opamps specification. Sizes of the transistors shown in Fig 4.6 are shown in the telescopic cascode amplifier section.

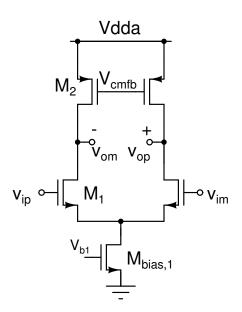

Figure 4.6: MDAC stage opamp architecture

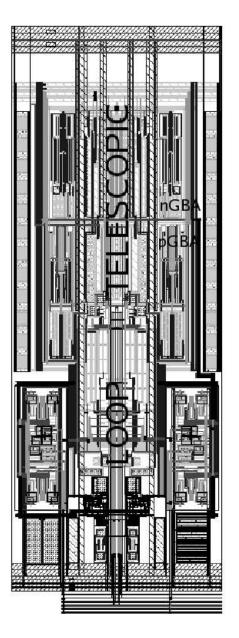

#### **4.3.3** Design of the telescopic opamp

Fig 4.7 shows the schematic of the telescopic opamp without the gain boosting amplifiers. Table 4.7 shows the device dimensions, the  $g_m$  and  $r_o$  of the devices used. The output common mode is controlled by having a tunable tail current source whose value is  $\frac{1}{32}$  of the entire tail current. The dominant pole is determined by the load capacitor and  $g_{m1}$ . The DC gain of the opamp is given by

$$A_{ol} = g_{m1}(R_{n,cascode} || R_{p,cascode})$$

$$= q_{m1}(q_{m2}r_{o2}r_{o1} || q_{m3}r_{o3}r_{o4})$$

Figure 4.7: Telescopic opamp without the gain boosting amplifiers

Tab.4.1 shows the simulated open loop response of the telescopic cascode opamp.

|                                        | $M_{bias}$          | $M_{cmfb}$          | $M_1$               | $M_2$               | $M_3$                | $M_4$                |

|----------------------------------------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|

|                                        | 1 bias              | 1 <sup>1</sup> cmfb |                     |                     |                      |                      |

| Size                                   | $62(\frac{2}{0.5})$ | $2(\frac{2}{0.5})$  | $64(\frac{2}{0.5})$ | $64(\frac{2}{0.5})$ | $96(\frac{2}{0.35})$ | $96(\frac{2}{0.35})$ |

| I (mA)                                 | 1.966               | 0.052               | 1.009               | 1.009               | 1.009                | 1.009                |

| $\Delta V (mV)$                        | 232                 | 223.2               | 237.7               | 238.4               | 320                  | 330                  |

| $g_m$ (mS)                             | 5.726               | 0.172               | 6.1                 | 6.387               | 5.67                 | 5.27                 |

| $r_o \left( \mathbf{k} \Omega \right)$ | 2.56                | 114.1               | 4.16                | 13.36               | 4.49                 | 3.33                 |

|                                        |                     |                     |                     |                     |                      |                      |

| Feature                                |                     |                     |                     | Achieved re         | esponse              |                      |

| DC gain                                |                     |                     |                     | 52 dB               |                      |                      |

| Phase Margin (PM)                      |                     |                     | PM)                 | 81°                 |                      |                      |

| UGB with $C_L = 1.2 \text{ pF}$        |                     |                     | 1.2 pF              | 700 M               | Hz                   |                      |

Table 4.1: Achieved open loop response of the telescopic cascode opamp

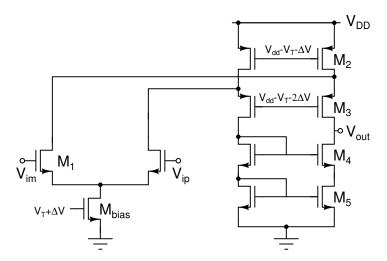

# 4.3.4 Design of the gain boosting amplifiers - nMOS folded cascode opamp

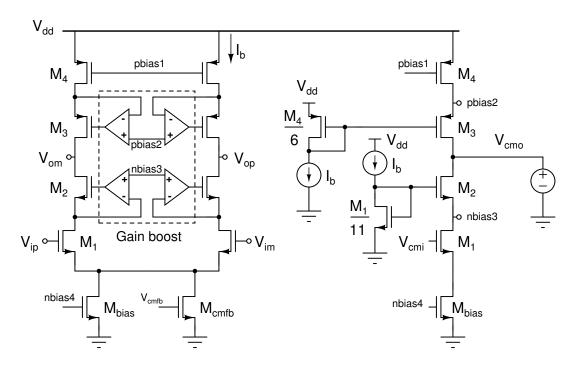

Fig 4.8 shows the schematic of the nMOS folded cascode opamp. Table 4.2 shows the device dimensions, the  $g_m$  and  $r_o$  of the devices used. The frequency response of the gain boosting amplifier is not crucial compared to the response of the telescopic cascode itself [Bult and Geelen (1990)].

Figure 4.8: nMOS folded cascode gain boosting amplifier

The small signal DC gain is given by

$$A_{ol} = g_{m1}(R_{n,cascode} || R_{p,cascode})$$

$$= g_{m1}(g_{m3}r_{o3}r_{o2} || g_{m4}r_{o4}r_{o5})$$

The load capacitance seen by the opamp will be equal to the parasitic capacitances at the gate of M3 in Fig 4.7.

|                           | $M_{bias}$        | $M_1$                | $M_2$                  | $M_3$                  | $M_4$               | $M_5$               |

|---------------------------|-------------------|----------------------|------------------------|------------------------|---------------------|---------------------|

| Size                      | $32(\frac{1}{1})$ | $16(\frac{1}{0.35})$ | $36(\frac{1.5}{0.75})$ | $36(\frac{1.5}{0.75})$ | $12(\frac{1}{0.5})$ | $12(\frac{1}{0.5})$ |

| Ι (μA)                    | 97.1              | 48.5                 | 93.7                   | 45.1                   | 45.1                | 45.1                |

| $\Delta V (mV)$           | 196               | 145                  | 271                    | 198                    | 175                 | 166                 |

| $g_m$ (mS)                | 0.706             | 0.563                | 0.645                  | 0.453                  | 0.411               | 0.403               |

| $r_o (\mathbf{k} \Omega)$ | 591.3             | 84.67                | 88.1                   | 281.5                  | 2606                | 257.5               |

Table 4.2: Transistor sizes of the nMOS folded cascode opamp

| Feature                       | Achieved response |

|-------------------------------|-------------------|

| DC gain                       | 69.5 dB           |

| Phase Margin (PM)             | 67°               |

| UGB with $C_L = 1 \text{ pF}$ | 75 MHz            |

Table 4.3: Achieved open loop response of nMOS folded cascode opamp

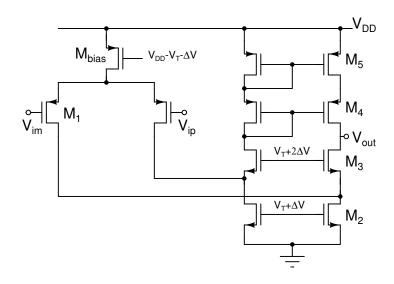

# 4.3.5 Design of the gain boosting amplifiers - pMOS folded cascode opamp

Fig 4.9 shows the schematic of the pMOS folded cascode opamp. Table 4.4 shows the device dimensions, the  $g_m$  and  $r_o$  of the devices used.

The small signal gain is given by

$$A_{ol} = g_{m1}(R_{n,cascode} || R_{p,cascode})$$

$$= g_{m1}(g_{m3}r_{o3}r_{o2} || g_{m4}r_{o4}r_{o5})$$

The load capacitance seen by the opamp will be equal to the parasitic capacitances at the gate of M2 in Fig 4.7.

Figure 4.9: pMOS folded cascode gain boosting amplifier

|                                        | $M_{bias}$        | $M_1$                | $M_2$               | $M_3$               | $M_4$                  | $M_5$                  |

|----------------------------------------|-------------------|----------------------|---------------------|---------------------|------------------------|------------------------|

| Size                                   | $32(\frac{1}{1})$ | $16(\frac{1}{0.35})$ | $12(\frac{1}{0.5})$ | $12(\frac{1}{0.5})$ | $36(\frac{1.5}{0.75})$ | $36(\frac{1.5}{0.75})$ |

| Ι (μA)                                 | 96.3              | 48.1                 | 97.3                | 49.1                | 49.1                   | 49.1                   |

| $\Delta V (mV)$                        | 388               | 271                  | 236                 | 181                 | 210                    | 200                    |

| $g_m$ (mS)                             | 0.43              | 0.36                 | 0.57                | 0.43                | 0.47                   | 0.47                   |

| $r_o \left( \mathbf{k} \Omega \right)$ | 236.7             | 78.7                 | 84.31               | 220.2               | 257.8                  | 237.5                  |

Table 4.4: Transistor sizes of the pMOS folded cascode opamp

| Feature                       | Achieved response |

|-------------------------------|-------------------|

| DC gain                       | 63 dB             |

| Phase Margin (PM)             | 70°               |

| UGB with $C_L = 1 \text{ pF}$ | 47 MHz            |

Table 4.5: Achieved open loop response of pMOS folded cascode opamp

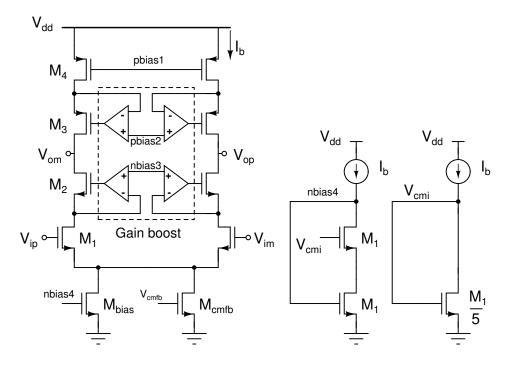

#### 4.3.6 Biasing the opamp

5 important bias voltages need to generated for biasing the opamp. They are vcmi  $(\approx V_T + 2\Delta V)$ , pbias1 ( $\approx V_{DD} - V_T - \Delta V$ ), pbias2 ( $\approx V_{DD} - \Delta V$ ), nbias3 ( $\approx 2\Delta V$ ) and nbias4 ( $\approx V_T + \Delta V$ ), where  $\approx \Delta V$  is the assumed overdrive of the tail current source.

Figs 4.10, 4.11 and 4.12 show the generation of each of these voltages respectively. The opamp along with the bias circuit is shown in each figure for sake of clarity.

Figure 4.10: Biasing - Generation of vcmi, nbias4

Figure 4.11: Biasing - Generation of pbias1

Figure 4.12: Biasing - Generation of pbias2, nbias3

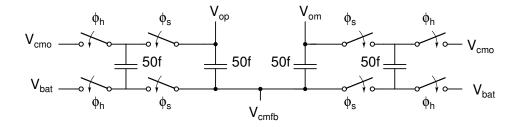

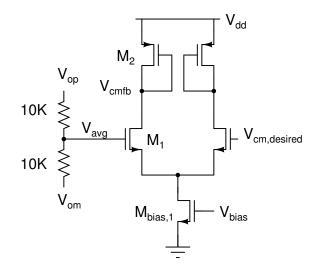

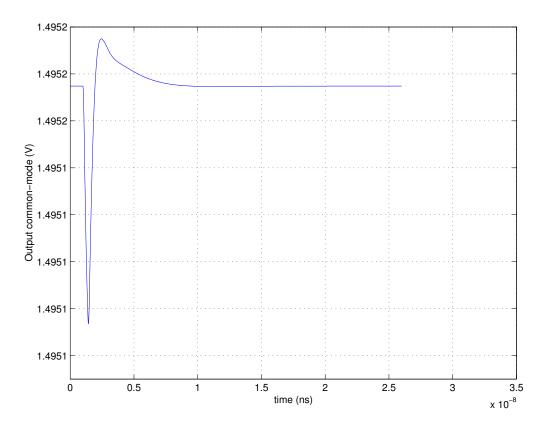

# 4.3.7 Common-mode feedback loop

A switched capacitor common feedback loop [Choksi and Carley (2003)] is used to control the output common mode. The desired output common mode is 1.5 V. Each of the switches were nMOS with dimensions  $2(\frac{0.5}{0.35})$ . With the inputs tied to input common mode, the output common mode was verified to settle to 99% V<sub>cmo</sub> in 12.5 ns.

Figure 4.13: Switched capacitor CMFB

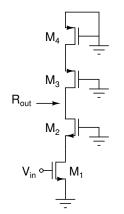

#### 4.3.8 Opamp noise analysis

For noise analysis, the equivalent half circuit is shown in Fig 4.14. The tail current source is not shown as it does not contribute to noise at the output. All the nodes whose gate values are at DC are grounded in the incremental equivalent circuit.

Let the equivalent resistance of the gain-boosted cascode be denoted as Rout.

$$R_{out} = (R_{n,cascode} || R_{p,cascode})$$

=  $(A_n g_{m2} r_{o2} r_{o1} || A_p g_{m3} r_{o3} r_{o4})$

$v_{n,out} = g_{m1} R_{out} v_{n1} + g_{m4} R_{out} v_{n4}$

$S_{vn,out} = g_{m1}^2 R_{out}^2 S_{v,n1} + g_{m4}^2 R_{out}^2 S_{v,n4}$

The major noise contributors are transistors  $M_1$  and  $M_4$ . The equivalent input referred noise integrated over 10 KHz to 1 GHz is 90.1  $\mu$ V ( $\approx 0.1$  LSB).

Figure 4.14: Equivalent circuit for noise analysis

#### 4.3.9 Summary of simulated results

Tab.4.6 shows the simulated open loop response of the gain-boosted opamp.

$$A_{ol} = g_{m1}(R_{n,cascode}||R_{p,cascode})$$

$$= g_{m1}(A_n g_{m2} r_{o2} r_{o1}||A_p g_{m3} r_{o3} r_{o4})$$

| Feature                         | Achieved response |

|---------------------------------|-------------------|

| DC gain                         | 118 dB            |

| Phase Margin (PM)               | 80°               |

| UGB with $C_L = 1.2 \text{ pF}$ | 700 MHz           |

Table 4.6: Achieved open loop response

## 4.3.10 Design of bootstrapped sampling switches

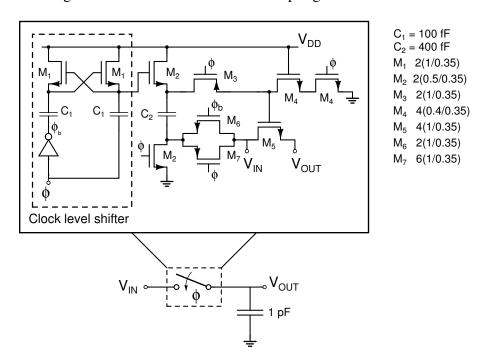

In the first MDAC stage, bootstrapped switches are used to achieve lower distortion. Bootstrapping the sampling switch ensures a constant gate-source voltage across the switch. Bootstrapping techniques reported in [Nagaraj *et al.* (2000)] are used to realize a sampling switch with 3 dB bandwidth of 330 MHz with a 1 pF capacitive load.

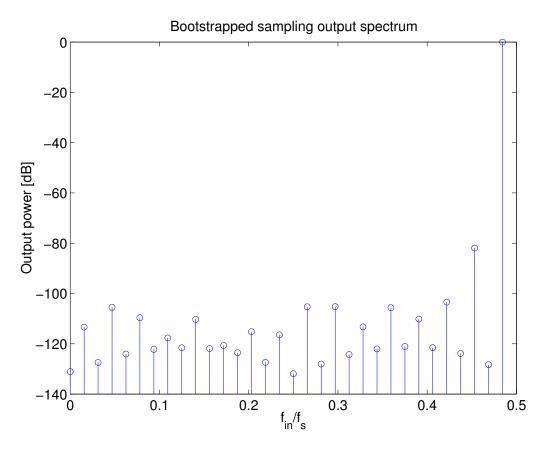

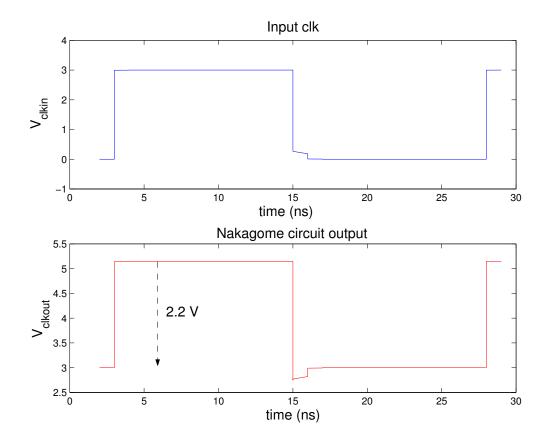

Fig 4.15 shows the implementation of the sampling switch along with the circuit for the bootstrapped clock generator. The Nakagome charge pump [Nakagome *et al.* (1991)] used for generating a clock which switches from 3.0 V to 5.2 V is shown in dotted lines in Fig 4.15. The third order harmonic distortion is 80 dB for 2  $V_{pp}$ , 19.375 MHz sinusoidal input. Fig 4.16 shows the output spectrum of the switch.

During layout, attention should be paid to minimize the value of parasitic capaci-

tance between the input and output terminals of the sampling switch. Signal feedthrough from the input pin to the output pin during the hold phase degrades the distortion performance of the sampling switch. For a fully differential implementation of the MDAC stage, 4 bootstrapped switches are required. Only one clock level shifter circuit was used for driving the boosted clock to all the 4 sampling switches.

Figure 4.15: Schematic of bootstrapped switch

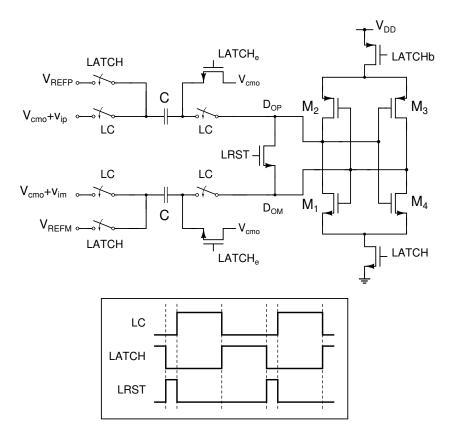

# 4.3.11 Comparator design

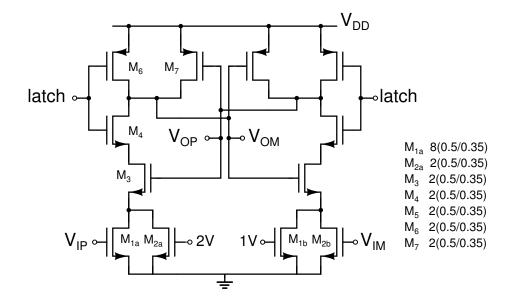

The A/D converter in each MDAC stage requires 2 comparators, with comparator thresholds at  $\frac{V_{\text{REF}}}{4}$  and  $\frac{-V_{\text{REF}}}{4}$ . The need to generate two different references  $\frac{V_{\text{REF}}}{4}$ and  $\frac{-V_{\text{REF}}}{4}$  can be avoided by using the comparator topology in [Cho and Gray (1995)]. Fig 4.18 shows the circuit implementation of the comparator used in MDAC stage. The bottom NMOS device pairs (M<sub>1a</sub>, M<sub>2a</sub>) and (M<sub>1b</sub>, M<sub>2b</sub>) operate in triode region and act as resistances R<sub>1</sub>, R<sub>2</sub>. The values of R<sub>1</sub>, R<sub>2</sub> depend on the input voltages V<sub>IP</sub>, V<sub>IM</sub>. The values of R<sub>1</sub>, R<sub>2</sub> are given by the equations shown below. The input common mode

Figure 4.16: Output spectrum of the bootstrapped switch

Figure 4.17: Nakagome charge pump output

Figure 4.18: MDAC stage comparator

voltage  $V_{cmo}$  is 1.5V and  $V_{REF}$  is 1V.

$$\frac{1}{R_1} = K_n \left[ \frac{W_{1a}}{L} (V_{\rm IP} - V_T) + \frac{W_{2a}}{L} (V_{cmo} + \frac{V_{\rm REF}}{2} - V_T) \right]$$

$$\frac{1}{R_2} = K_n \left[ \frac{W_{1b}}{L} (V_{\rm IM} - V_T) + \frac{W_{2b}}{L} (V_{cmo} - \frac{V_{\rm REF}}{2} - V_T) \right]$$