## ANALYSIS AND MITIGATION OF OPAMP

# NONLINEARITIES IN CONTINUOUS-TIME

## **OVERSAMPLED CONVERTERS**

A THESIS

submitted by

### PRABU SANKAR THIRUGNANAM

for the award of the degree

of

### **DOCTOR OF PHILOSOPHY**

### DEPARTMENT OF ELECTRICAL ENGINEERING

#### INDIAN INSTITUTE OF TECHNOLOGY, MADRAS.

August 2010

This thesis is dedicated to my parents

**Thirugnanam** and **Thenmozhi**

## THESIS CERTIFICATE

This is to certify that the thesis titled **ANALYSIS AND MITIGATION OF OPAMP NONLINEARITIES IN CONTINUOUS-TIME OVERSAMPLED CONVERTERS**, submitted by **Prabu Sankar T.**, to the Indian Institute of Technology, Madras, for the award of the degree of **Doctor of Philosophy**, is a bona fide record of the research work done by him under my supervision. The contents of this thesis, in full or in parts, have not been submitted to any other Institute or University for the award of any degree or diploma.

**Dr. Y. Shanthi Pavan** Research Guide Professor Dept. of Electrical Engineering IIT Madras, 600 036

Place: Chennai

Date:

## TABLE OF CONTENTS

| ACKNO        | OWLEDGEMENTS                                                                    | i               |

|--------------|---------------------------------------------------------------------------------|-----------------|

| ABSTR        | ACT                                                                             | ii              |

| LIST O       | F TABLES                                                                        | viii            |

| LIST O       | F FIGURES                                                                       | xvii            |

| ABBRE        | VIATIONS                                                                        | xviii           |

| NOTAT        | IONS                                                                            | XX              |

| CHAP         | TER 1 INTRODUCTION                                                              | 1               |

| 1.1          | Fundamentals of ADC - Sampling and Quantization                                 | 2               |

| 1.2          | ADC architectures                                                               | 6               |

| 1.3          | Basics of Delta-Sigma modulation                                                | 10              |

| 1.4          | Continuous-Time Delta-Sigma Modulators                                          | 19              |

|              | 1.4.1 Advent of continuous-time delta-sigma modulators and their advantages     | 19              |

|              | 1.4.2 Design methodology of continuous-time modulators                          | 21              |

|              | 1.4.3 Design issues in continuous-time modulators                               | 26              |

|              | 1.4.4 Issue of integrator nonlinearity in continuous-time modulators            | 33              |

| 1.5          | Prior work and Motivation                                                       | 39              |

| 1.6          | Contributions                                                                   | 40              |

| 1.7          | Organization of the thesis                                                      | 41              |

| CHAPT<br>TIM | TER 2 ANALYSIS OF INTEGRATOR NONLINEARITY IN CON<br>E DSMs : THE MULTI-BIT CASE | NTINUOUS-<br>43 |

| 2.1          | Modeling nonlinearity in $G_m$ -C and active-RC integrators                     | 44              |

|              | 2.1.1 G <sub>m</sub> -C integrator                                              | 44              |

|               | 2.1.2 Active-RC integrators                                                               | 45        |

|---------------|-------------------------------------------------------------------------------------------|-----------|

| 2.2           | Effect of integrator nonlinearity in multi-bit CIFF modulators                            | 59        |

|               | 2.2.1 Analysis of modulators with an RZ DAC                                               | 66        |

| 2.3           | Simulation results                                                                        | 72        |

| СНАР          | TER 3 MODELING THE EFFECT OF INITIAL TRANSIENTS                                           | 81        |

| 3.1           | Modeling of integrator nonlinearity including the effect of initial tran-<br>sients       | 82        |

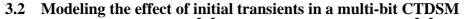

| 3.2           | Modeling the effect of initial transients in a multi-bit CTDSM                            | 87        |

| 3.3           | Simulation results                                                                        | 89        |

| 3.4           | Extensions to the analysis                                                                | 95        |

| CHAP'<br>: TH | TER 4 ANALYSIS OF INTEGRATOR NONLINEARITY IN CTDS<br>HE SINGLE-BIT CASE                   | SMs<br>98 |

| 4.1           | Distortion with $G_m$ -C and active-RC integrators with a single-stage transconductor     | 98        |

| 4.2           | Distortion with active-RC integrators based on Miller and feedforward compensated opamps  | 102       |

| 4.3           | Simulation results                                                                        | 109       |

| 4.4           | Severity of integrator nonlinearity in single-bit and multi-bit modulators and discussion | 115       |

| CHAP'<br>SIS' | TER 5MITIGATION OF NONLINEARITIES USING THE AS-TED OPAMP TECHNIQUE                        | 117       |

| 5.1           | Basics of opamp assistance                                                                | 119       |

| 5.2           | Analysis of nonlinearity in two-stage opamp assisted active-RC inte-<br>grators           | 122       |

| 5.3           | Nonidealities of the assistant blocks                                                     | 127       |

|               | 5.3.1 Effect of noise due to opamp assistants                                             | 128       |

|               | 5.3.2 Effect of distortion from the assistant circuitry                                   | 130       |

| 5.4           | Simulation results                                                                        | 131       |

| 5.5           | Application of opamp assistance to multi-bit modulators                                   | 134       |

| 5.6           | Prospects and related work                                                                | 136       |

| CHAP<br>ULA   | FER 6<br>ATORS     | DESIGN OF LOW POWER SINGLE-BIT AUDIO MOD-                                         |   |

|---------------|--------------------|-----------------------------------------------------------------------------------|---|

| 6.1           | Addres             | ssing the issues of a single-bit design                                           |   |

| 6.2           | Loop f             | ilter architecture                                                                |   |

| 6.3           | Circuit            | design details                                                                    |   |

|               | 6.3.1              | Operational amplifiers                                                            |   |

|               | 6.3.2              | Quantizer                                                                         |   |

|               | 6.3.3              | Feedback DACs                                                                     |   |

|               | 6.3.4              | Assistant circuitry                                                               |   |

| 6.4           | Simula             | tion results                                                                      |   |

| 6.5           | Measu              | rement results                                                                    |   |

|               | 6.5.1              | Jitter sensitivity measurements                                                   |   |

| 6.6           | Compa              | rrison with other work                                                            |   |

| CHAP          | FER 7              | CONCLUSION                                                                        |   |

| 7.1           | Summa              | ary of the contributions and observations                                         |   |

| 7.2           | Sugges             | stions for future work                                                            |   |

| APPEN<br>curr | IDIX A<br>ent inje | Analysis of nonlinear systems using Bussgang's method of ction                    |   |

| APPEN<br>base |                    | Comparison of Miller and feedforward compensated opamp<br>e-RC integrators        | ) |

| B.1           | Active             | -RC integrator with a two-stage Miller compensated opamp .                        |   |

| B.2           | Active             | -RC integrator with a feedforward compensated opamp                               |   |

| APPEN<br>a we |                    | Autocorrelation function of Gaussian noise passed through inearity                |   |

| APPEN<br>nals |                    | Low frequency equivalence of time-varying random sig-<br>mpled and held waveforms |   |

| APPEN<br>gies | DIX E              | A comparison of resistive and current-steering DAC topolo-                        |   |

| E.1           | Noise              |                                                                                   |   |

| E.2           | Speed              | and Area                                                                          |   |

| APPENDIX F Slewing and nonlinearity issues in a multi-bit CTDSM with an RZ feedback DAC                        | 200 |

|----------------------------------------------------------------------------------------------------------------|-----|

| APPENDIX G Analysis of nonlinearity of the second stage transconduc-<br>tor in two-stage active-RC integrators | 202 |

| G.1 Modeling of second stage nonlinearity in active-RC integrators with feedforward compensated opamp          | 202 |

| G.2 Severity of second stage nonlinearity in two-stage active-RC integrators                                   | 206 |

| APPENDIX H Anti-alias rejection of CTDSMs with direct path for the input signal                                | 209 |

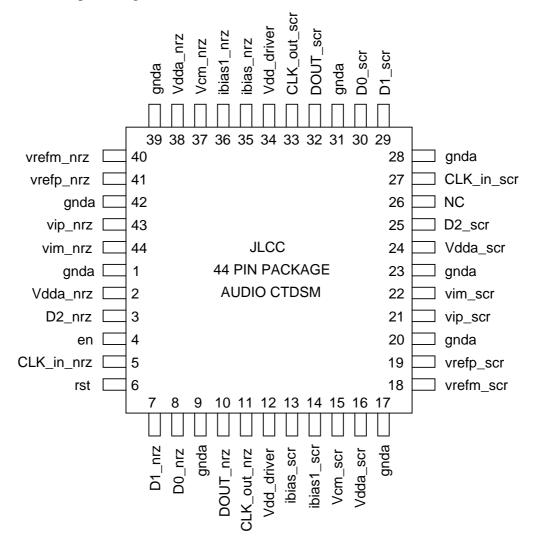

| APPENDIX I Pin details of the audio CTDSM                                                                      | 211 |

# LIST OF TABLES

| 3.1 | Relative nonlinear coefficients in a feedforward opamp based integrator.                                            | 91  |

|-----|---------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Relative nonlinear coefficients of various integrator configurations used in the single-bit modulator with NRZ DAC. | 110 |

| 6.1 | Performance of a CTDSM using a conventional integrator (NRZ DAC) as a function of current consumption.              | 157 |

| 6.2 | Performance of a CTDSM using a conventional integrator (SCR DAC) as a function of current consumption.              | 158 |

| 6.3 | Summary of measured performance of the NRZ and SCR modulators.                                                      | 168 |

| 6.4 | Comparison with other Delta-Sigma modulators                                                                        | 171 |

| I.1 | Functionality of pins of audio CTDSM                                                                                | 212 |

# LIST OF FIGURES

| 1.1  | Functional view of the role played by ADC and DAC                                                                                                                                                                        | 1        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2  | Illustration of sampling and quantization operations occurring in an ADC                                                                                                                                                 | 2        |

| 1.3  | (a) Model of an ADC along with anti-aliasing filter (b) Illustration of aliasing into the signal band from components around multiples of $\pm f_s$ (c) Response of ideal and practical anti-aliasing filters            | 3        |

| 1.4  | Typical input-output characteristic of a 8-level quantizer along with the quantization error profile                                                                                                                     | 4        |

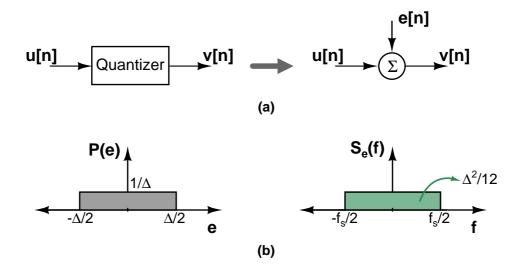

| 1.5  | (a) Linear representation of a quantizer (b) Probability density function, $P(e)$ and Power Spectral Density, $S_e(f)$ of the quantization noise .                                                                       | 5        |

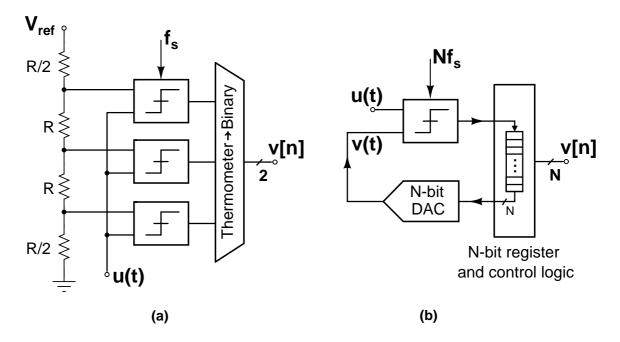

| 1.6  | (a) 4-bit Flash ADC (b) Functional block diagram of a SAR ADC .                                                                                                                                                          | 7        |

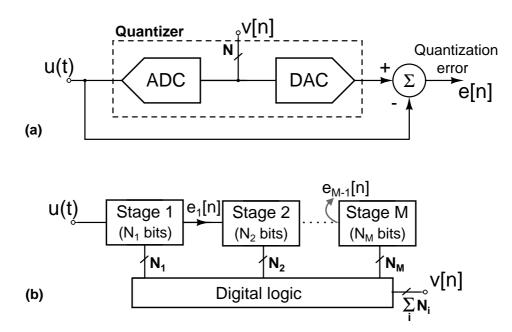

| 1.7  | (a) Individual stage of a pipeline ADC (b) Functional block diagram of a pipeline ADC having M stages                                                                                                                    | 8        |

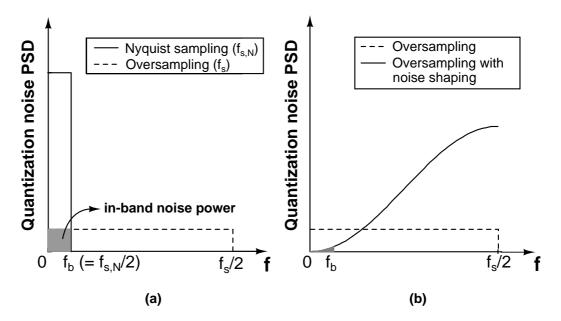

| 1.8  | (a) Comparison of quantization noise PSD (single-sided) with Nyquist-<br>rate sampling and oversampling (b) Noise shaping achieved in delta-<br>sigma modulators                                                         | 9        |

| 1.9  | Functional block diagram of a first order Delta-Sigma modulator                                                                                                                                                          | 10       |

| 1.10 | Linearized model of a first order delta-sigma modulator                                                                                                                                                                  | 11       |

| 1.11 | Input and output waveforms of a 4-bit modulator employing an accu-<br>mulator as the loop filter. The inset is a zoomed in version showing how<br>well the output signal tracks the input. The quantizer step size is 2. | 12       |

| 1.12 | Linearized model for higher order delta-sigma modulators                                                                                                                                                                 | 13       |

| 1.13 | (a) Cascade of Integrators Feedforward (CIFF) architecture (b) Cascade of Integrators Feedback (CIFB) architecture                                                                                                       | 14       |

| 1.14 | Variation in the magnitude response of an all zero NTF $((1-z^{-1})^L)$ for different orders. The inset compares the low frequency responses.                                                                            | 15       |

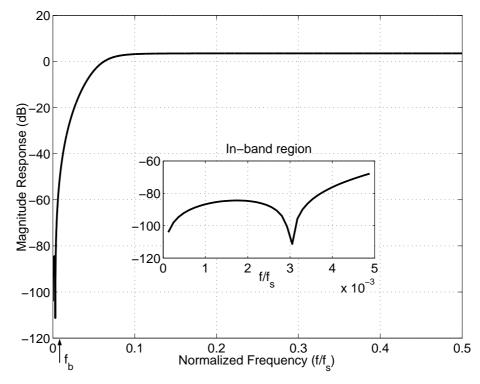

| 1.15 | Magnitude response of a typical third order NTF with an OBG of 1.5.<br>The inset shows the presence of in-band complex zeros                                                                                             | 18       |

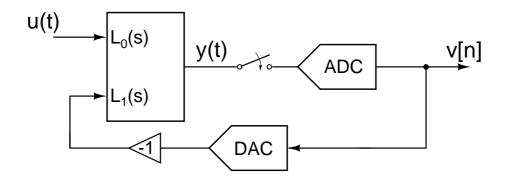

| 1.16 | Functional block diagram of a Continuous-Time Delta-Sigma Modula-<br>tor                                                                                                                                                 | 19       |

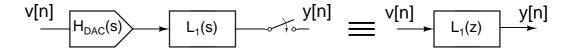

| 1.17 | Equivalence between continuous-time and discrete-time loop filter ( $H_{DAC}$ ) denotes the Laplace transform of the DAC pulse shape)                                                                                    | s)<br>21 |

|      |                                                                                                                                                                                                                          |          |

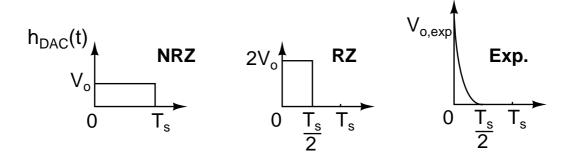

| 1.18 | Commonly used DAC pulse shapes                                                                                                                                                                                                                    | 22 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

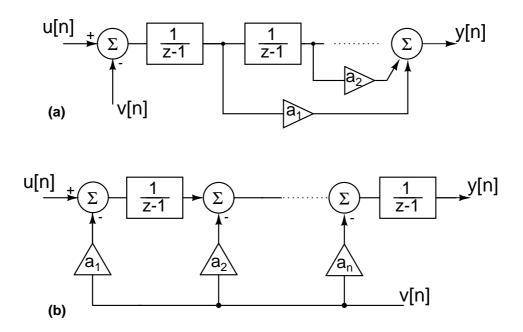

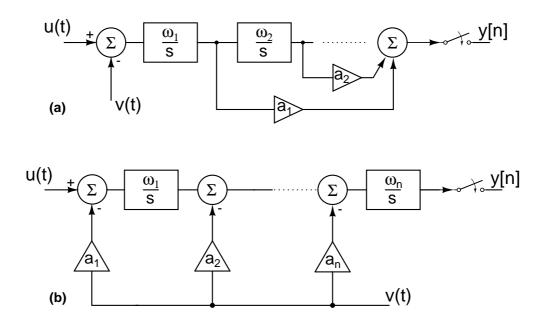

| 1.19 | Implementation of the continuous time loop filter using (a) Cascade of<br>Integrators Feedforward (CIFF) architecture and (b) Cascade of Inte-<br>grators Feedback (CIFB) architecture                                                            | 23 |

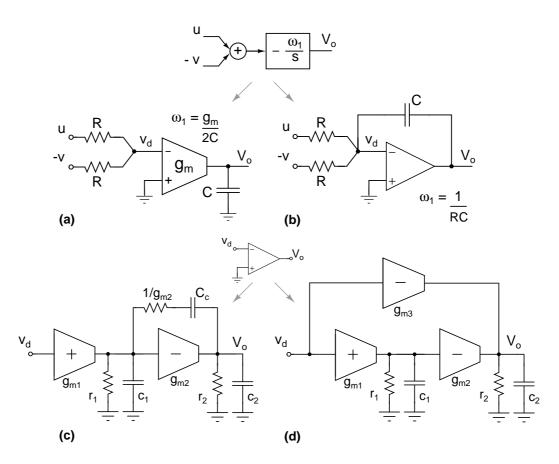

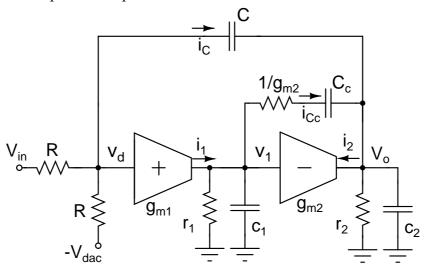

| 1.20 | Input stage of a CTDSM implemented using (a) $G_m$ -C integrator (b) active-RC integrator. Small-signal circuit models of (c) Miller compensated opamp (d) Feedforward compensated opamp $\ldots \ldots \ldots$                                   | 25 |

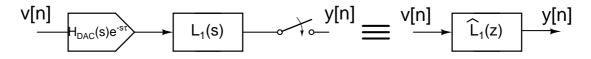

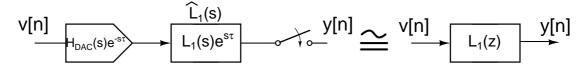

| 1.21 | Equivalence between continuous-time and (the modified) discrete-time loop filter $(\hat{L}_1(z))$ in the presence of delay $(\tau)$                                                                                                               | 26 |

| 1.22 | Conceptual model to compensate for excess loop delay                                                                                                                                                                                              | 27 |

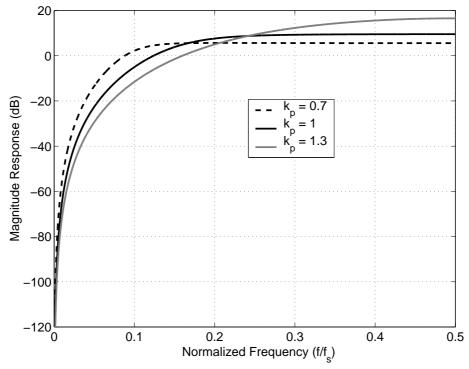

| 1.23 | Magnitude response of the NTF for different values of $k_p$                                                                                                                                                                                       | 28 |

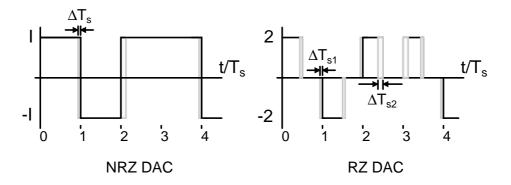

| 1.24 | Pulse width timing errors seen in NRZ and RZ DAC waveforms of a single-bit CTDSM                                                                                                                                                                  | 30 |

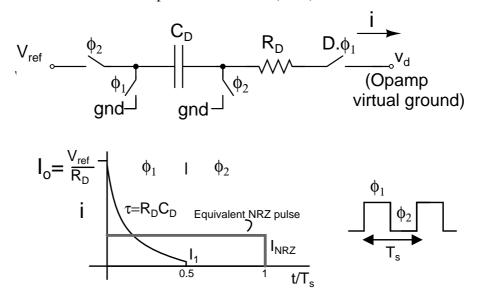

| 1.25 | SCR DAC schematic and the exponentially decaying pulse produced by the DAC                                                                                                                                                                        | 32 |

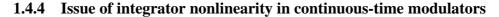

| 1.26 | Input-output characteristic of (a) a linear transconductor and (b) a non-<br>linear transconductor                                                                                                                                                | 33 |

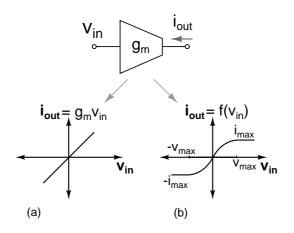

| 1.27 | (a) Block diagram of the input stage of a CTDSM including the first integrator, along with typical swings observed for $u(t)-v(t)$ for different number of quantizer bits (b) N = 1 (c) N = 2 (d) N = 3. (Full scale range of the quantizer is 2) | 34 |

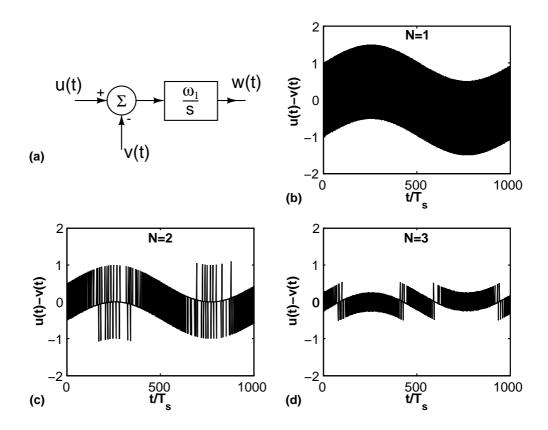

| 1.28 | A nonlinear $G_m$ -C implementation of the first integrator                                                                                                                                                                                       | 36 |

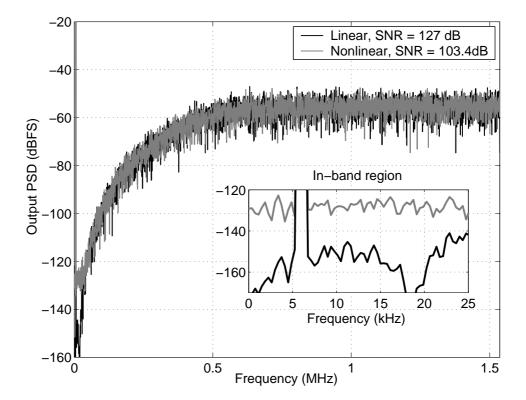

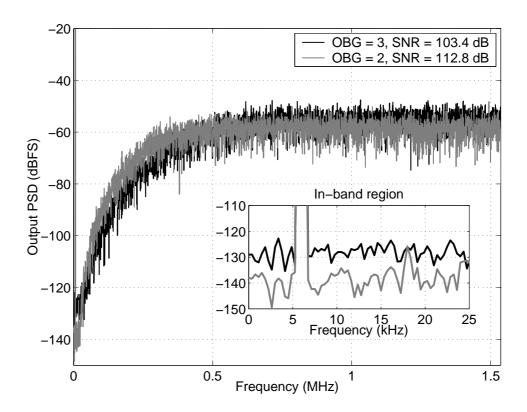

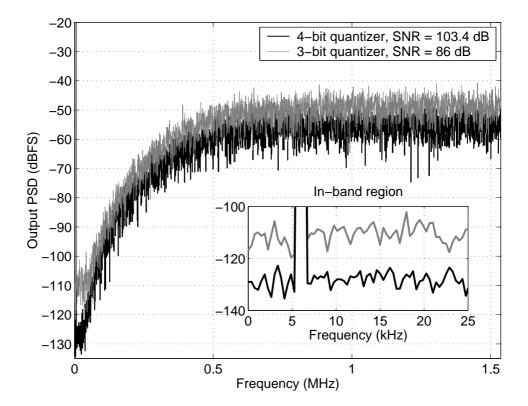

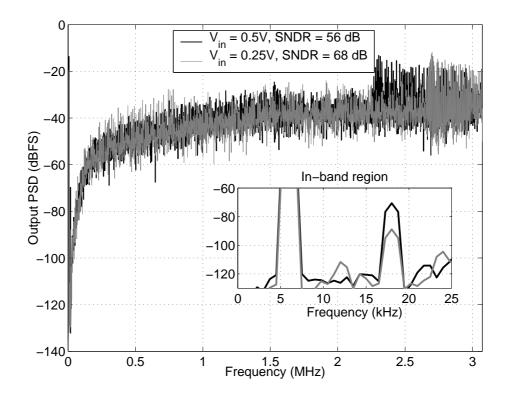

| 1.29 | Simulated PSD of a third order CTDSM with and without nonlinearity in the $G_m$ -C integrator. Comparison of the in-band noise floor is shown in the inset.                                                                                       | 37 |

| 1.30 | Simulated PSD of a third order CTDSM with a nonlinear transconduc-<br>tor for different OBGs.                                                                                                                                                     | 38 |

| 1.31 | Simulated PSD of a third order CTDSM with a nonlinear transconduc-<br>tor for different quantizer levels                                                                                                                                          | 38 |

| 1.32 | Simulated PSD of a third order single-bit CTDSM showing the har-<br>monic distortion limited performance for two different input amplitudes                                                                                                       | 39 |

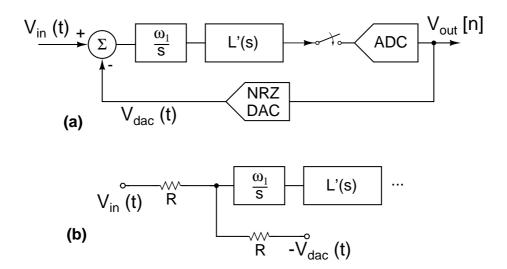

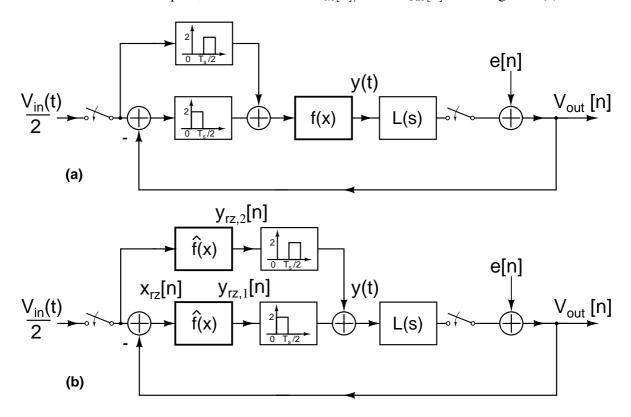

| 2.1  | (a) Block diagram of a modulator with CIFF loop filter and (b) the input stage with a resistive DAC implementation.                                                                                                                               | 43 |

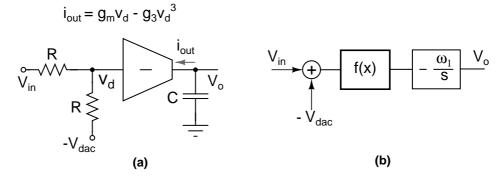

| 2.2  | (a) Circuit of the input stage of a CTDSM using a nonlinear $G_m$ -C integrator and (b) its equivalent model.                                                                                                                                     | 44 |

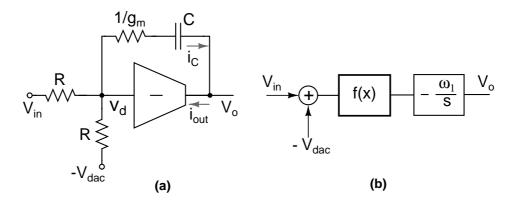

| 2.3  | (a) Circuit of the input stage of a CTDSM using a nonlinear single-stage active-RC integrator and (b) its equivalent model.                                                                                                                       | 45 |

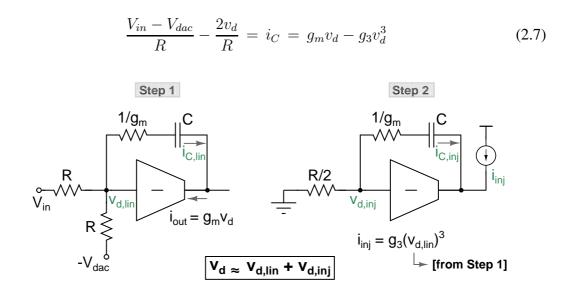

| 2.4  | Circuit topologies in each step of the current injection method                                                                                                                                                                                                                                                                             | 46 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.5  | Circuit of the input stage of a CTDSM using an active-RC integrator with a two-stage Miller compensated opamp.                                                                                                                                                                                                                              | 48 |

| 2.6  | Circuit of the first integrator of a CTDSM with the responses (currents) shown at each node given a step input. Initial transients are neglected assuming a fast opamp.                                                                                                                                                                     | 49 |

| 2.7  | Injection of a step-like nonlinear current $(i_{inj})$ at the output of the input transconductor in an active-RC integrator with Miller opamp. Initial transients have been neglected.                                                                                                                                                      | 50 |

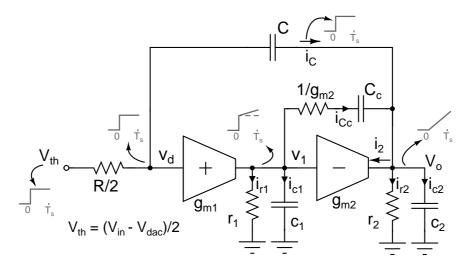

| 2.8  | Circuit of the first integrator of a CTDSM with finite $r_1$ and $r_2$ . The responses (currents) at each node are shown for a given step input, neglecting the initial transients.                                                                                                                                                         | 52 |

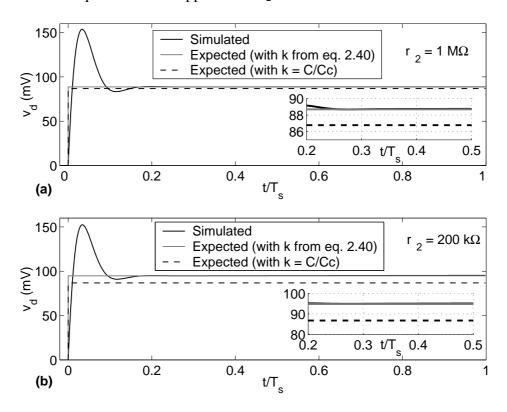

| 2.9  | Simulated and expected step response at $v_d$ for the Miller opamp based<br>integrator with $g_{m1} = 27.12 \ \mu$ S, $R = 100 \ \text{k}\Omega$ , $C = 527 \ \text{fF}$ , $C_c = 150 \ \text{fF}$ ,<br>$g_{m2} = 60 \ \mu$ S for (a) $r_2 = 1 \ \text{M}\Omega$ (b) $r_2 = 200 \ \text{k}\Omega$ . The insets show the<br>zoomed-in views. | 54 |

| 2.10 | Circuit of an active-RC integrator with a two-stage feedforward com-<br>pensated opamp.                                                                                                                                                                                                                                                     | 56 |

| 2.11 | CTDSM with nonlinearity in the first integrator                                                                                                                                                                                                                                                                                             | 59 |

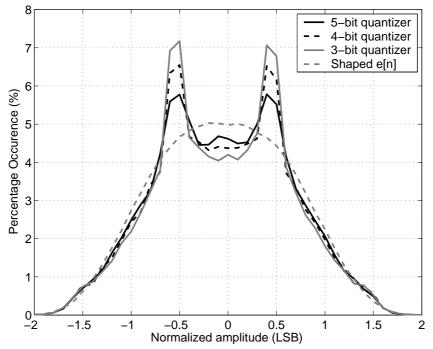

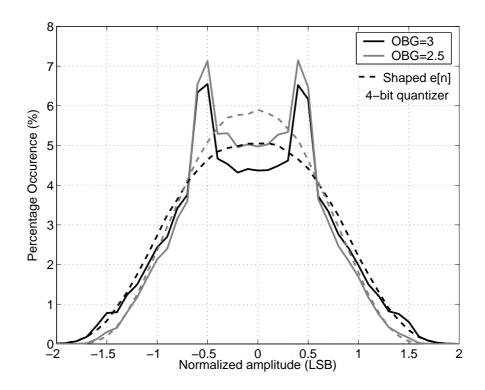

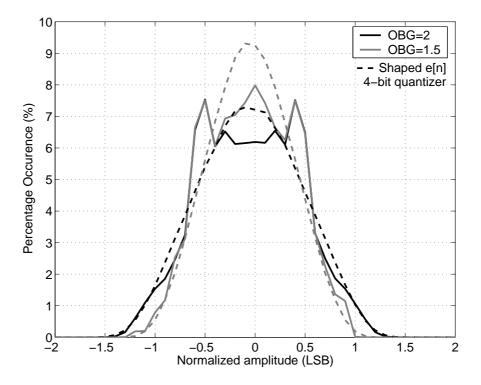

| 2.12 | Observed histogram of samples of $x[n]$ for various quantizer levels. Expected distribution of noise shaped $e[n]$ is also shown for comparison.                                                                                                                                                                                            | 60 |

| 2.13 | Observed histogram of samples of $x[n]$ for various OBGs. The expected distribution is shown as dashed-lines                                                                                                                                                                                                                                | 61 |

| 2.14 | Observed histogram of samples of $x[n]$ for various OBGs. The expected distribution is shown as dashed-lines                                                                                                                                                                                                                                | 61 |

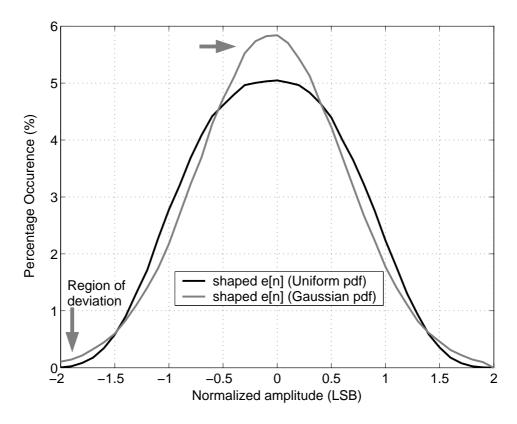

| 2.15 | Comparison of the expected distribution of noise shaped $e[n]$ having<br>either uniform or Gaussian distribution. The regions where the two<br>distributions differ have been indicated.                                                                                                                                                    | 62 |

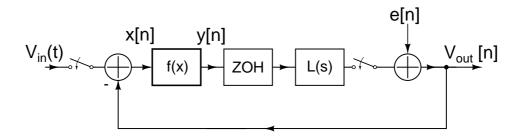

| 2.16 | Equivalent model of the CTDSM for slow inputs                                                                                                                                                                                                                                                                                               | 63 |

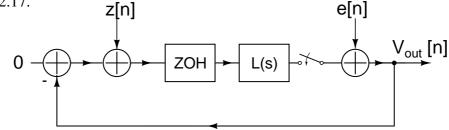

| 2.17 | Model for nonlinearity analysis of the CTDSM for the zero input case.                                                                                                                                                                                                                                                                       | 63 |

| 2.18 | Assumed PSD of the shaped quantization noise                                                                                                                                                                                                                                                                                                | 64 |

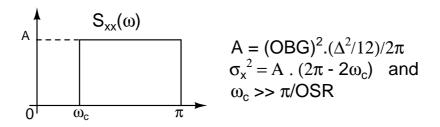

| 2.19 | CTDSM employing RZ DAC with nonlinearity in the first integrator                                                                                                                                                                                                                                                                            | 66 |

| 2.20 | (a) CTDSM employing RZ DAC with zero input (b) Equivalent model for the CTDSM with a nonlinear first integrator, for zero inputs                                                                                                                                                                                                            | 67 |

| 2.21 | (a) Model for the CTDSM employing RZ DAC with non zero input and (b)its equivalent representation                                                                                                                                                                                                                                           | 68 |

| 2.22 | Equivalent model for the CTDSM employing RZ DAC with a nonlinear first integrator                                                                                                                                                                                                                                                           | 70 |

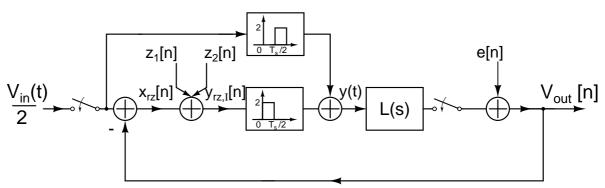

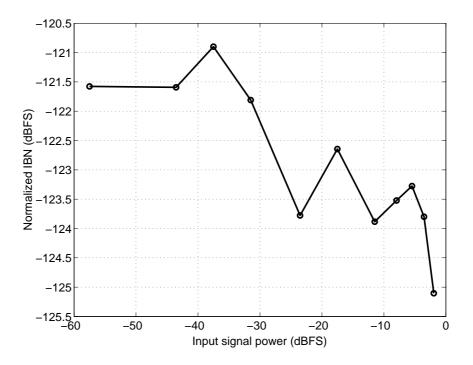

| 2.23 | In-band power spectral density of the modulator output with a linear<br>and nonlinear active-RC integrator. Predicted spectral density obtained<br>using current injection method is also shown.                                                                                                                                                                                                                                                                  | 72 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

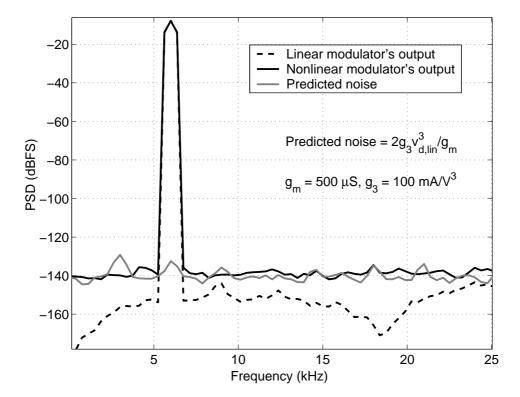

| 2.24 | Variation of IBN with varying input signal power.                                                                                                                                                                                                                                                                                                                                                                                                                 | 73 |

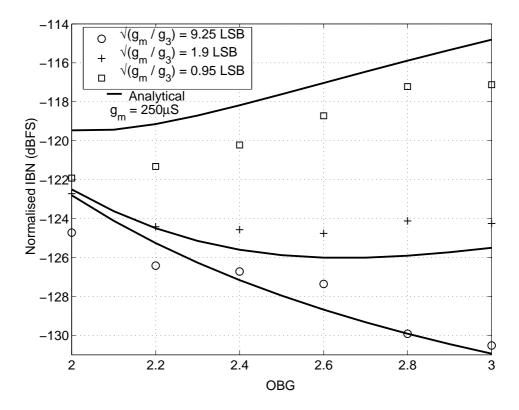

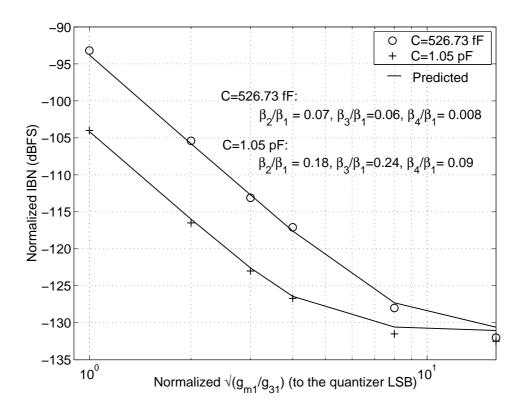

| 2.25 | Variation of IBN with OBG for different levels of transconductor non-<br>linearity. The solid lines are the analytically computed results, while<br>the points denote results from macromodel simulations                                                                                                                                                                                                                                                         | 74 |

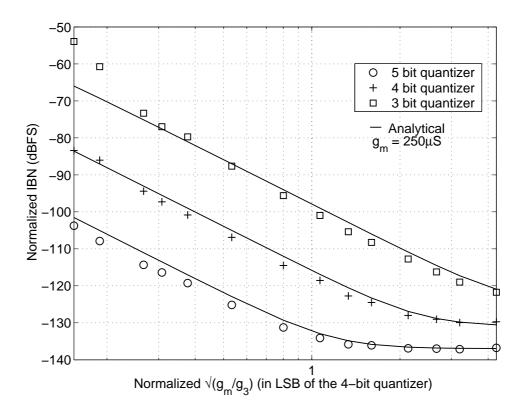

| 2.26 | IBN as a function of nonlinearity for different quantizer resolutions.                                                                                                                                                                                                                                                                                                                                                                                            | 75 |

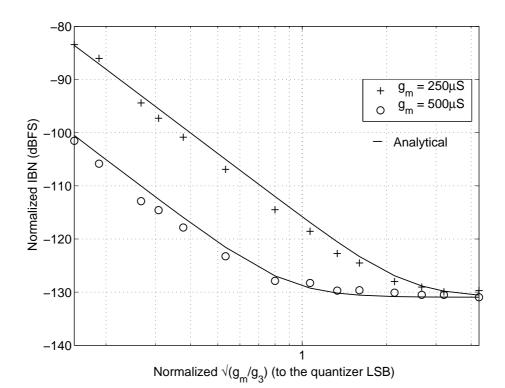

| 2.27 | Variation of IBN with nonlinearity for two values of $g_m$                                                                                                                                                                                                                                                                                                                                                                                                        | 76 |

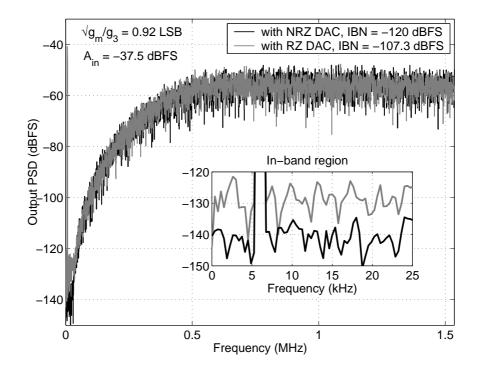

| 2.28 | Comparison of output PSD of NRZ and RZ modulator with a nonlinear single-stage active-RC integrator ( $g_m = 500 \mu$ S).                                                                                                                                                                                                                                                                                                                                         | 77 |

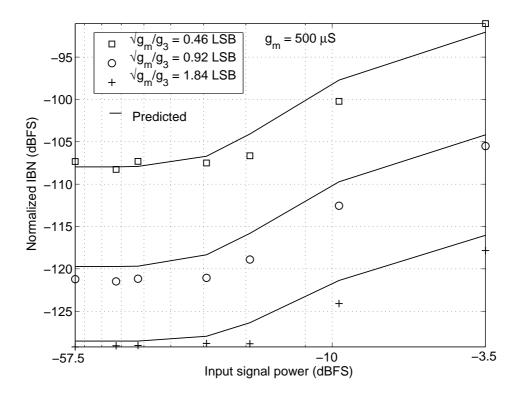

| 2.29 | Variation of IBN with an RZ DAC, for varying input signal power and nonlinearity in the single-stage transconductor based active-RC integrator.                                                                                                                                                                                                                                                                                                                   | 77 |

| 2.30 | Variation of IBN with a two-stage Miller compensated opamp due to nonlinearity in the input transconductor.                                                                                                                                                                                                                                                                                                                                                       | 78 |

| 2.31 | Variation of IBN with a feedforward compensated opamp                                                                                                                                                                                                                                                                                                                                                                                                             | 78 |

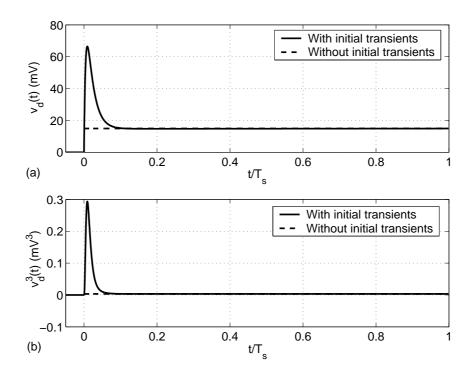

| 2.32 | Response at the virtual ground node of the active-RC integrator with feedforward compensated opamp, to a step input. (a) $v_d(t)$ (b) $v_d^3(t)$                                                                                                                                                                                                                                                                                                                  | 80 |

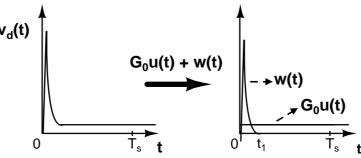

| 3.1  | Step response at the virtual ground node of an active-RC integrator with two-stage opamp, considered as having two components - $G_0u(t)$ and $w(t)$                                                                                                                                                                                                                                                                                                              | 81 |

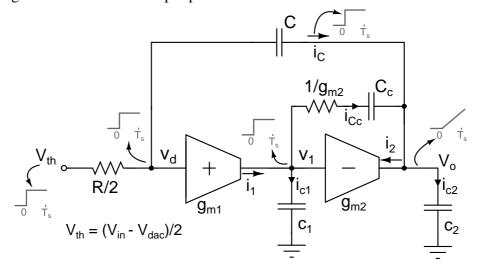

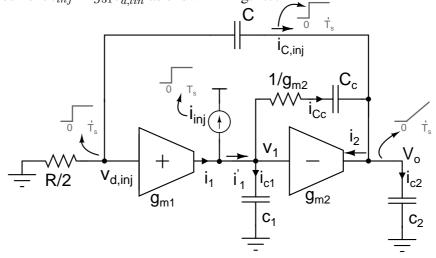

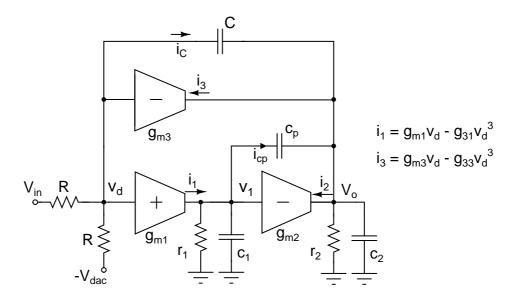

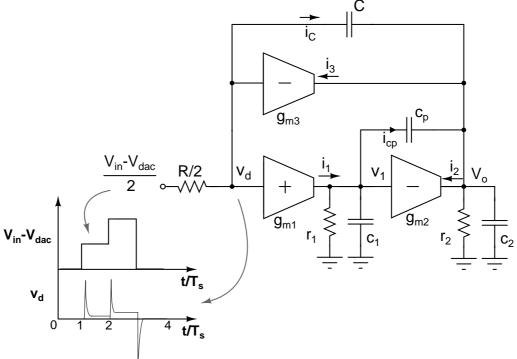

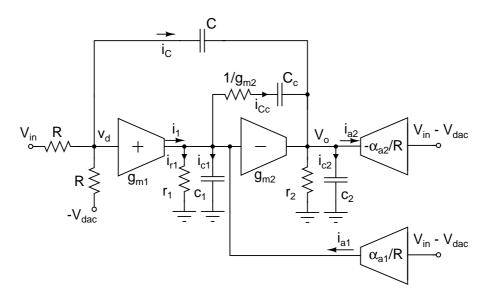

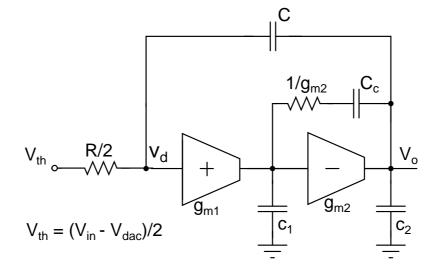

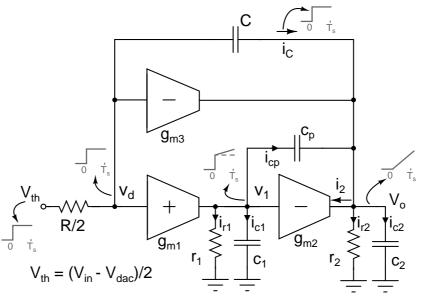

| 3.2  | Circuit of an active-RC integrator with a two-stage feedforward compensated opamp used in a multi-bit CTDSM with an NRZ DAC                                                                                                                                                                                                                                                                                                                                       | 82 |

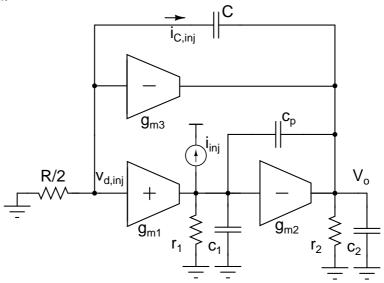

| 3.3  | Injection of nonlinear current $(i_{inj})$ due to the input transconductor in an active-RC integrator with two-stage feedforward compensated opamp.                                                                                                                                                                                                                                                                                                               | 83 |

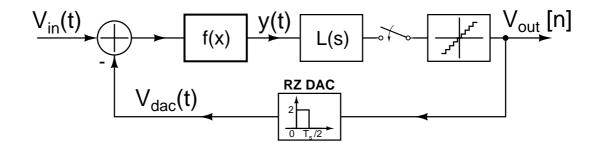

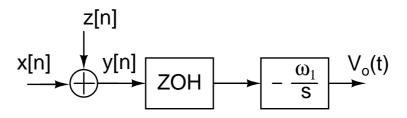

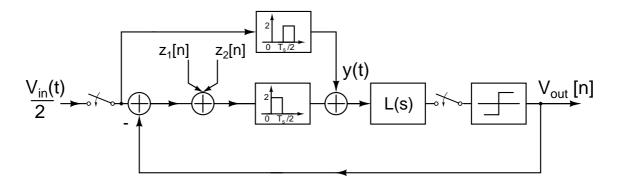

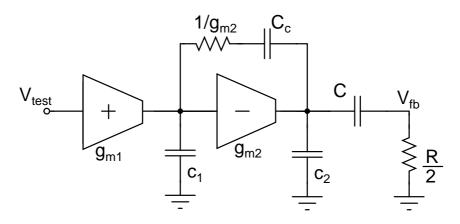

| 3.4  | Model of the nonlinear active-RC integrator with $z[n] = \sum_{i=1}^{4} z_i[n]$ , that includes the effect of initial transients in the in-band region                                                                                                                                                                                                                                                                                                            | 86 |

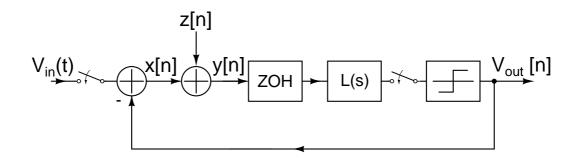

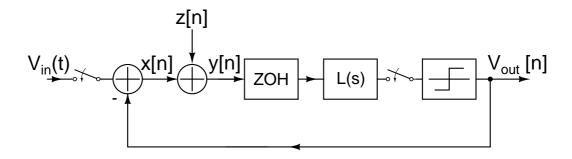

| 3.5  | Model of the CTDSM with a nonlinear integrator where $z[n] = \sum_{i=1}^{4} z_i[n]$ includes the effect of initial transients. The model can be used to predict the in-band noise due integrator nonlinearity.                                                                                                                                                                                                                                                    | 87 |

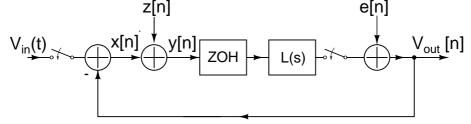

| 3.6  | Comparison between the spectrum of the exact and approximate version<br>of $v_{d,lin}(t)^3$ obtained with a feedforward opamp based integrator. $g_{m1} =$<br>27.12 $\mu$ S, $R = 100 \text{ k}\Omega$ , $C = 527 \text{ fF}$ , $c_1 = 45 \text{ fF}$ , $c_p = 10 \text{ fF}$ , $g_{m2} = 100 \mu$ S,<br>$c_2 = 250 \text{ fF}$ , $g_{m3} = 320 \mu$ S, $r_2 = 1 \text{ M}\Omega$ . The inset shows the matching<br>between the two spectra in the in-band region | 90 |

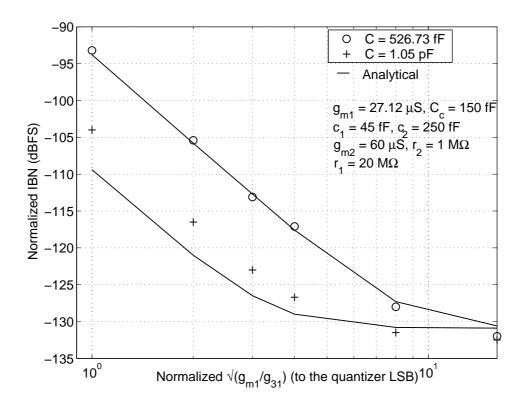

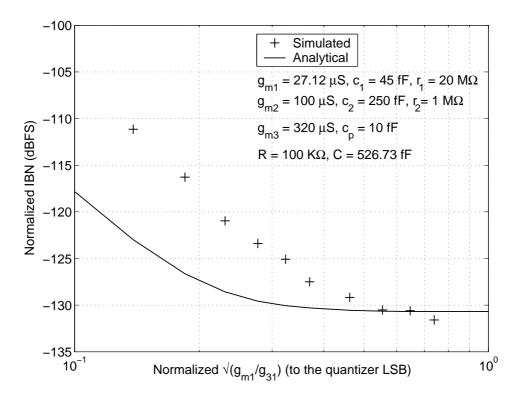

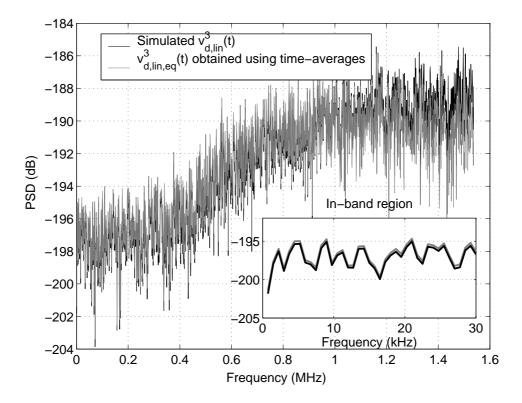

| 3.7  | Comparison of the IBN estimated with and without including the effect of initial transients for the feedforward opamp based integrator                                                                                                                                                                                                                                                                                                                            | 92 |

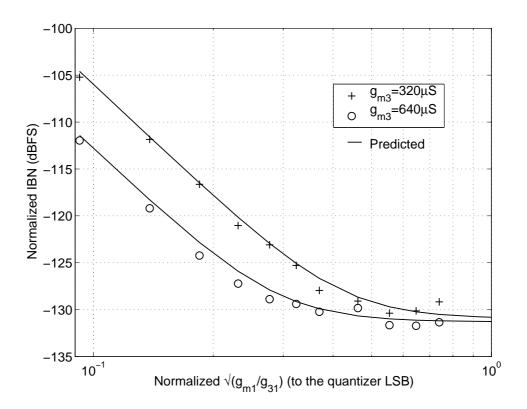

| 3.8  | Variation in IBN with a feedforward opamp based integrator for two values of $g_{m3}$ .                                                                                                                         | 93  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

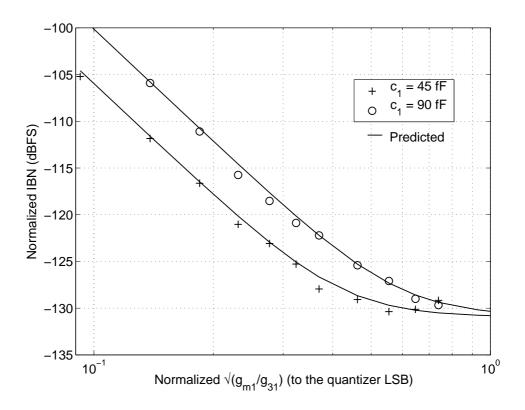

| 3.9  | Variation in IBN with a feedforward opamp based integrator for two values of $c_1$                                                                                                                              | 93  |

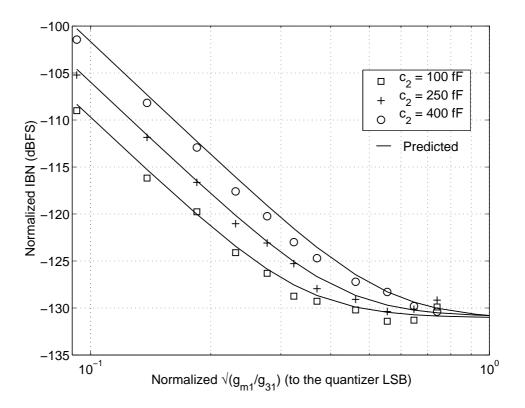

| 3.10 | Variation in IBN with feedforward opamp based integrator for various $c_2$                                                                                                                                      | 94  |

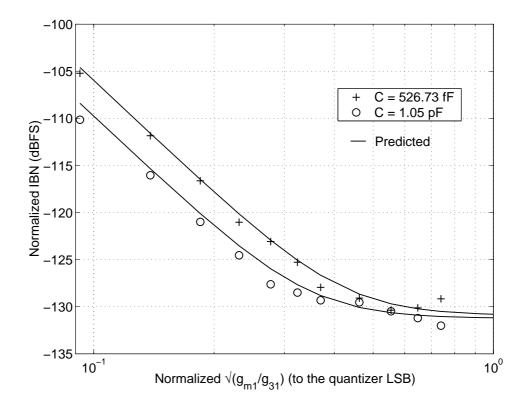

| 3.11 | Variation in IBN with a feedforward opamp based integrator for two values of integrating capacitors.                                                                                                            | 94  |

| 3.12 | Variation in IBN with Miller opamp based integrator for two values of $C. \ldots \ldots$ | 95  |

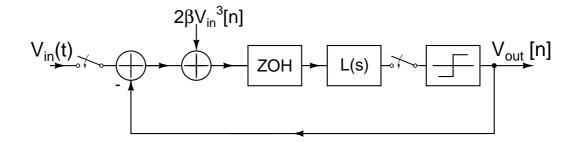

| 4.1  | Model of a single-bit CTDSM with nonlinear $G_m$ -C and active-RC integrators with a single-stage transconductor.                                                                                               | 99  |

| 4.2  | Equivalent model of the single-bit CTDSM with nonlinear single-stage integrators.                                                                                                                               | 100 |

| 4.3  | Model of a single-bit CTDSM with nonlinear single-stage integrator<br>and an RZ DAC                                                                                                                             | 100 |

| 4.4  | Equivalent model of the single-bit CTDSM with nonlinear single-stage integrators                                                                                                                                | 101 |

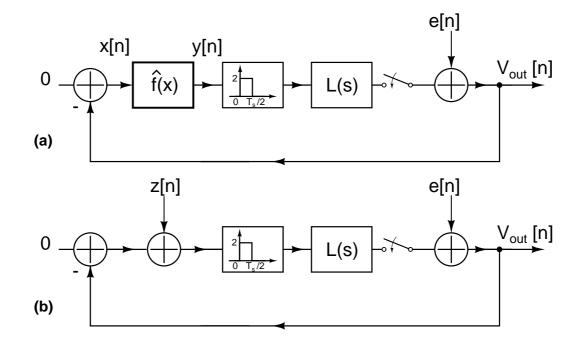

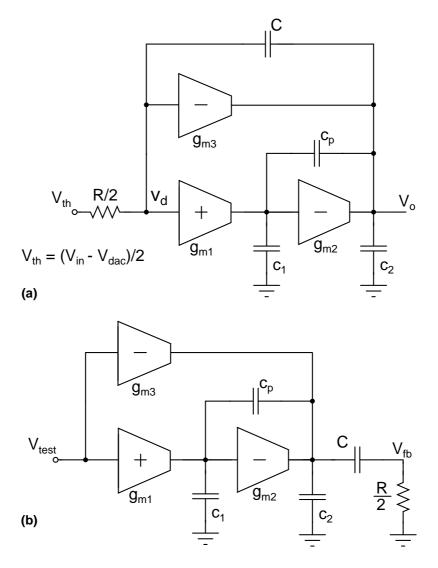

| 4.5  | Model of a single-bit CTDSM with nonlinear two-stage opamp based active-RC integrators, where $z[n] = \sum z_i[n]$ (i=1,2,3,4).                                                                                 | 102 |

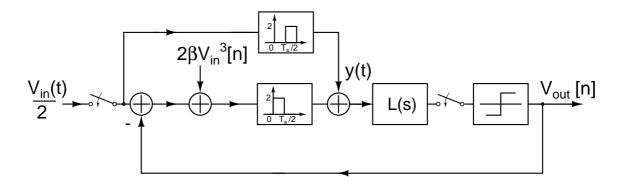

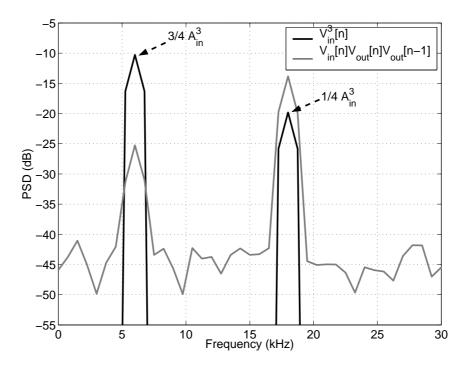

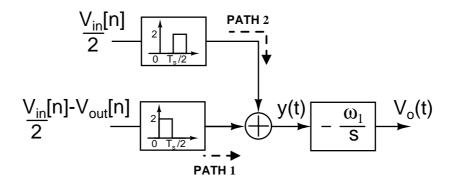

| 4.6  | In-band PSD of $V_{in}^3[n]$ and $V_{in}[n]V_{out}[n]V_{out}[n-1]$ , with 6 kHz being the input frequency.                                                                                                      | 105 |

| 4.7  | Model for the input stage of a CTDSM with an RZ feedback DAC and a linear first integrator.                                                                                                                     | 106 |

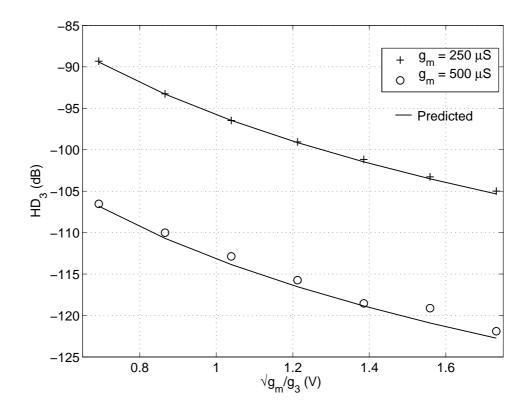

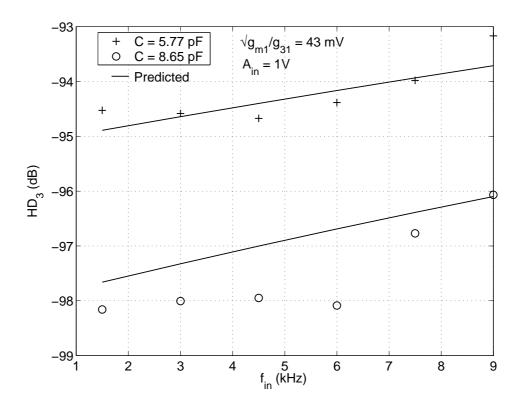

| 4.8  | Variation of $HD_3$ with a single-stage transconductor based active-RC integrator for two values of $g_m$ .                                                                                                     | 109 |

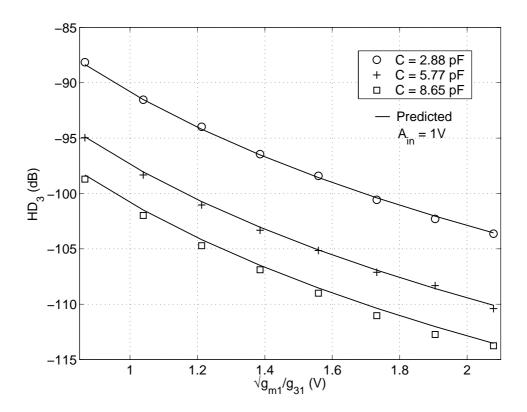

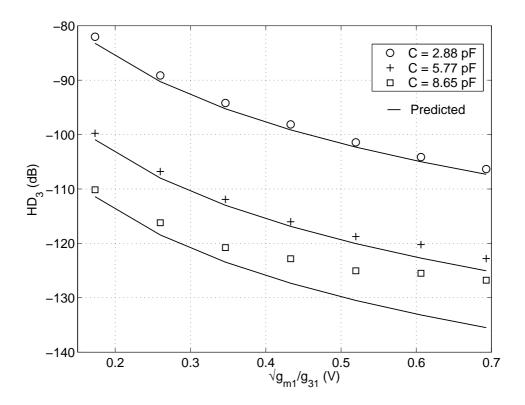

| 4.9  | Variation of $HD_3$ with Miller compensated opamp due to nonlinearity<br>in the input transconductor for different integrating capacitors                                                                       | 111 |

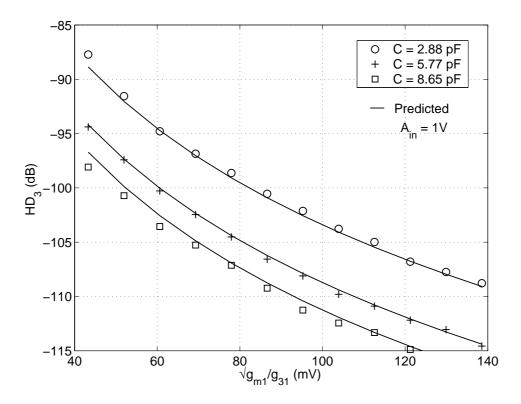

| 4.10 | Variation of $HD_3$ with feedforward compensated opamp due to nonlinearity in the input transconductor for different integrating capacitors.                                                                    | 111 |

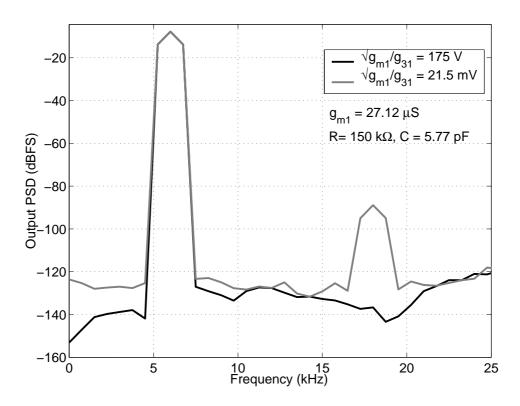

| 4.11 | In-band PSD of the modulator output showing the increase in noise floor at high nonlinearities                                                                                                                  | 112 |

| 4.12 | Variation of $HD_3$ (with feedforward compensated opamp) as a function of the input frequency for different values of integrating capacitors.                                                                   | 113 |

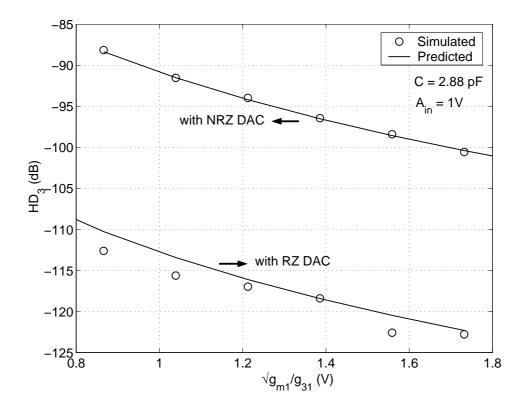

| 4.13 | Variation of $HD_3$ with a Miller compensated opamp as function of non-<br>linearity in the input transconductor, in modulators with NRZ and RZ<br>DAC                                                          | 113 |

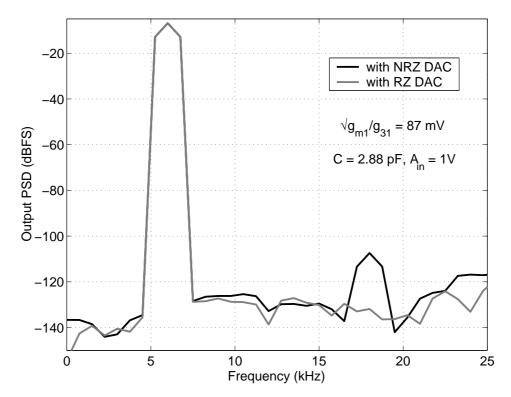

| 4.14 | In-band PSD of the single-bit CTDSM employing a nonlinear feedfor-<br>ward opamp based active-RC integrator, comparing the performance<br>with NRZ and RZ DAC                                                                                                                                                                                                     | 114      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

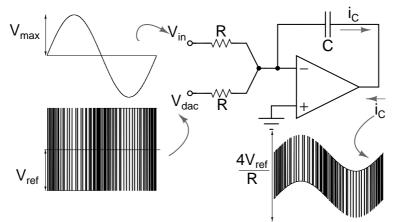

| 5.1  | Schematic and waveforms in a conventional integrator                                                                                                                                                                                                                                                                                                              | 117      |

| 5.2  | Assisted opamp integrator                                                                                                                                                                                                                                                                                                                                         | 118      |

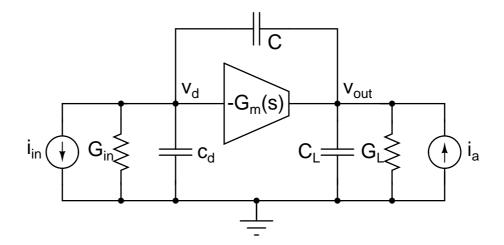

| 5.3  | Equivalent circuit of an assisted opamp integrator                                                                                                                                                                                                                                                                                                                | 119      |

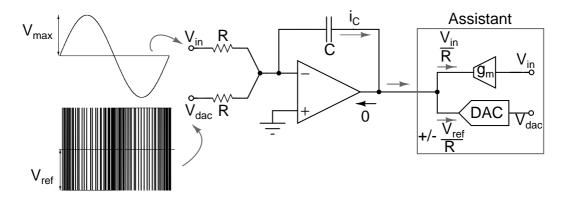

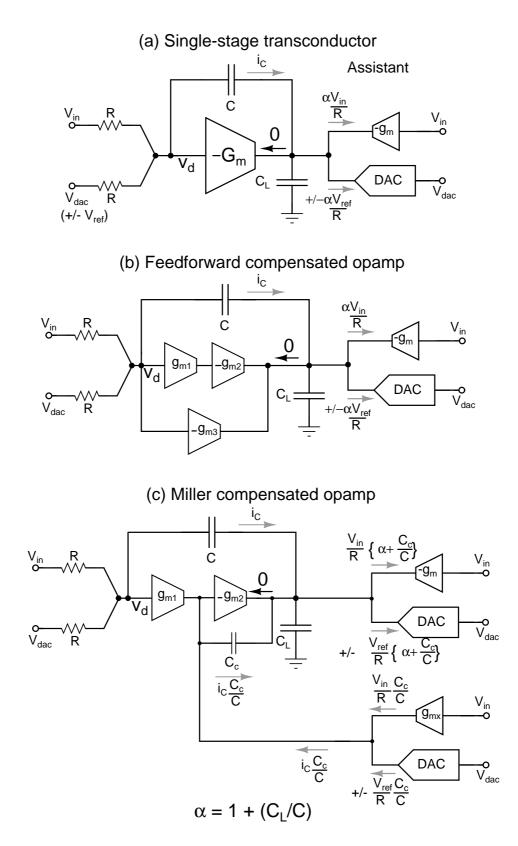

| 5.4  | Implementation of the assisted opamp integrator for several commonly<br>used opamp topologies - (a) A single stage transconductor (b) A two-<br>stage feedforward compensated opamp and (c) A Miller compensated<br>opamp ( $\alpha = 1 + C_L/C$ )                                                                                                                | 121      |

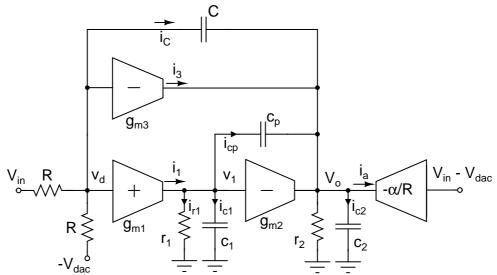

| 5.5  | Assisted active-RC integrator with feedforward compensated opamp                                                                                                                                                                                                                                                                                                  | 122      |

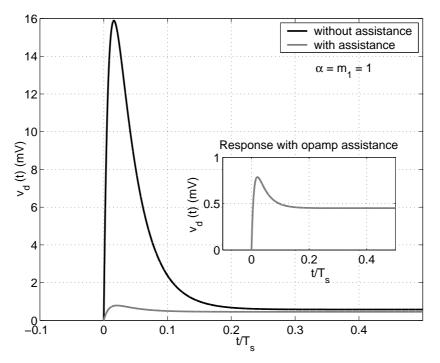

| 5.6  | Step response of the active-RC integrator with and without opamp as-<br>sistance ( $\alpha = m_1 = 1$ ). Inset shows a zoomed in view of the response<br>with assistance. $g_{m1} = 27.12 \mu$ S, $R = 150 k\Omega$ , $C = 5.77 \mu$ F, $r_1 = 20 M\Omega$ ,<br>$c_p = 10 \mu$ F, $g_{m2} = 100 \mu$ S, $g_{m3} = 320 \mu$ S, $c_1 = 45 \mu$ F, $r_2 = 1 M\Omega$ | 125      |

| 5.7  | Assisted active-RC integrator with Miller compensated opamp                                                                                                                                                                                                                                                                                                       | 125      |

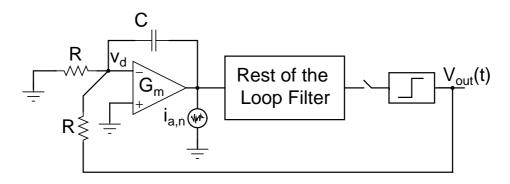

| 5.8  | Simplified diagram of the modulator used to evaluate the effect of noise of the assistant transconductor                                                                                                                                                                                                                                                          | 129      |

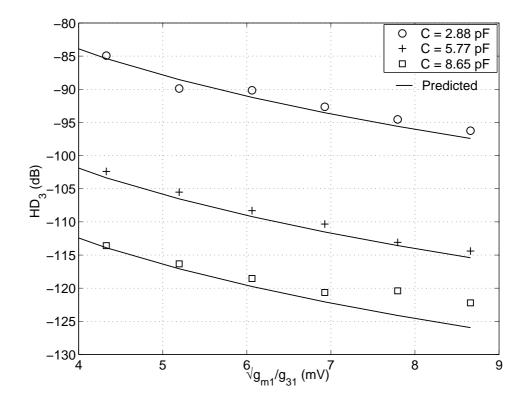

| 5.9  | Variation of $HD_3$ with feedforward compensated opamp with assistance.                                                                                                                                                                                                                                                                                           | 132      |

| 5.10 | Variation of $HD_3$ with Miller compensated opamp with assistance provided only to the second stage ( $m_{11} = 0, \alpha_{a2} = m_{12} = 1$ )                                                                                                                                                                                                                    | 133      |

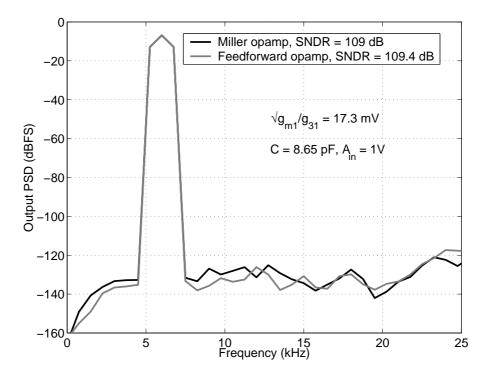

| 5.11 | In-band PSD of the single-bit CTDSM employing a nonlinear active-<br>RC integrator with both Miller and feedforward compensated opamps.<br>Assistance has been provided to both the stages of the Miller opamp. $(m_{11}$<br>$1, \alpha_{a2} = m_{12} = 1)$ .                                                                                                     | =<br>133 |

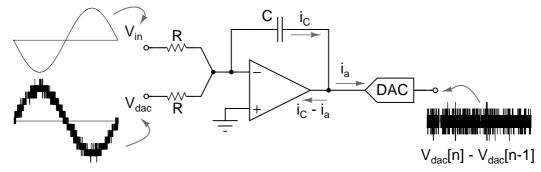

| 5.12 | Modified assisted opamp integrator in a multi-bit CTDSM                                                                                                                                                                                                                                                                                                           | 135      |

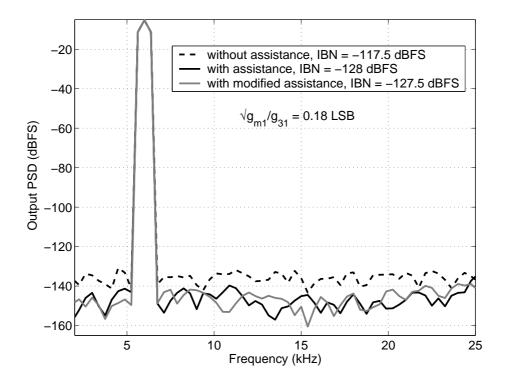

| 5.13 | Comparison of the in-band PSD of the output of a multi-bit CTDSM employing a nonlinear active-RC integrator having a feedforward compensated opamp, with and without opamp assistance. The PSD observed with modified opamp assistance is also shown                                                                                                              | 135      |

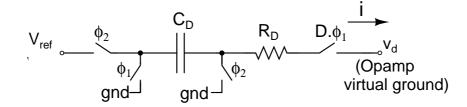

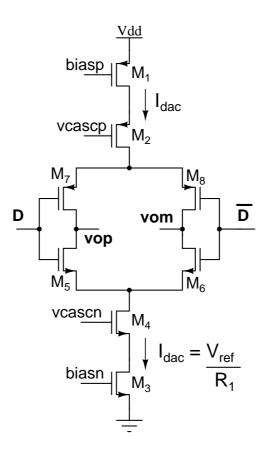

| 6.1  | Single-ended schematic of an SCR DAC                                                                                                                                                                                                                                                                                                                              | 139      |

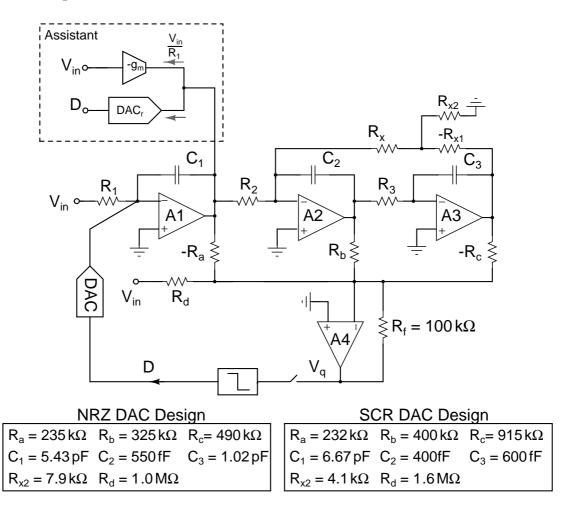

| 6.2  | Modulator architecture and component values (DAC is either NRZ or SCR)                                                                                                                                                                                                                                                                                            | 140      |

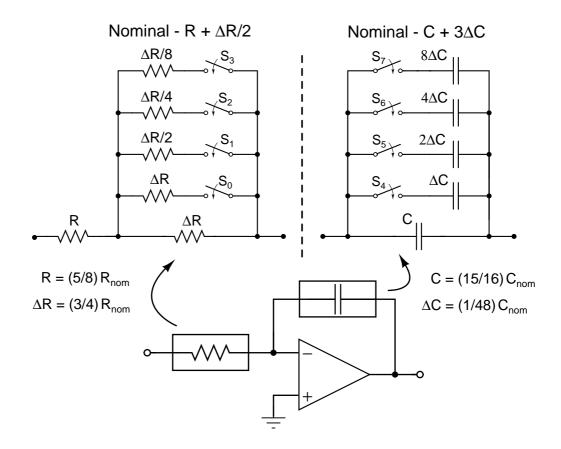

| 6.3  | Resistor and capacitor banks used in the integrators                                                                                                                                                                                                                                                                                                              | 143      |

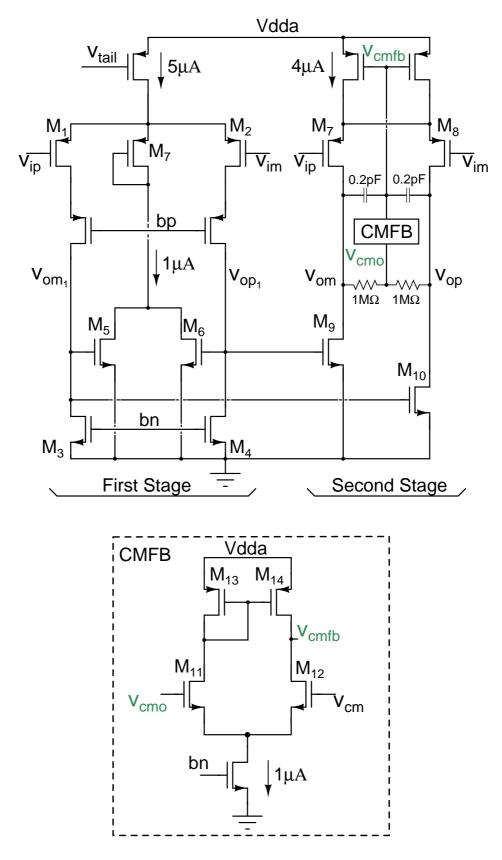

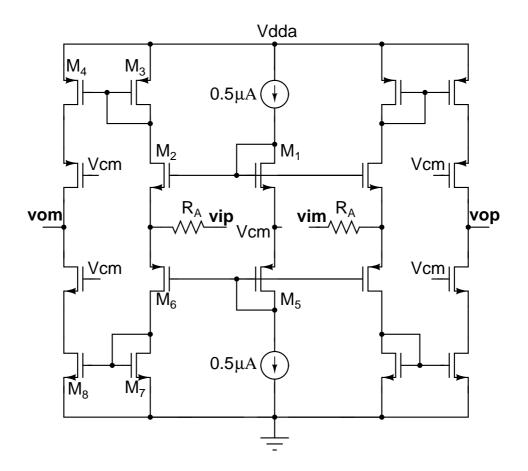

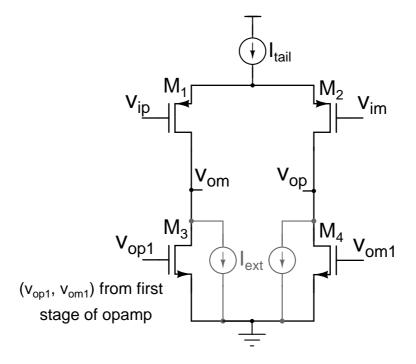

| 6.4  | Operational amplifier used in the first integrator                                                                                                                                                                                                                                                                                                                | 144      |

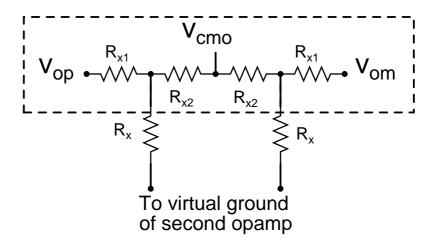

| 6.5  | Common mode feedback sensing used in third opamp $(R_{x1} \text{ and } R_{x2})$ to realize the T-network. Resistor $R_x$ is also shown for convenience.                                                | 146 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

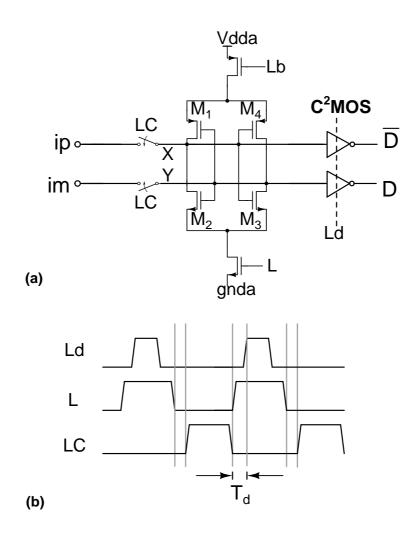

| 6.6  | (a) Comparator schematic and (b) Clock waveforms                                                                                                                                                       | 147 |

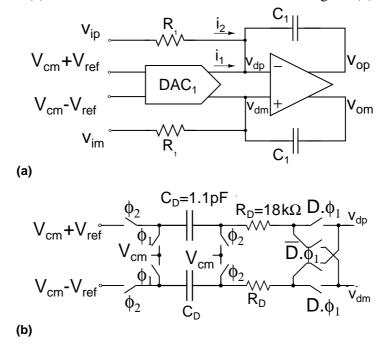

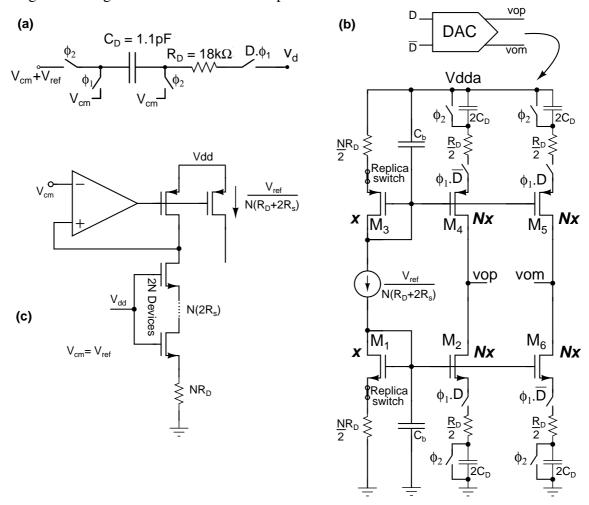

| 6.7  | <ul><li>(a) Schematic of the first integrator in the modulator with the SCR DAC</li><li>(b) Schematic of the differential SCR DAC</li></ul>                                                            | 148 |

| 6.8  | Transconductor used in the assistant circuit                                                                                                                                                           | 149 |

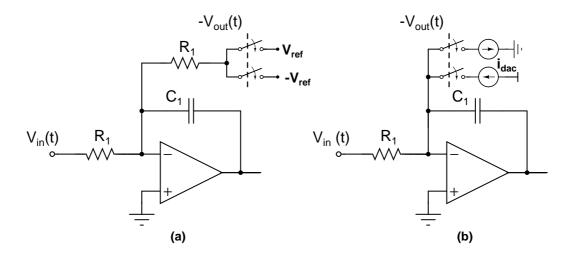

| 6.9  | Assistant DAC used in the NRZ modulator                                                                                                                                                                | 150 |

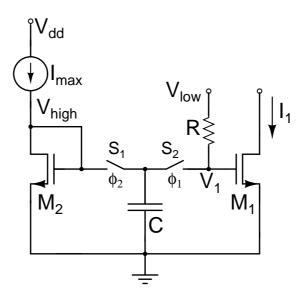

| 6.10 | Simplified schematic of an exponentially decaying pulse generator proposed in Ortmanns <i>et al.</i> (2003)                                                                                            | 151 |

| 6.11 | (a) Single branch of the SCR feedback DAC (b) Schematic of the SCR assistant DAC and (c) Simplified schematic of the bias current generator.                                                           | 152 |

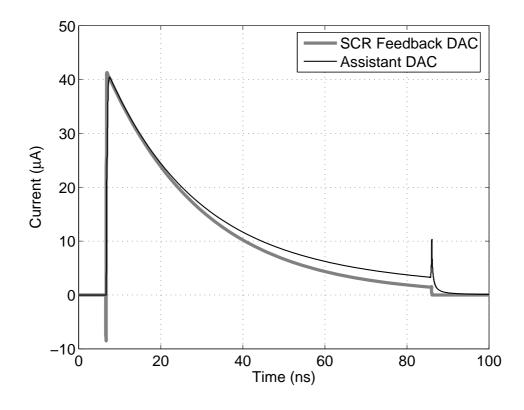

| 6.12 | Pulse shapes of the SCR feedback and assistant DACs                                                                                                                                                    | 154 |

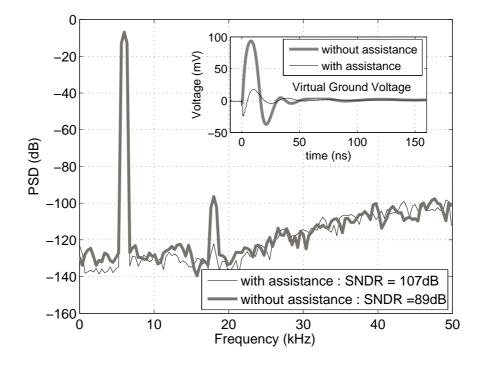

| 6.13 | Low frequency PSD of NRZ modulators using conventional and as-<br>sisted opamp integrators (with the same power consumption). The inset<br>shows the voltages at the virtual ground node in both cases | 156 |

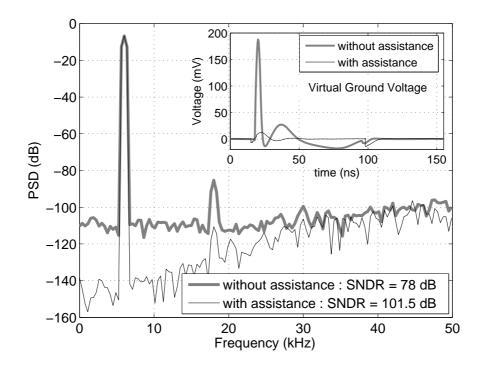

| 6.14 | Low frequency PSD of SCR modulators using conventional and as-<br>sisted opamp integrators (with the same power consumption). The inset<br>shows the voltages at the virtual ground node in both cases | 157 |

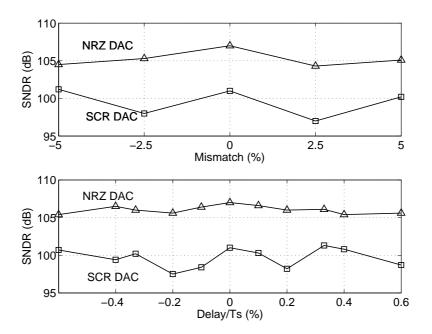

| 6.15 | Simulated performance of modulators employing assisted integrators with NRZ and SCR DACs, with $\pm 5\%$ mismatch and $\pm 1$ ns (0.6 %Ts) timing skew between feedback and assistant DACs.            | 158 |

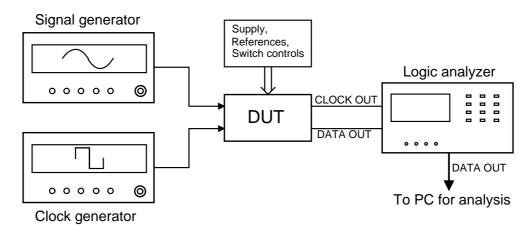

| 6.16 | Block diagram representation of the setup used for measuring the per-<br>formance of the modulators.                                                                                                   | 159 |

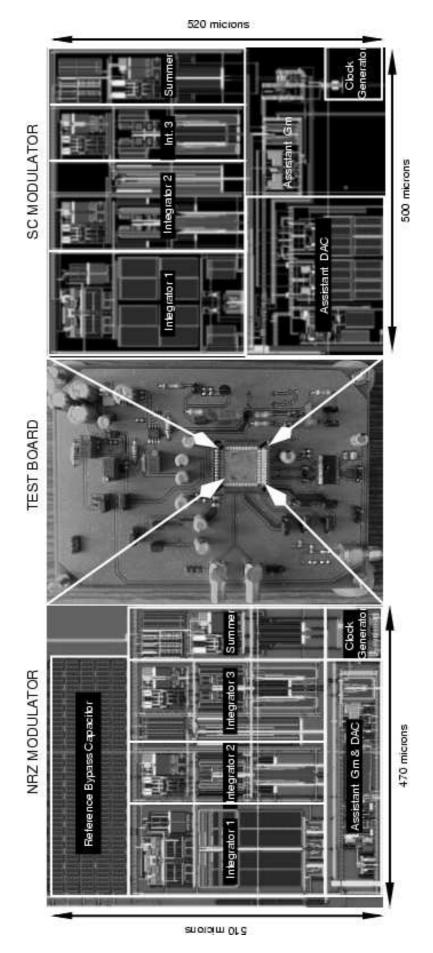

| 6.17 | Test board and chip layouts of the NRZ and SCR DAC based modula-<br>tors                                                                                                                               | 160 |

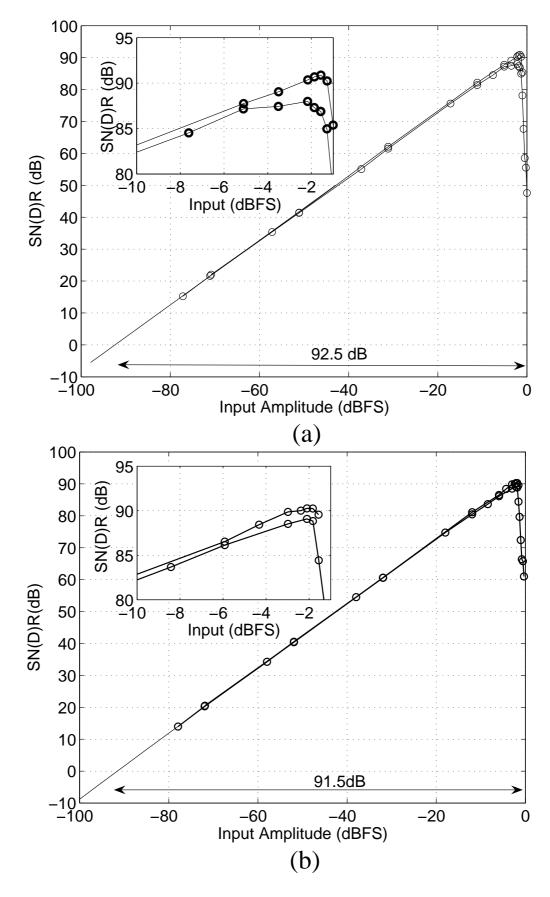

| 6.18 | Measured SNR and SNDR for the modulator with (a) an NRZ DAC and (b) an SCR DAC. The dynamic ranges are 92.5 dB and 91.5 dB respectively.                                                               | 162 |

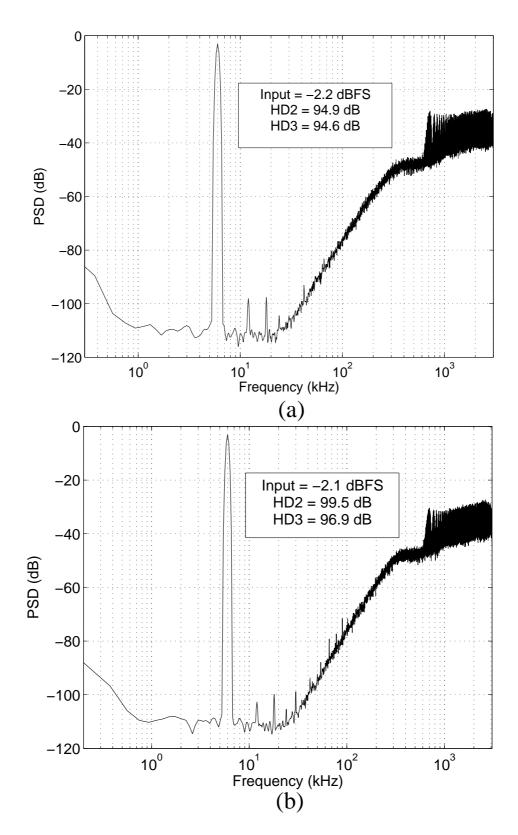

| 6.19 | Modulator output spectrum for a 6 kHz tone (a) for an NRZ DAC based modulator with -2.2 dBFS input and (b) for an SCR DAC based modulator with -2.1 dBFS input.                                        | 163 |

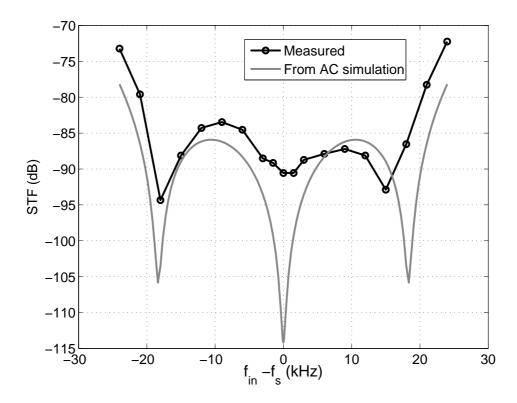

| 6.20 | Measured and simulated rejection in the first alias band (( $f_s$ - 24 kHz))<br>to ( $f_s$ + 24 kHz))                                                                                                  | 164 |

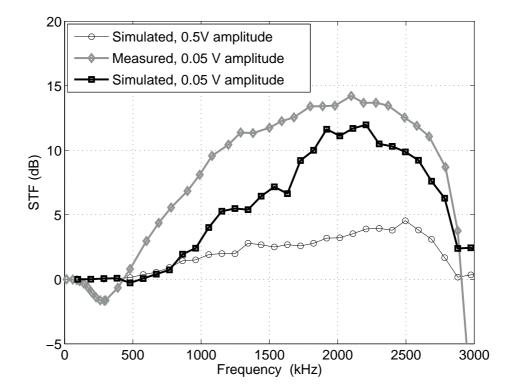

| 6.21 | Measured and simulated STF for out-of-band frequencies. The magni-<br>tude of the STF depends significantly on the input amplitude                                                                     | 164 |

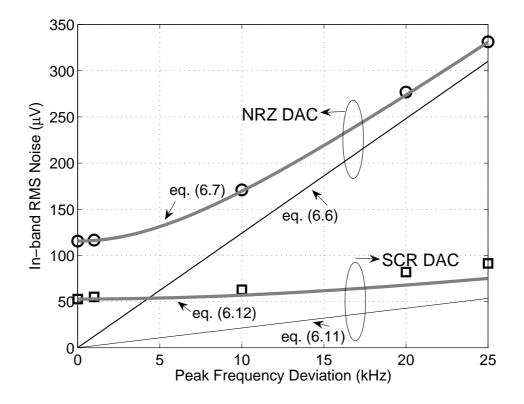

| 6.22        | Measured jitter performance of the NRZ and SCR modulators, with an FM modulated sinewave clock source. The upper and lower curves in gray are calculations using eq. 6.7 and 6.12 respectively.                      | 166 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

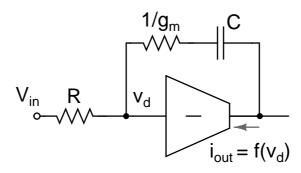

| A.1         | A nonlinear active-RC integrator.                                                                                                                                                                                    | 178 |

| A.2         | Injection of the nonlinear current $i_{inj2}$ to a linear active-RC integrator.                                                                                                                                      | 179 |

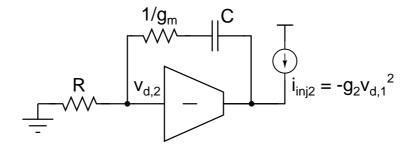

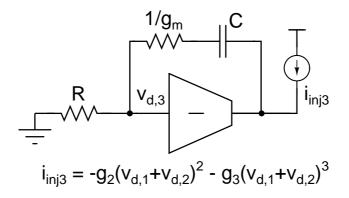

| A.3         | Injection of the nonlinear current $i_{inj3}$ to a linear active-RC integrator.                                                                                                                                      | 180 |

| <b>B</b> .1 | Active-RC integrator with a two-stage Miller compensated opamp .                                                                                                                                                     | 182 |

| B.2         | Open loop configuration of the active-RC integrator with two-stage<br>Miller compensated opamp                                                                                                                       | 183 |

| B.3         | (a) Active-RC integrator with a feedforward compensated opamp and its (b) open loop configuration used for stability analysis                                                                                        | 184 |

| B.4         | Second stage of a feedforward compensated opamp, showing the implementation of $g_{m2}$ and $g_{m3}$ sharing the same current                                                                                        | 186 |

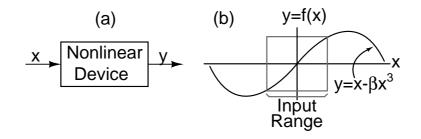

| C.1         | (a) Weakly nonlinear function $y = f(x) = x - \beta x^3$ (b) Input signal range relative to the transfer characteristic of the nonlinear function                                                                    | 188 |

| E.1         | Input stage of a single-bit CTDSM with (a) resistive DAC (b) current-<br>steering DAC                                                                                                                                | 193 |

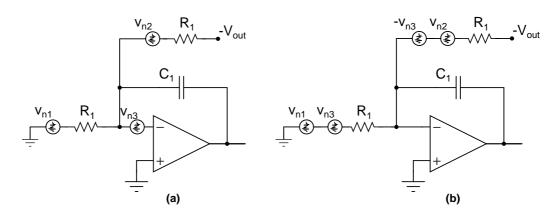

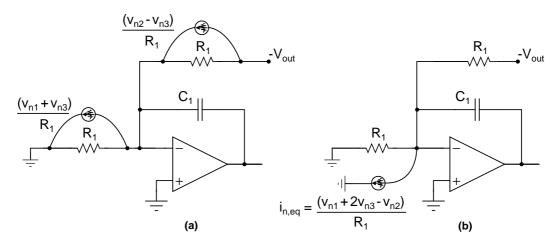

| E.2         | (a) Input stage of a CTDSM showing the critical noise sources and (b) the equivalent representation of the opamp noise.                                                                                              | 194 |

| E.3         | (a) Representation of the voltage noise sources in the input stage of a CTDSM with current noise sources and (b) the equivalent current noise source $(i_{n,eq})$ representing the contribution of the noise sources | 194 |

| E.4         | (a) Input stage of a CTDSM having a current-steering DAC along with the critical noise sources and (b) the equivalent current noise source $(i_{n,eq})$ representing the contribution of all the noise sources       | 195 |

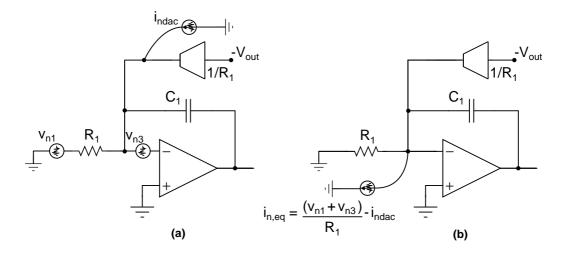

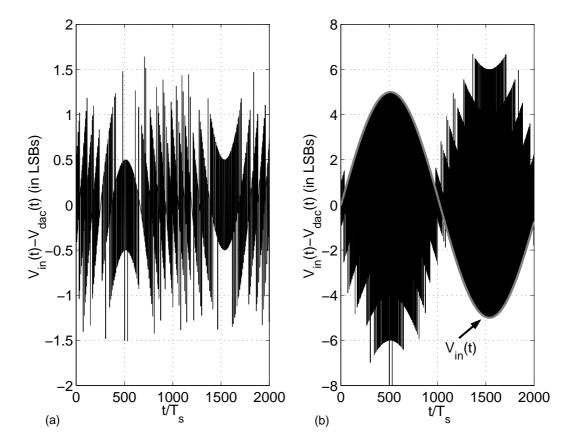

| E.5         | N-bit feedback DAC - resistive and current-steering implementation                                                                                                                                                   | 198 |

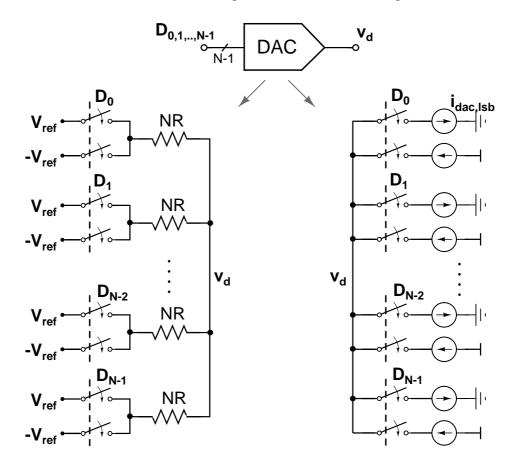

| F.1         | Normalized input to the loop filter $(V_{in}(t) - V_{dac}(t))$ observed for a 4-<br>bit modulator with (a) NRZ DAC (b) RZ DAC. The input signal is also<br>shown for reference in grey                               | 200 |

| G.1         | Circuit of the first integrator of a CTDSM with feedforward compen-<br>sated opamp. The responses (currents) at each node given a step input<br>have been shown neglecting the initial transients.                   | 203 |

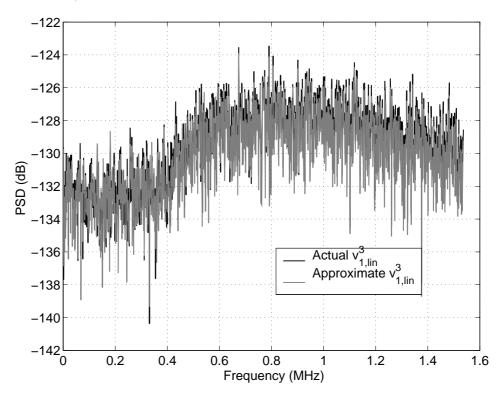

| G.2 | PSDs of the exact and approximate response, $v_{1,lin}^3$ in the feedforward<br>opamp based active-RC integrator. $g_{m1} = 27.12 \ \mu$ S, $R = 100 \ k\Omega$ , $C =$<br>527 fF, $c_1 = 45$ fF, $c_p = 10$ fF, $g_{m2} = 100 \ \mu$ S, $c_2 = 250$ fF, $r_1 = 20 \ M\Omega$ , $r_2 =$<br>$1 \ M\Omega$ . | 205 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

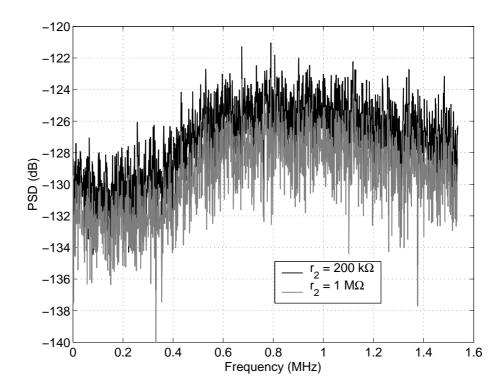

| G.3 | PSDs of the response, $v_{1,lin}^3$ observed for two values of $r_2$ of the feed-forward opamp based active-RC integrator                                                                                                                                                                                  | 206 |

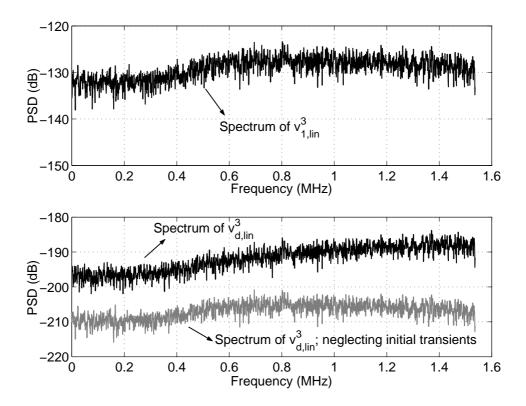

| G.4 | Comparison of the PSDs of $v_{1,lin}^3$ and $v_{d,lin}^3$ obtained with the feedforward opamp based active-RC integrator. The difference in the spectrum of $v_{d,lin}^3$ observed when the intial transients are neglected is also shown.                                                                 | 207 |

| I.1 | Pinout details of the audio CTDSM employing NRZ and SCR feedback DACs                                                                                                                                                                                                                                      | 211 |

## **ABBREVIATIONS**

- ADC Analog-to-Digital Converter

- DAC Digital-to-Analog Converter

- **DSP** Digital Signal Processor

- CTDSM Continuous-Time Delta Sigma Modulator

- PSD Power Spectral Density

- **SNR** Signal-to-Noise Ratio

- SAR Successive Approximation Register

- **STF** Signal Transfer Function

- **NTF** Noise Transfer Function

- **CIFF** Cascade of Integrators Feedforward

- **CIFB** Cascade of Integrators Feedback

- MSA Maximum Stable Amplitude

- **OBG** Out-of-Band Gain

- NRZ Non-Return-to-Zero

- RZ Return-to-Zero

- **SCR** Switched Capacitor Resistor

- **DEM** Dynamic Element Matching

- SR Slew-Rate

- IBN In-band Noise

- **ZOH** Zero-Order-Hold

- LSB Least Significant Bit

- **SNDR** Signal-to-Noise-plus-Distortion Ratio

- **DR** Dynamic Range

- **FOM** Figure of Merit

# NOTATIONS

## English symbols

| $f_s$      | Sampling frequency                                          |

|------------|-------------------------------------------------------------|

| $T_s$      | Sampling period                                             |

| $f_b$      | Signal bandwidth                                            |

| $g_m$      | Small-signal transconductance                               |

| $g_3$      | Third order coefficient of nonlinearity of a transconductor |

| $r_1, r_2$ | Small-signal resistances of an opamp                        |

| $c_1, c_2$ | Small-signal parasitic capacitances of an opamp             |

| $V_{ref}$  | Reference voltage of a DAC                                  |

| $A_{in}$   | Input signal amplitude                                      |

| $f_{in}$   | Input signal frequency                                      |

| $HD_3$     | Third Harmonic Distortion                                   |

## Greek symbols

| $\Delta$ | Step size of a quantizer                                        |

|----------|-----------------------------------------------------------------|

| $\beta$  | Third order coefficient of nonlinearity in a nonlinear function |

| $\sigma$ | Standard deviation of a random variable from its mean           |

| au       | Time constant of an RC network                                  |

## ACKNOWLEDGEMENTS

At the outset, I would like to express my sincere gratitude to my research advisor Dr. Shanthi Pavan. It was his constant motivations and encouragements that have been instrumental in shaping my research work. I would say I am privileged to not only benefit from his brilliant teaching but also get his invaluable guidance throughout my research life here at IIT, Madras. I would also like to thank him for spending lot of his precious time in helping me bring this thesis in its present form.

I also take this opportunity to thank Prof. Nagendra Krishnapura for imparting significant knowledge in the field of data converters and analog IC design. I am also grateful to him for having many timely technical discussions and for patiently clarifying many of my doubts. I would also like to extend my heartfelt gratitude to Prof. P.V. Ramakrishna (Anna University) at this juncture. His directions and inspirations during my under-graduate years have been significant in beginning my research career.

I am thankful to the members of my Doctoral Committee - Prof. Vinita Vasudevan and Prof. Nagendra Krishnapura of the Electrical Department, Prof. Babu Viswanathan of the Mechanical Department and Dr. Shankar Balachandran from the Computer Science Department, for their comments and suggestions.

I would like to acknowledge Anand Kannan, Sunil Rafeeque and Nitesh Kekre of Texas Instruments for granting access to some high-end test equipments and helping me test my fabricated chips.

I am greatly thankful to all my labmates who have been around me in different stages of my five year stay at IIT, Madras. Some of those lively discussions (technical and nontechnical) I had with my senior labmates - Reddy Karthikeyan, Murali, I.Rajesh, Laxmi Nidhi and V.V Srinivas, still remain fresh in my mind. I'm sure they will remain so forever. Equally good were the times spent with my juniors - Deepa, Shankar, Vikas, Hariharan, Amrith, Pradeep, Mrunmay, Lokesh, Eeshan, Saurabh, Sandeep, Radha, Sreelakshmi, Ankesh... (the list goes on). Some of my most enjoyable moments were with this lot, especially Deepa, Vikas and Amrith.

I would also like to thank all the support staff in our department and in the academic section for all the help they extended in administrative matters.

I also take this opportunity to thank my sisters and other family members for their timely moral support. Last but not the least, i would like to mention about my beloved parents, Thirugnanam and Thenmozhi, without whom I wouldn't have been what I am today. It would only be befitting to dedicate this thesis to them for all their care and support they have poured on me, right from day one I stepped on this planet.

(Prabu Sankar T.)

## ABSTRACT

KEYWORDS: Continuous-time; analog-to-digital; oversampling; delta-sigma; opamp nonlinearity; harmonic distortion; assisted opamp; audio

This research addresses the need to understand the effects of opamp nonlinearity on the performance of a class of oversampled analog-to-digital converters called continuoustime delta-sigma modulators. Nonlinearity in the opamps used to build continuous-time filters are one of the crucial factors determining the power consumption of these modulator. In modulators employing multi-bit quantizers, opamp nonlinearity is found to degrade the modulator performance by increasing the in-band noise. Analytical relations quantifying the increase in the in-band noise spectral density are developed for various integrator architectures and different opamp topologies. The analysis is also extended to quantify the harmonic distortions observed in modulators with single-bit quantizers. Macromodel simulation results are used to prove the accuracy of the derived analytical results.

A power efficient technique that can mitigate the effects of opamp nonlinearity in continuous-time delta-sigma modulators is also proposed. Termed as the 'assisted opamp technique', it can be used to achieve low power, low distortion operation in single-bit modulators. The efficacy of the technique is demonstrated through two singlebit audio modulators - one using a Non-Return-to-Zero (NRZ) feedback DAC and the other using a Switched Capacitor Resistor (SCR) feedback DAC. With the help of the proposed technique, the modulator with an NRZ DAC is found to achieve a dynamic range of 92.5 dB in a 24 kHz bandwidth, with a power dissipation of  $110 \mu$ W from a 1.8 V supply. The second design employing an SCR DAC, achieves a dynamic range of 91.5 dB and dissipates  $122 \mu$ W of power. The performance thus achieved with these modulators is comparable to that of the best multi-bit modulators reported in the literature.

## **CHAPTER 1**

## **INTRODUCTION**

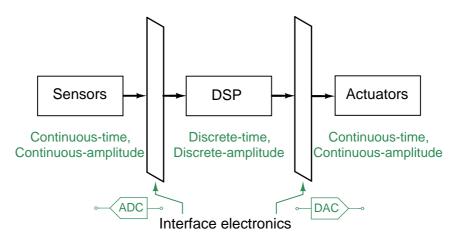

Advancements in the field of integrated circuits over the last few decades has made electronics an indispensable part of human life. With extensive computational capabilities, robustness, repeatability and long-term stability, digital signal processing techniques are becoming increasingly preferred over traditional analog processing. However, the world surrounding us is analog in nature and therefore, there is a need to interface the real world with digital processors. As depicted in Fig. 1.1, Analog-to-Digital Converters (ADCs) and Digital-to-Analog Converters (DACs) form a vital part of the interface electronics that bridge the analog and digital world.

Figure 1.1: Functional view of the role played by ADC and DAC

As the name suggests, the function of ADCs is to convert the continuous-time analog signals to digital signals that can be suitably processed by a Digital Signal Processor (DSP). DACs perform the inverse operation of converting the processed output from the

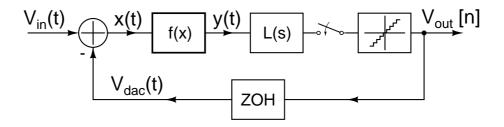

DSP back to the continuous-time domain. The focus of this thesis is a popular 'oversampled' ADC architecture called the *Continuous-Time Delta Sigma Modulator (CTDSM)*. This chapter is aimed at providing some of the basic concepts that can aid better understanding of the ideas and models presented in this thesis and has been organized as follows. Beginning with the fundamentals of analog-to digital conversion, the discussion is carried over to popular ADC architectures that are currently being used. Subsequently, the reader is introduced to delta sigma modulators, of which continuous-time modulators form a sub-class. Operational details and various implementation issues involving these modulators are then described, eventually bringing about the motivation behind the problem addressed in this thesis. The chapter is concluded by describing the organization of the thesis and contributions of this research work.

#### 1.1 Fundamentals of ADC - Sampling and Quantization

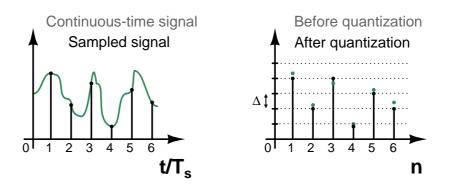

Figure 1.2: Illustration of sampling and quantization operations occurring in an ADC

The conversion from the analog to digital domain achieved in an ADC involves two fundamental operations - *sampling* and *quantization*. As illustrated in Fig. 1.2, sampling involves the conversion of the continuous-time analog signal to a discrete-time signal, sampled every  $T_s$  secs. The next process involves quantization of these samples to have discrete amplitude levels (in steps of  $\Delta$  as shown in Fig. 1.2). The discrete-levels are then appropriately mapped to the digital format to be able to be processed by a DSP.

In a nutshell, ADCs can be perceived as performing discretization in both time and amplitude domains. Such discretizations can be expected to lead to potential loss of information contained in the analog signal. Information loss during the sampling process is averted by adhering to Shannon's sampling theorem according to which '*any analog signal with a bandwidth of*  $f_b$  *can be completely reconstructed from its samples, if the sampling rate* ( $f_s$ ) *is more than*  $2f_b$ '. The critical sampling rate of ' $2f_b$ ' is termed as the Nyquist-rate.

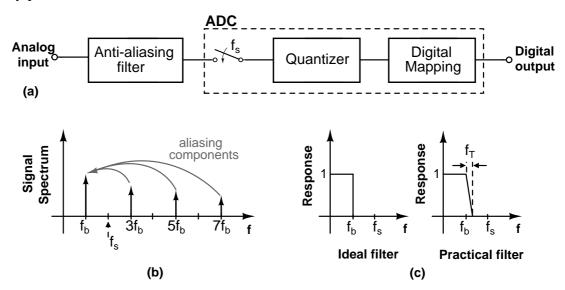

Figure 1.3: (a) Model of an ADC along with anti-aliasing filter (b) Illustration of aliasing into the signal band from components around multiples of  $\pm f_s$  (c) Response of ideal and practical anti-aliasing filters

Since not all signals are band-limited in nature, a low pass filter (called the 'antialiasing' filter) is always required to precede the sampling operation of an ADC, as shown in Fig. 1.3(a). Aliasing of frequency components around multiples of  $\pm f_s$  into the signal band (as illustrated in Fig. 1.3(b)), can be prevented by the anti-aliasing filter. Though an ideal brick-wall response is desired out of an anti-aliasing filter, practical realizability issues force the use of filters with finite transition bands ( $f_T$ ) as shown in Fig. 1.3(c). The order and the transition band requirements on the filter are determined by the nature (or the frequency content) of the continuous-time signal and the sampling rate used. Naturally, such specifications are the most severe when signals are sampled at the Nyquist-rate.

While discretization in the time-domain can be shown to be lossless, the same cannot be said about the subsequent operation of quantization. Discretization in the amplitude domain inherently introduces 'permanent' errors called the quantization error or quantization noise, thereby resulting in a lossy conversion. Such errors can be reduced by increasing the number of discrete-levels a quantizer can resolve into, or in other words, by reducing the step size ( $\Delta$ ) that separates each of these discrete-levels.

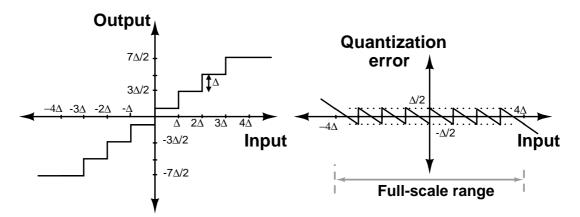

Figure 1.4: Typical input-output characteristic of a 8-level quantizer along with the quantization error profile

Illustrating these two design parameters of a quantizer is Fig. 1.4, where the inputoutput characteristic of a 8-level quantizer and the corresponding quantization error are shown. The quantization error can be seen to be bounded between  $-\Delta/2$  and  $\Delta/2$  for inputs in the range [-4 $\Delta$ , 4 $\Delta$ ]. This input range, beyond which the quantization error can be seen to grow without bounds is called the full-scale range of the quantizer. The quantizer is said to be saturated or over-loaded for inputs above this range.

Figure 1.5: (a) Linear representation of a quantizer (b) Probability density function, P(e) and Power Spectral Density,  $S_e(f)$  of the quantization noise

Though quantization is a nonlinear operation, dynamic performance of quantizers (and ADCs) has been traditionally analyzed by adopting a linearized, stochastic model as shown in Fig. 1.5(a). The quantizer is perceived as an independent additive source that introduces the quantization noise sequence, e[n]. As shown in Fig. 1.5(b), e[n] is assumed to be uniformly distributed (Bennett (1948)) in the range [- $\Delta/2$ ,  $\Delta/2$ ], with a white Power Spectral Density (PSD), under the following conditions<sup>1</sup>

- The quantizer input is within the full scale range

- The number of quantizer levels is large and the step size,  $\Delta$  is very small

- The input is random in nature

Under such assumptions, the quantization noise can be shown to have a variance of  $\Delta^2/12$  and a PSD given by  $\Delta^2/(12f_s)$ . Though the white noise approximation becomes invalid for sinusoidal inputs (since the quantization noise becomes periodic), the quantization noise power is found to be close enough to  $\Delta^2/12$ . Therefore, the dynamic performance of an ADC is measured by the Signal-to-Noise Ratio (SNR) observed for a sinusoidal input, assuming a variance of  $\Delta^2/12$  for the quantization noise. For a

<sup>&</sup>lt;sup>1</sup>While these conditions serve to provide a general outlook on the cases when the above assumption is valid, more specific conditions on the characteristics of the input signal can be found in Widrow (1956) and Sripad and Snyder (1977).

full-scale input signal, the resulting peak SNR can be shown to be

$$SNR = (6.02N + 1.76) \,\mathrm{dB}$$

(1.1)

where N denotes the number of bits used to represent the discrete levels of the quantizer<sup>2</sup>. The above equation is often used in the reverse sense to define the resolution of an ADC, as the value of N determined by the peak SNR achieved with the ADC. The resolution increases by one bit for every 6 dB increase in the peak SNR.

#### **1.2 ADC architectures**

Various ADC architectures have been proposed to accomplish the conversion from analog to digital domain based on the principles discussed above. Based on the sampling rate, they can be broadly classified into Nyquist-rate and oversampled converters.

A. Nyquist-rate Converters : Nyquist-rate converters sample the input signal at twice the signal bandwidth  $(2f_b)$ . Some of the popular architectures are (Johns and Martin (2009))

- Flash ADCs

- Successive Approximation Register (SAR) ADCs

- Pipeline ADCs

The building block behind all these architectures is the *comparator*, which decides whether the input signal is above or below a threshold and accordingly generates a binary '1' or '0' as the output. Each architecture employs the comparator in an unique manner to facilitate the required analog to digital conversion.

$<sup>^2 \</sup>text{In effect, an ADC with } 2^{\rm N}$  discrete levels of quantization has N bits in its digital output.

For instance, a N-bit flash ADC employs  $2^{N}$ -1 comparators that act in a concurrent fashion, to achieve the conversion. Fig. 1.6(a) shows a typical 2-bit flash ADC built with 3 comparators, with each of the thresholds tapped from the resistive ladder shown. The comparators together provide a thermometer coded output<sup>3</sup> which is then decoded to obtain a 2-bit binary output.

Figure 1.6: (a) 4-bit Flash ADC (b) Functional block diagram of a SAR ADC

Due to the exponential increase in the number of comparators with increasing resolution (N), flash ADCs are not used to achieve resolutions higher than 8 bits. For some applications requiring higher resolutions, SAR ADCs can be used. As shown in Fig. 1.6(b), SAR ADCs employ a single comparator in an iterative fashion. They use the *binary search* algorithm to systematically reduce the difference between the input signal (u(t)) and its estimate given by the fed back DAC signal (v(t)). Such a digitization process requires N clock-cycles to generate a N-bit digital output. This clearly shows that speed is traded off to have reduced complexity (area), when adopting SAR ADCs over flash

<sup>&</sup>lt;sup>3</sup>Similar to the dipping of mercury level of a thermometer, the comparators whose thresholds are lower than the input signal, generate a logic high (or '1') at their outputs.

ADCs. For applications that require higher data rates than supported by SAR ADCs,

Figure 1.7: (a) Individual stage of a pipeline ADC (b) Functional block diagram of a pipeline ADC having M stages

Pipeline ADCs can be used. As the name suggests, this architecture utilizes the principle of pipelining to engage M stages of conversion, in a concurrent fashion. As depicted in Fig. 1.7(a), each stage employs an ADC (typically a flash) and a DAC to generate a N-bit digitized output along with the quantization error, e[n]. As shown in Fig. 1.7(b), the quantization error generated by each stage ( $e_i[n]$ ) is then passed on to the subsequent stage, for digitization in the 'next' clock cycle. The digitization of a given input sample is completed after M clock cycles (stages), when a digital block appropriately combines the output of each stage to generate the desired digital output. Except for the initial latency period<sup>4</sup> of typically M clock cycles, very high conversion rates can be achieved with this architecture, thanks to the parallel conversion operations occurring in each of the M stages. It can be seen that circuit complexity has been traded off to achieve higher speeds with a pipeline architecture.

<sup>&</sup>lt;sup>4</sup>This refers to the number of clock cycles needed before the first digital output can be obtained corresponding to the first input sample.

*B. Oversampled converters :* While Nyquist-rate converters can be said to be strictly following the sampling theorem, analog signals can be digitized at a much higher sampling rate as is done in *oversampled converters*. Oversampling results in several benefits such as

- The requirements on the anti-aliasing filter are relaxed due to oversampling, as they can have less-steeper roll-off characteristics with  $f_s/2 \gg f_b$ .

- More importantly, the quantization noise (with variance  $\Delta^2/12$ ) is now spread across a wider bandwidth. This effectively reduces the quantization noise power in the desired signal bandwidth<sup>5</sup> ( $f_b$ ), as shown in Fig. 1.8(a).

Figure 1.8: (a) Comparison of quantization noise PSD (single-sided) with Nyquist-rate sampling and oversampling (b) Noise shaping achieved in delta-sigma modulators

In essence, oversampling is an useful technique that can increase the effective resolution of an ADC. The output of an oversampled converter can be filtered to remove the noise outside the signal band of interest and then re-sampled at the Nyquist rate to achieve the desired improvement in resolution. Defining a factor called Over-Sampling Ratio (OSR =  $f_s/(2f_b)$ ), increasing the OSR by a factor of 2 can be seen to result in a 3 dB reduction in the in-band quantization noise power. However, observe that for

<sup>&</sup>lt;sup>5</sup>The desired signal band will henceforth be referred to as the in-band region

every half a bit of improvement in the effective resolution, the sampling rate has to be increased in an exponential manner. Thus, it should be mentioned that additional techniques have to be employed along with oversampling, to obtain significant improvements in the resolution of a converter. Delta-Sigma modulators are one such sub-class of oversampled converters that can achieve very high resolutions, by employing the technique of 'noise shaping' (as depicted in Fig. 1.8(b)). While pipeline architectures can be said to increase the speed of conversions, delta-sigma modulators are seen as suitable choices to achieve high resolutions, that are hard to achieve with a SAR ADC. The following sections have been organized to provide a more detailed overview about this architecture.

#### 1.3 Basics of Delta-Sigma modulation

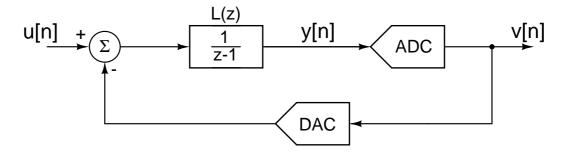

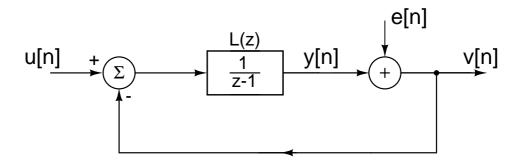

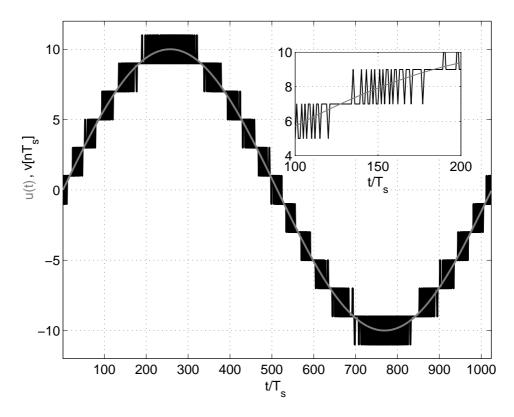

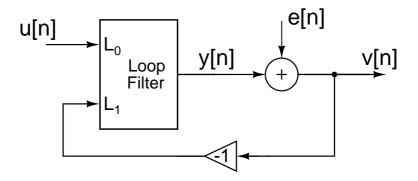

Figure 1.9: Functional block diagram of a first order Delta-Sigma modulator