# Design of a Decimator and a Delta Sigma Modulator for Audio Bandwidth

A THESIS

submitted by

### **P. SHANKAR**

for the award of the degree

of

#### **MASTER OF SCIENCE**

(by Research)

Department Of Electrical Engineering Indian Institute of Technology Madras, India

November 2011

### CERTIFICATE

This is to certify that the thesis titled **Design of a Decimator and a Delta Sigma Modulator for Audio Bandwidth**, submitted by **P. Shankar**, to the Indian Institute of Technology Madras, for the award of the degree of **Master of Science**, is a bona fide record of the work done by him under my supervision. The contents of this thesis, in full or in parts, have not been submitted to any other Institute or University for the award of any degree or diploma.

Dr. Nagendra Krishnapura

Research Advisor Associate Professor Dept. of Electrical Engineering IIT Madras Chennai 600 036

Place: Chennai

Date:

### ACKNOWLEDGEMENTS

காலத்தி னாற்செய்த நன்றி சிறிதெனினும் ஞாலத்தின் மாணப் பெரிது.

திருக்குறள் : 102, அதிகாரம் : செய்ந்நன்றி அறிதல்

A timely help and support given by someone is of earthly value regardless of how small the help is. I take this as an opportunity to thank and acknowledge the people around me who helped me in numerous occasions throughout my life.

At first, I express my sincere gratitude to my guide Dr. Nagendra Krishnapura for giving this opportunity to work under him. I learned a broader perspective of Analog IC design through his courses and the interactions I had with him. Much broader was the perspective of the research career through the projects that I have done under him. I extend my gratitude and thank him for the support, guidance and freedom he has provided that gives an environment of continuous and better learning for a research career.

I thank my GTC members, Dr. Nitin Chandrachoodan and Dr. V. Kamakoti for evaluating my work and providing valuable suggestions at right times. I thank Prof. Shanthi Pavan for his wonderful course on data converters which forms the core of my thesis. He makes understand very complex ideas in a simple and elegant fashion which reminds me of my school time physics teacher. I thank Dr. C.S. Ramalingam for the useful discussions on digital filter design. I would also like to thank Prof. S. Karmalkar for his course on MOS modelling through which I got a deep insight of dancing of electrons inside a transistor. I would like to extend my sincere thanks to Dr. Vinita Vasudevan for funding me during my final semester.

I thank the office and administrative staff of our department especially Mrs. Sumathi, Mrs. Janaki and Mr. Sarnath for the timely help in solving problems in lab and sorting out the administrative issues.

My passion towards the research career was mainly imbibed during my under graduation by Prof. P. V. Ramakrishna, College of Engineering Guindy. I sincerely thank him for his motivation, courses and project opportunities he had provided us that gave us more confidence to build our career.

My heartfelt gratitude goes to Abishek Goda and Ramakrishnan who helped me in understanding the digital design flow and troubleshooting CAD tools. Digital part of my work would have been difficult for me to complete if not for their help. Abishek has been a good friend and a great companion in IITM, playing tennis, python programming, linux KT and many others. I thank Kunal for assisting me in testing the final version of my decimator chip. I acknowledge Siladitya and Hariharan who supported me during the tape-out of my Delta Sigma modulator. Many thanks to Siladitya for helping me layout a couple of blocks and Hariharan who reviewed and gave valuable suggestions that my tape-out happened in time.

My long stay in IITM would not have been smooth, peaceful and joyful if not for my seniors Deepa and Vallabh. They treated me as their brother providing moral support, keeping me energetic and buoyant whenever I hit a low. Special thanks to Mrs. Vallabh for the delicious food at home many times.

During my considerably long duration of stay in IITM, I happened to interact with lots of people. Initial fun days were with Prashanth Jnanendra, Nanda Govind, TJ Karthik. I had great time of fun and learning with my seniors, batch mates and a few generations of my juniors - Prabu Sankar, Vikas, Hariharan, Mrinmay, Radha, Amrith, Pradeep, Kunal, Lokesh, Jishnu, Siladitya, ABK, Ankesh, Naga Rajesh and nevertheless its an non exhaustive list that goes long. It was good interacting technically with Pradeep, Mrinmay and Chembian. The discourses on art, science, literature, mathematics with Chembian and Mrinmay are still nice to remember. Some of my most cherish able and memorable moments I had here are with Deepa, Vallabh, Abishek and Radha. I thank all of them for their kindness they have showered on me.

Life would have been monotonous and boring in IITM if not for the discourses with Ashwin on variety of topics cinema, politics, medicine, philosophy, (a)theism and lots of technical stuff. I thank him for the great companionship. Similar thanks goes AR Karthikeyan and Sandeep Palakkal with who I share my hobby of photography. I thank my hostel friends for the fun time I had with them, especially Sathesh (tennis partner), Magesh and Sivakumar. I thank my undergrad friends with whom I had loads of fun during many weekends which helped me relax and rejuvenate. Few of them are Selvakumar, Arulmani, Vijay Babu, Sanjeev, Rangarajan, Raajay, Ramprasad, Muthuselvan.

I take this as an opportunity to thank my mother and my relatives who provided me all the moral support. I am very gifted to have such an understanding mother and grand parents whose love, care and support helped me reach this heights. It is a great honour for me to dedicate this thesis to them.

P. Shankar

உள்ளுவ தெல்லாம் உயர்வுள்ளல் மற்றது தள்ளினும் தள்ளாமை நீர்த்து. திருக்குறள் : 66, அதிகாரம் : ஊக்கமுடைமை

Let the aim, thoughts and actions be strong and lofty. The virtue of them stands irrespective of their failures.

#### ABSTRACT

This work explores the design of a decimator and a Delta Sigma ( $\Delta\Sigma$ ) modulator for audio bandwidths. These are the essential components of the front end of a digital audio system. The first part of the work explores the design of a low power decimator and the second part of the work involves with the design of a very high resolution  $\Delta\Sigma$ modulator.

A decimator for a low power (90  $\mu$ W)  $\Delta\Sigma$  modulator [1] with 24 kHz bandwidth and an in-band resolution of 16 bits is designed in a 1.8 V, 0.18  $\mu$ m CMOS process. To achieve a low power consumption comparable to that of the modulator, various optimizations like retiming of registers, canonical signed digits (CSD) encoding for tap weights of the filters, polyphase implementation of the filters and optimal selection of data path width are employed. The decimator occupies an area of 0.46 mm<sup>2</sup> and consumes a power of 100  $\mu$ W from a supply of 1.8 V and is operational down to a reduced supply of 0.9 V.

A high resolution continuous-time  $\Delta\Sigma$  modulator targeting a resolution of 18 bits (108 dB SNR) in audio bandwidth (20 Hz-24 kHz) is designed in a 1.8 V, 0.18  $\mu$ m CMOS process. The resolution of the internal quantizer is 4 bit and the modulator runs at the oversampled frequency of 3.072 MHz. The modulator is designed for an SNR of 108 dB and the simulated SQNR is in excess of 115 dB. The modulator occupies an area of 0.89 mm<sup>2</sup> and consumes a current of 540  $\mu$ A from a supply of 1.8 V. The measured idle channel in-band integrated noise is 6.5  $\mu$ V<sub>rms</sub> and the modulator is stable up to -0.7 dBFS.

## TABLE OF CONTENTS

| AC | CKNC  | OWLEDGEMENTS                                  | i   |

|----|-------|-----------------------------------------------|-----|

| Ał | BSTR  | ACT                                           | iii |

|    | LIST  | Γ OF TABLES                                   | ix  |

|    | LIST  | Γ OF FIGURES                                  | xi  |

| AI | BBRE  | VIATIONS                                      | xvi |

| 1  | Intro | oduction                                      | 1   |

|    | 1.1   | Organization of the thesis                    | 2   |

| 2  | Intro | oduction to decimators                        | 4   |

|    | 2.1   | $\Delta\Sigma$ modulation                     | 4   |

|    | 2.2   | Overview of decimation                        | 6   |

|    |       | 2.2.1 Downsampling                            | 6   |

|    |       | 2.2.2 Decimation in $\Delta\Sigma$ modulation | 8   |

|    | 2.3   | Design targets for the decimator              | 8   |

| 3  | Arcl  | nitecture of the decimator                    | 9   |

|    | 3.1   | Multistage decimation                         | 9   |

|   | 3.2             | SINC4 filter                                 | 10 |

|---|-----------------|----------------------------------------------|----|

|   |                 | 3.2.1 Hogenauer structure                    | 12 |

|   |                 | 3.2.2 Pipelining and retiming of SINC4       | 12 |

|   | 3.3             | Halfband filters                             | 14 |

|   |                 | 3.3.1 Implementation of the halfband filters | 15 |

|   | 3.4             | Equalizer                                    | 20 |

|   | 3.5             | Scaling block                                | 21 |

| 4 | Synt            | thesis of the decimator                      | 23 |

|   | 4.1             | Description of design flow                   | 23 |

|   |                 | 4.1.1 Synthesis & simulation results         | 25 |

|   |                 | 4.1.2 Power estimation                       | 25 |

|   | 4.2             | Level translator                             | 26 |

| 5 | Mea             | sured results from the decimator chip        | 28 |

|   | 5.1             | Test setup                                   | 28 |

|   | 5.2             | Results from the fabricated chip             | 29 |

|   |                 | 5.2.1 Power measurement                      | 30 |

|   | 5.3             | Summary                                      | 31 |

| 6 | $\Delta \Sigma$ | modulator fundamentals                       | 32 |

|   | 6.1             | Continuous-time $\Delta\Sigma$ modulation    | 33 |

|   |                 | 6.1.1 Advantages of a CTDSM                  | 35 |

|   |     | 6.1.2 Performance measures                   | 35 |

|---|-----|----------------------------------------------|----|

|   | 6.2 | Design targets for the CTDSM                 | 37 |

|   | 6.3 | Nonidealities in a CTDSM                     | 37 |

|   |     | 6.3.1 Clock jitter                           | 38 |

|   |     | 6.3.2 Excess loop delay                      | 39 |

|   |     | 6.3.3 Loop filter                            | 40 |

|   |     | 6.3.4 ADC                                    | 43 |

|   |     | 6.3.5 DAC                                    | 44 |

|   | 6.4 | Block level design                           | 45 |

|   |     | 6.4.1 Choice of the NTF                      | 46 |

|   |     | 6.4.2 Designing for noise                    | 47 |

| 7 | Con | tinuous-time loop filter                     | 52 |

|   | 7.1 | Loop filter topology                         | 52 |

|   | 7.2 | Integrator topology                          | 53 |

|   | 7.3 | Realization of the loop filter               | 53 |

|   | 7.4 | First integrating op-amp                     | 54 |

|   | 7.5 | The second and the third integrating op-amps | 57 |

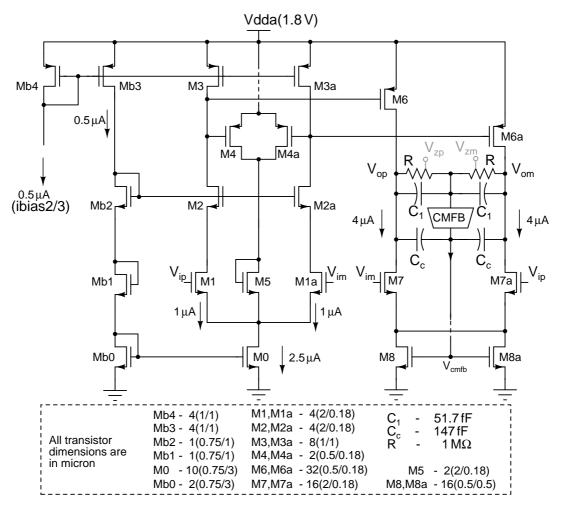

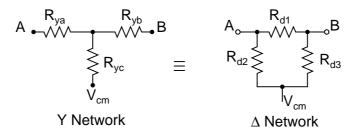

|   |     | 7.5.1 Implementation of the complex poles    | 58 |

|   | 7.6 | Summing amplifier                            | 59 |

|   | 7.7 | Tuning of R & C variations                   | 61 |

|   | 7.8 | Summary                                      | 65 |

#### 8 Four bit flash ADC

|    | 8.1  | Architecture of the flash array         | б |

|----|------|-----------------------------------------|---|

|    |      | 8.1.1 Resistive ladder                  | 6 |

|    |      | 8.1.2 Comparator                        | 7 |

|    |      | 8.1.3 Latch                             | 9 |

|    | 8.2  | Element mismatches in the ADC           | 0 |

|    |      | 8.2.1 Mismatch in latch transistors     | 1 |

|    |      | 8.2.2 Mismatch between ladder resistors | 3 |

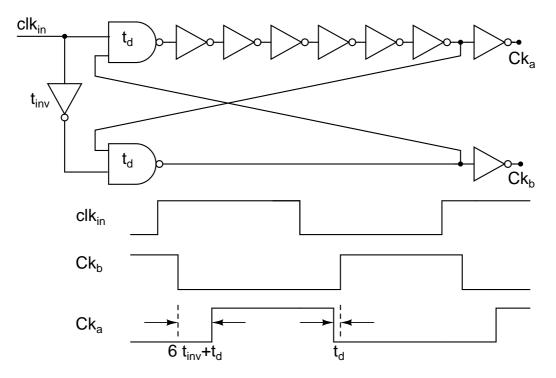

|    | 8.3  | Clock generation for the flash ADC      | 4 |

| 9  | Feed | pack DAC 70                             | 6 |

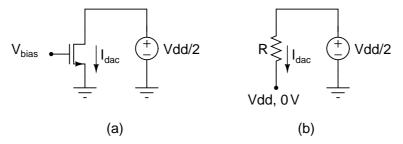

|    | 9.1  | The DAC unit element                    | 5 |

|    | 9.2  | Accuracy of DAC elements                | 8 |

|    | 9.3  | Dynamic element matching                | 9 |

|    |      | 9.3.1 Data weighted averaging           | 9 |

|    |      | 9.3.2 Implementation of the DWA         | 0 |

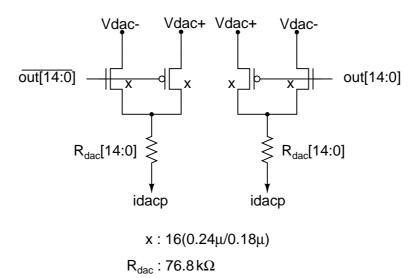

|    | 9.4  | DAC resistor sizing                     | 2 |

| 10 | Layo | it and top level simulation results 84  | 4 |

|    | 10.1 | Layout                                  | 4 |

|    | 10.2 | Simulation results                      | 4 |

|    | 10.3 | Power consumption                       | 6 |

66

| 11 | Measurement results from the $\Delta\Sigma$ modulator chip | 88 |

|----|------------------------------------------------------------|----|

|    | 11.1 Test setup                                            | 88 |

|    | 11.2 Measurement results                                   | 89 |

|    | 11.2.1 Idle channel performance                            | 89 |

|    | 11.2.2 Performance with sinusoidal input                   | 91 |

| 12 | Conclusions                                                | 93 |

| A  | Pin details of the decimator chip                          | 94 |

| B  | Table of coefficients of the filters in the decimator      | 95 |

| C  | Reference currents for the $\Delta\Sigma$ modulator        | 97 |

| D  | Pin details of the $\Delta\Sigma$ modulator chip           | 98 |

## LIST OF TABLES

| 2.1  | Modulator characteristics                                | 8  |

|------|----------------------------------------------------------|----|

| 2.2  | Decimator requirements                                   | 8  |

| 4.1  | CAD tools used for the decimator design                  | 23 |

| 4.2  | Power consumption for various test inputs                | 26 |

| 4.3  | Power consumption of the blocks of the decimator         | 26 |

| 5.1  | Power consumption for various supply voltages            | 31 |

| 5.2  | Performance summary of the decimator                     | 31 |

| 6.1  | Performance summary of the CTDSM [1]                     | 37 |

| 6.2  | CTDSM design specifications                              | 37 |

| 6.3  | Noise contributions from various elements                | 50 |

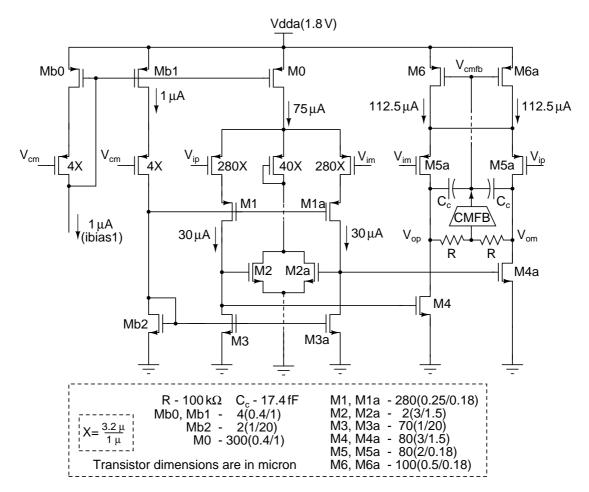

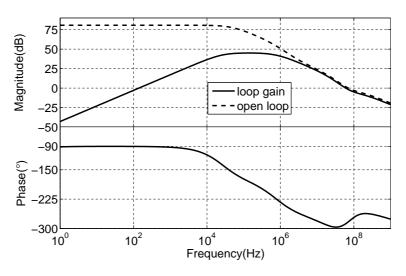

| 7.1  | Performance summary of the first op-amp/integrator       | 57 |

| 7.2  | Performance summary of the summing op-amp                | 60 |

| 7.3  | Modulator performance with time constant $(\tau)$ tuning | 64 |

| 7.4  | Current consumption of the loop filter                   | 65 |

| 10.1 | Simulation results: SNDR for various test cases          | 85 |

| 10.2 | Simulation results: SNDR for RC corners with tuning      | 85 |

| 10.3 | Power consumption of the $\Delta\Sigma$ modulator blocks            | 86 |

|------|---------------------------------------------------------------------|----|

| 10.4 | Summary of the $\Delta\Sigma$ modulator design                      | 87 |

| A.1  | Pin details of the decimator chip                                   | 94 |

| B.1  | Coefficients of the first halfband filter ( $10^{\rm th}$ order)    | 95 |

| B.2  | Coefficients of the second halfband filter (50 <sup>th</sup> order) | 95 |

| B.3  | Coefficients of the equalizer ( $34^{th}$ order)                    | 96 |

| D.1  | Pin details of the $\Delta\Sigma$ modulator chip                    | 99 |

## **LIST OF FIGURES**

| 2.1  | Block diagram of a discrete-time $\Delta \Sigma$ modulator.         | 4  |

|------|---------------------------------------------------------------------|----|

| 2.2  | CTDSM (a) Block diagram, (b) Discrete time equivalent with additive |    |

|      | quantization noise model.                                           | 4  |

| 2.3  | Spectrum of a $\Delta\Sigma$ modulator, Order: 3, OSR: 64           | 6  |

| 2.4  | Illustration of downsampling by a factor of three.                  | 6  |

| 2.5  | Spectrum of the downsampled signal when $M = 3. \dots \dots \dots$  | 7  |

| 2.6  | A decimator that downsamples by $M$                                 | 7  |

| 2.7  | Decimator for a $\Delta\Sigma$ modulator                            | 8  |

| 3.1  | Block diagram of the multistage decimator.                          | 10 |

| 3.2  | Zeros of a 16 tap SINC filter in the $\mathcal{Z}$ plane            | 11 |

| 3.3  | Frequency response of the SINC4 filter(aliasing bands in gray)      | 11 |

| 3.4  | Implementation of SINC4 as Hogenauer structure                      | 12 |

| 3.5  | Retiming and pipelining of accumulators for power reduction         | 13 |

| 3.6  | Implementation of the SINC4 filter.                                 | 13 |

| 3.7  | Frequency response: The first and the second halfband filters       | 15 |

| 3.8  | Polyphase structure in halfband filters                             | 17 |

| 3.9  | Deserializer: Splits data into even and odd streams                 | 17 |

| 3.10 | Filtering of quantization noise floor.                              | 18 |

| 3.11 | Polyphase implementation of the first halfband filter ( $10^{\rm th}$ order)    | 19 |

|------|---------------------------------------------------------------------------------|----|

| 3.12 | Obtaining output from the internal states.                                      | 20 |

| 3.13 | Frequency response of the Equalizer, the unequalized & the equalized decimator. | 21 |

|      |                                                                                 | 21 |

| 4.1  | Layout of the decimator chip                                                    | 24 |

| 4.2  | Simulated spectrum of the decimator output, SNR=95.8 dB                         | 25 |

| 4.3  | Schematic of the level translator.                                              | 27 |

| 5.1  | Block diagram of the test setup.                                                | 28 |

| 5.2  | Picture of the test PCB.                                                        | 29 |

| 5.3  | Measured spectrum of the decimator's output                                     | 29 |

| 5.4  | Comparison of the impulse responses.                                            | 30 |

| 6.1  | Block level representation of an ADC and its additive quantization noise        |    |

|      | model                                                                           | 32 |

| 6.2  | Quantization noise spectrum (a) Nyquist rate, (b) Oversampled rate              | 33 |

| 6.3  | Block diagram of a continuous-time $\Delta\Sigma$ modulator                     | 34 |

| 6.4  | Plot of input to the internal ADC when the modulator input is a slow            |    |

|      | ramp                                                                            | 36 |

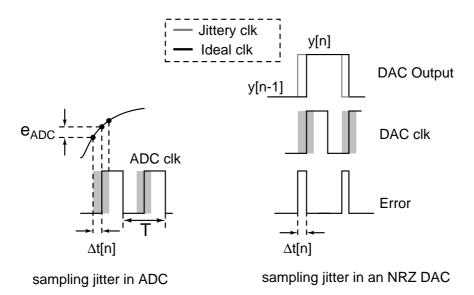

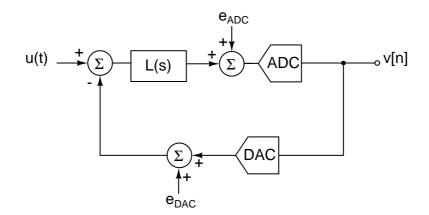

| 6.5  | Sampling error due to clock jitter in ADC and DAC                               | 38 |

| 6.6  | Modelling the effect of clock jitter in a CTDSM                                 | 38 |

| 6.7  | Continuous-time and discrete-time loop filter equivalence                       | 39 |

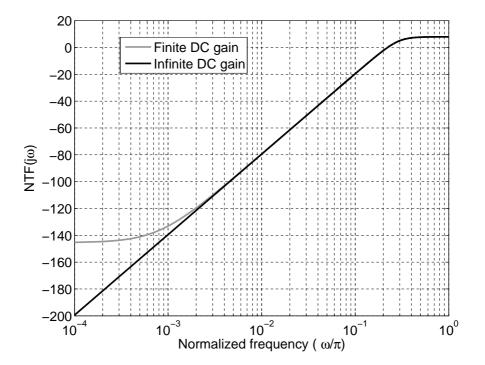

| 6.8  | NTF magnitude response for finite DC gain of the op-amps                        | 41 |

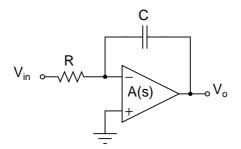

| 6.9  | Schematic of an active RC integrator.                                                                                                | 42 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

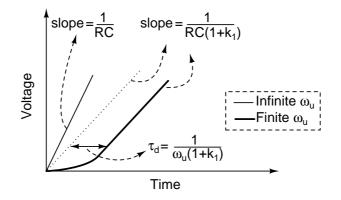

| 6.10 | Step response of an integrator having finite UGF                                                                                     | 42 |

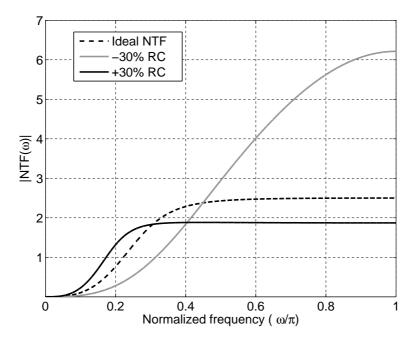

| 6.11 | Variation of the NTF for $\pm30\%$ change in RC time constants. $\ .\ .\ .$                                                          | 43 |

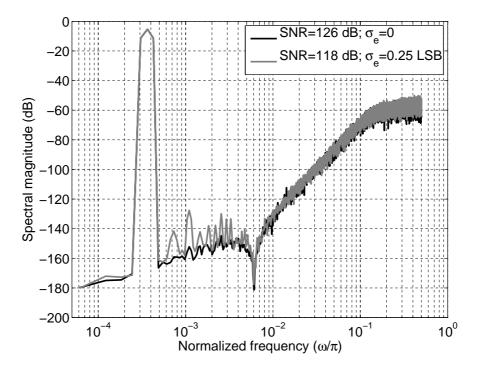

| 6.12 | Modulator's spectrum for 0.25 LSB error in the references                                                                            | 44 |

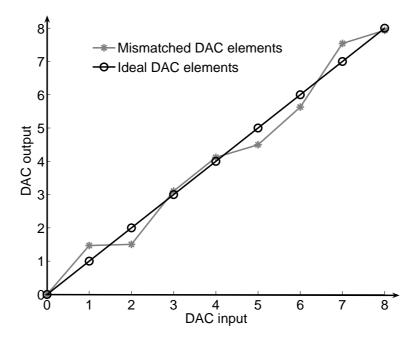

| 6.13 | Transfer characteristic of a DAC with mismatched elements                                                                            | 45 |

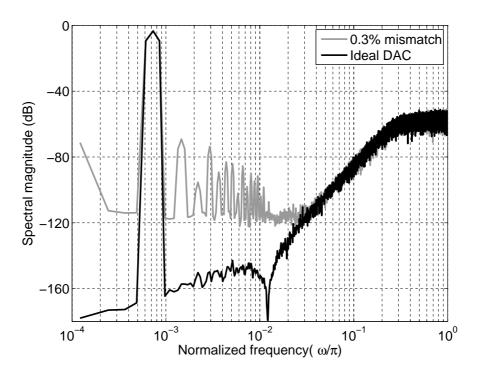

| 6.14 | Modulator's spectrum for 0.3% mismatched DAC elements                                                                                | 46 |

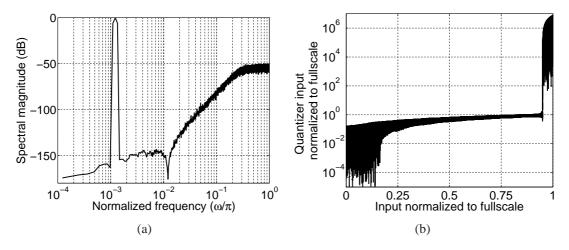

| 6.15 | Macromodel simulation results: (a) Spectrum of the modulator output,<br>(b) Plot of quantizer input as a function of input amplitude | 47 |

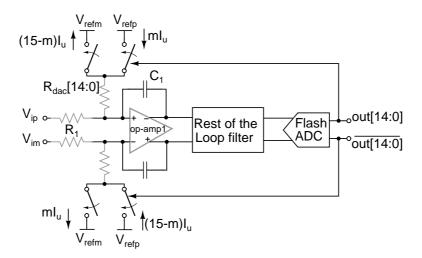

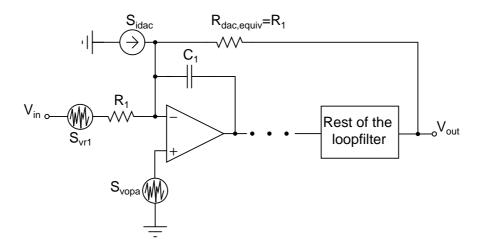

| 6.16 | Circuit diagram of the CTDSM showing the important noise contribut-                                                                  |    |

|      | ing elements (shaded gray).                                                                                                          | 48 |

| 6.17 | Equivalent circuit of the modulator for noise analysis                                                                               | 49 |

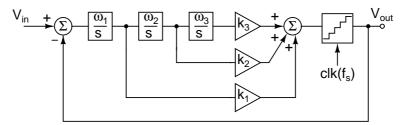

| 7.1  | Third order loop filter: CIFF structure                                                                                              | 52 |

| 7.2  | Third order loop filter: CIFB structure                                                                                              | 52 |

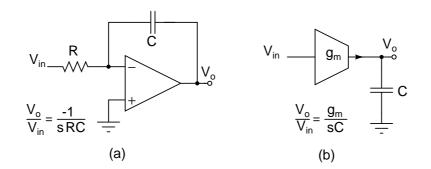

| 7.3  | Integrator types: (a) Active RC integrator, (b) $g_m$ -C integrator                                                                  | 53 |

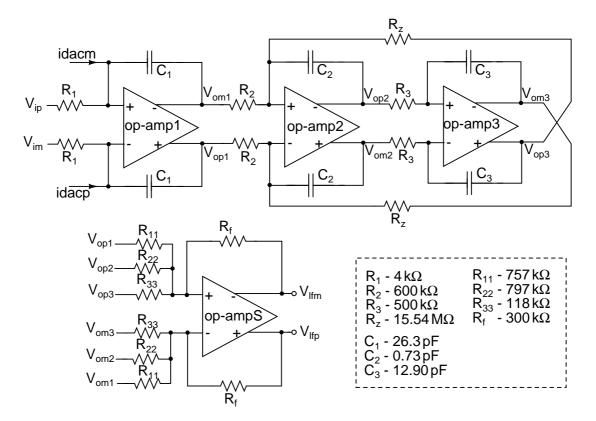

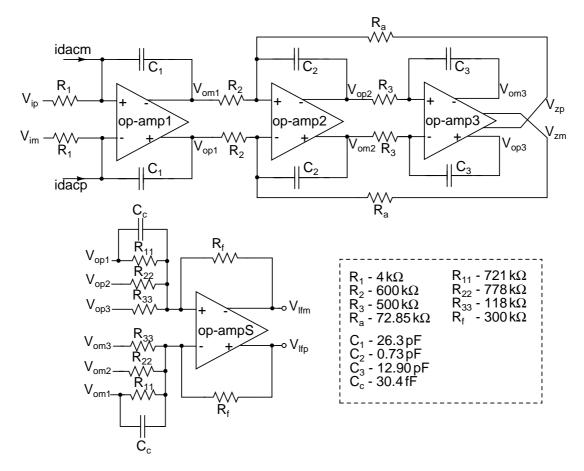

| 7.4  | Realization of the CIFF loop filter.                                                                                                 | 54 |

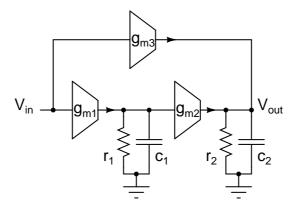

| 7.5  | Block diagram of a feedforward op-amp                                                                                                | 55 |

| 7.6  | Schematic of the first op-amp.                                                                                                       | 56 |

| 7.7  | Frequency response of the first op-amp.                                                                                              | 56 |

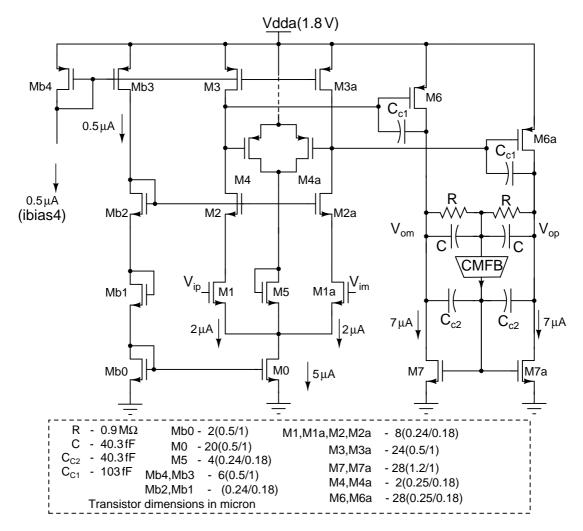

| 7.8  | Schematic of the second and the third integrating op-amps                                                                            | 57 |

| 7.9  | Illustration of $Y - \Delta$ transformation                                                                                          | 58 |

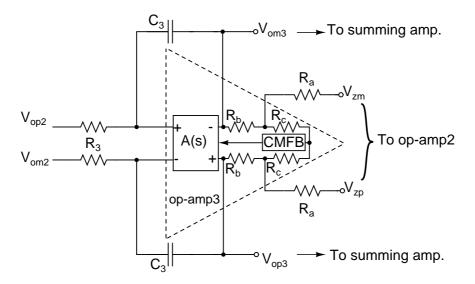

| 7.10 | Implementation of complex poles with the CMFB                                                                                        | 59 |

| 7.11 | Schematic of the summing op-amp.                                                                                                     | 60 |

| 7.12 | Loop filter with excess loop delay compensation.                           | 61 |

|------|----------------------------------------------------------------------------|----|

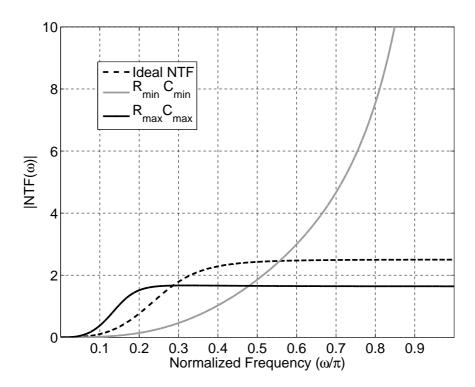

| 7.13 | NTF variation for $\pm35\%$ R variation and $\pm15\%$ C variation          | 62 |

| 7.14 | Integrating capacitor tuning bank.                                         | 62 |

| 7.15 | Histogram of $\frac{\tau_a}{\tau_i}$ for $R_{tio} = 0.293$                 | 64 |

| 7.16 | NTF variation for $\pm 10$ % variation in time constants                   | 65 |

| 8.1  | Block diagram of the 4 bit flash ADC                                       | 67 |

| 8.2  | Block diagram of the comparator.                                           | 68 |

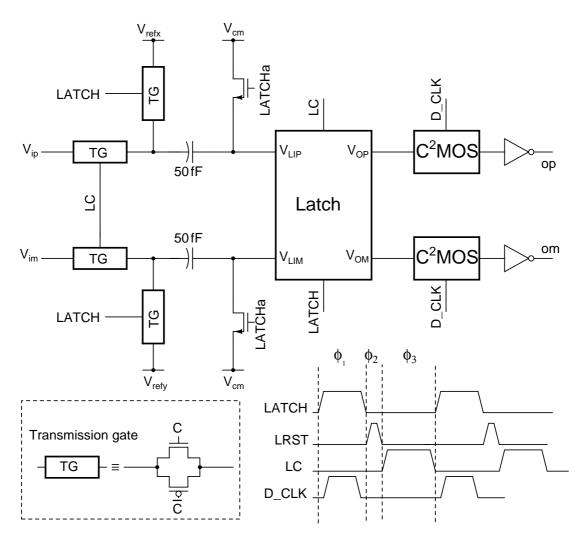

| 8.3  | Circuit diagram of the latch.                                              | 69 |

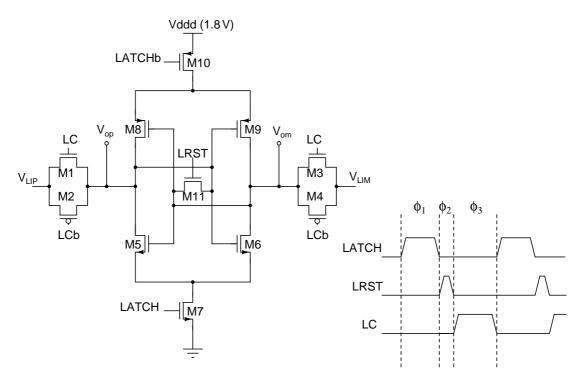

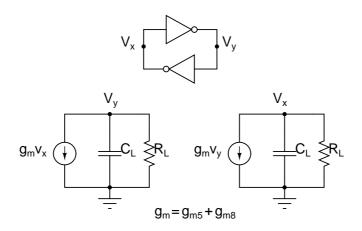

| 8.4  | Equivalent circuit of the latch.                                           | 70 |

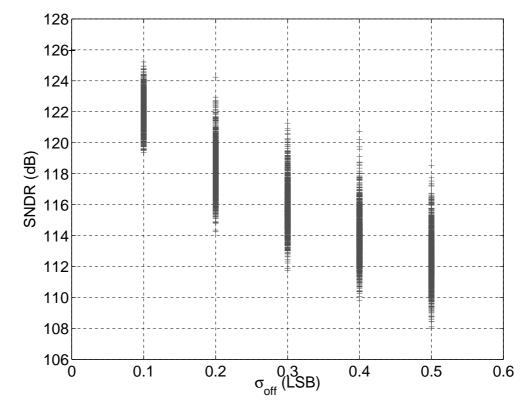

| 8.5  | Scatter plot of the SNR for 1000 simulations with different latch offsets. | 72 |

| 8.6  | Scatter plot of the SNR for 1000 simulations with mismatched ladder        |    |

|      | resistors                                                                  | 73 |

| 8.7  | Non-overlapping clock generator                                            | 74 |

| 9.1  | Implementation of a DAC unit element: a) A current source constructed      |    |

|      | with MOSFET, b) A current source using a resistor.                         | 77 |

| 9.2  | Schematic of the resistive DAC.                                            | 77 |

| 9.3  | Generation of the references for the DAC                                   | 78 |

| 9.4  | Illustration of the DWA                                                    | 80 |

| 9.5  | Block level implementation of the DWA                                      | 81 |

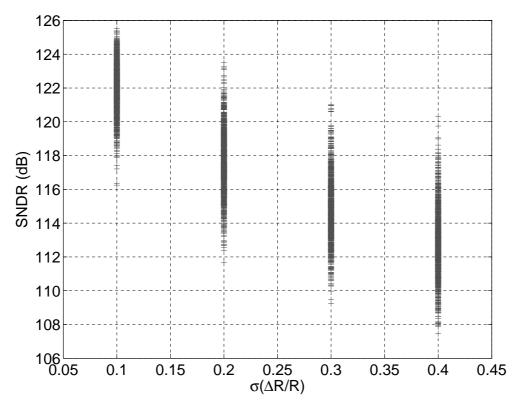

| 9.6  | Scatter plot of the SNR for various $\sigma_{\frac{\Delta R}{R}}$          | 82 |

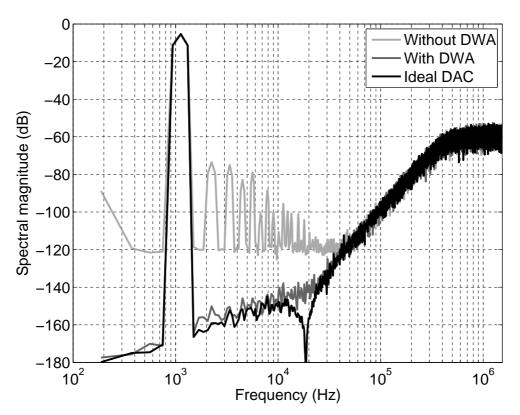

| 9.7  | Spectrum of the modulator output with and without DWA for $0.3\%$          |    |

|      | matched DAC elements.                                                      | 83 |

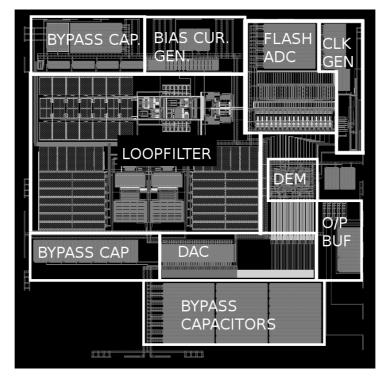

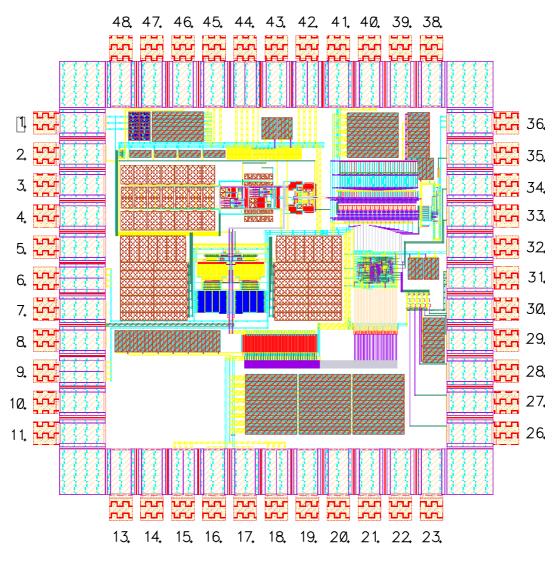

| 10.1 | Layout of the $\Delta\Sigma$ modulator.                                          | 84 |

|------|----------------------------------------------------------------------------------|----|

| 10.2 | Simulated spectrum of the $\Delta\Sigma$ modulator for a tone input at 4.5 kHz   | 86 |

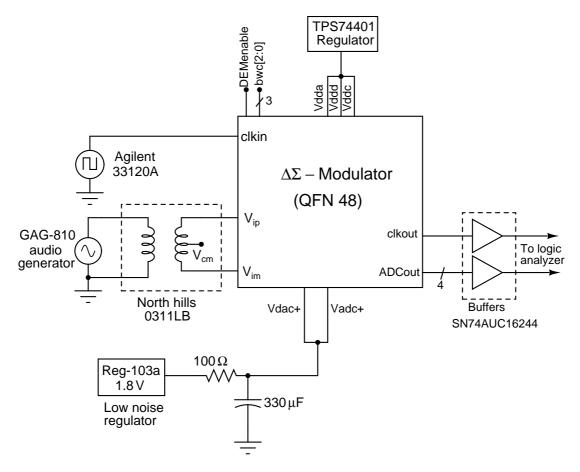

| 11.1 | Test setup of the $\Delta\Sigma$ modulator.                                      | 88 |

| 11.2 | Picture of the PCB for testing the $\Delta\Sigma$ modulator.                     | 89 |

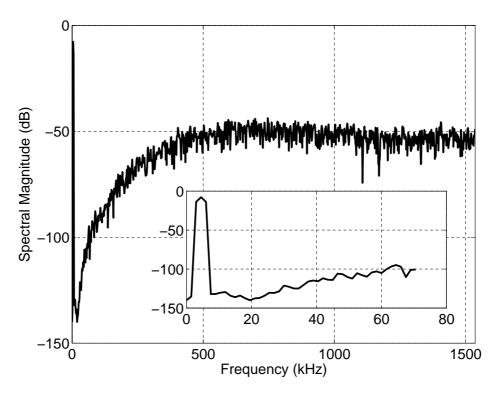

| 11.3 | Idle channel performance of the $\Delta\Sigma$ modulator chip                    | 90 |

| 11.4 | Idle channel performance with the differenital inputs open circuited.            | 91 |

| 11.5 | Spectrum from the $\Delta\Sigma$ modulator chip for a sinusoidal input at 5 kHz. | 92 |

| A.1  | Decimator chip.                                                                  | 94 |

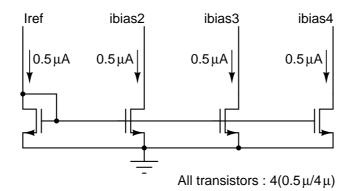

| C.1  | Bias current generation for op-amps                                              | 97 |

| D.1  | $\Delta\Sigma$ modulator chip                                                    | 98 |

### ABBREVIATIONS

ADC Analog to Digital Converter CAD Computer Aided Design CIFB Cascade of Integrators Feedback CIFF Cascade of Integrators Feed Forward **CMOS** Complementary Metal Oxide Semiconductor **CSD** Canonical Signed Digits CTDSM Continuous-Time Delta Sigma Modulator CTS **Clock Tree Synthesis** DAC Digital to Analog Converter DEM Dynamic Element Matching DNL **Differential Non Linearity** DR Dynamic Range DSP Digital Signal Processor DWA Data Weighted Averaging FIR Finite Impulse Response Field Programmable Gate Array **FPGA** HDL Hardware Description Language INL Integral Non Linearity LSB Least Significant Bit MOSFET Metal Oxide Semiconductor Field Effect Transistor MSA Maximum Stable Amplitude NRZ Non Return to Zero OBG Out of Band Gain

| OSR    | Oversampling Ratio                   |

|--------|--------------------------------------|

| Op-amp | Operational Amplifier                |

| PSD    | Power Spectral Density               |

| РСВ    | Printed Circuit Board                |

| RTL    | Register Transfer Level              |

| RZ     | Return to Zero                       |

| SNDR   | Signal to Noise and Distortion Ratio |

| SNR    | Signal to Noise Ratio                |

| SQNR   | Signal to Quantization Noise Ratio   |

| STF    | Signal Transfer Function             |

| SoC    | System on Chip                       |

| UGF    | Unity Gain Frequency                 |

| VCD    | Value Change Dump                    |

### **CHAPTER 1**

#### Introduction

There has been a huge emphasis on System on a Chip (SoC) designs over the last decade. In SoCs, all components of an electronic system are integrated into a single chip. E.g. Mobile phone, personal media players, routers. Data and signal processing in such a system is mostly digital in nature. Digital signals are immune to noise, can be stored easily and are easier for processing. A typical SoC contains a core Digital Signal Processor (DSP) for digital data/signal processing, memory blocks to store data, phase locked loops to control timing and data converters (Analog to digital converters, ADCs, and digital to analog converters, DACs) to interface with the real world.

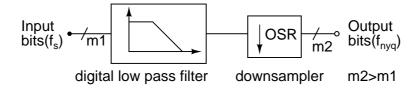

An ADC is characterized by its resolution, speed and power. The design described in this thesis lays emphasis on high resolution and low power. High resolution data converters are used in seismic monitoring, high fidelity audio, high accuracy instrumentation like strain gauges, pressure sensors.  $\Delta\Sigma$  ADCs can resolve signals as high as 20 bits in audio bandwidths.  $\Delta\Sigma$  ADCs are a class of oversampled converters wherein high resolution is obtained by virtue of oversampling and negative feedback that shapes the quantization noise out of the signal band. A  $\Delta\Sigma$  modulator encodes the analog signal with a smaller number of bits (1-4) at the oversampled rate. A decimator (decimation filter) is required to remove the out-of-band noise to a sufficient level and achieve the full resolution at the Nyquist rate of the signal.

This thesis aims at building the components of a  $\Delta\Sigma$  data conversion system for audio bandwidth with a low power consumption.

Very low power (90  $\mu$ W), high resolution (15 bit)  $\Delta\Sigma$  modulators for digital audio have already been proposed in [1][2]. This necessitates a decimator with a correspondingly low power in order to realize a low power analog to digital data conversion system. The first part of the thesis deals with the design of a low power decimator for a power optimized continuous-time  $\Delta\Sigma$  modulator for digital audio. The second part of the thesis deals with the design of a very high resolution, 18 bit (108 dB SNR), continuous-time  $\Delta\Sigma$  modulator in the bandwidth 20 Hz - 24 kHz.

### **1.1** Organization of the thesis

Chapters 2 - 5 form the first part of the thesis about the decimator.

**Chapter 2** gives a brief introduction to the concepts of decimation and the design targets for the decimator.

**Chapter 3** describes the architecture of the decimator and contains the description of various blocks in the decimator.

**Chapter 4** gives information about the digital synthesis of the decimator using standard cells and CAD tools. The simulation results are given in this chapter.

**Chapter 5** contains results from testing of the fabricated decimator chip and concludes the first part.

**Chapters 6 - 11** form the second part of the thesis about the design of a 18 bit  $\Delta\Sigma$  modulator.

**Chapter 6** contains a brief introduction on continuous-time  $\Delta \Sigma$  modulation and its implementation issues. It is then followed by the description of the targeted design and the system level design details.

**Chapter 7** describes the architecture and design of the continuous-time loop filter of the modulator.

**Chapter 8** describes the design of the four bit internal flash ADC and generation of multiphase clocks for the ADC.

**Chapter 9** contains the design of the feedback DAC and a dynamic element matching algorithm that fixes the effect of mismatch between DAC unit elements.

Chapter 10 shows the details of the fabricated chip and top level simulation results.

**Chapter 11** gives the measured results from the fabricated  $\Delta\Sigma$  modulator chip and concludes the design.

Chapter 12 draws some conclusions from this work.

#### **CHAPTER 2**

### **Introduction to decimators**

### **2.1** $\Delta \Sigma$ modulation

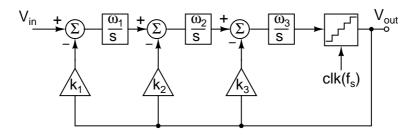

$\Delta\Sigma$  modulators are a class of data converters wherein the signal is oversampled and the quantizer is placed inside a negative feedback loop. The factor by which the sampling frequency  $(f_s)$  is greater than the Nyquist rate of the signal  $(f_{nyq})$  is termed as oversampling ratio,  $OSR = \frac{f_s}{f_{nyq}}$ . Figure 2.1 shows the block diagram of a discrete-time  $\Delta\Sigma$  modulator.

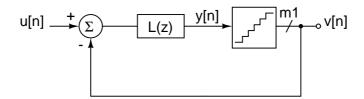

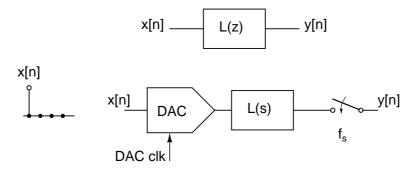

Figure 2.1: Block diagram of a discrete-time  $\Delta\Sigma$  modulator.

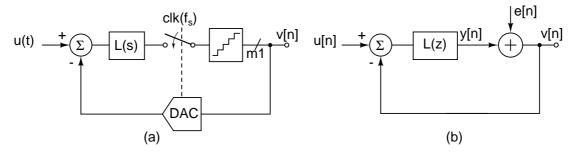

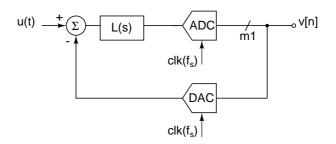

A continuous-time  $\Delta\Sigma$  modulator (CTDSM) employs a continuous-time loop filter and the sampling is done within the loop. The loop filter also behaves as an anti-aliasing filter [3]. Figure 2.2(a) shows the block diagram of a continuous-time  $\Delta\Sigma$  modulator. The quantizer is modelled as an additive noise source at the input of the quantizer.

Figure 2.2: CTDSM (a) Block diagram, (b) Discrete time equivalent with additive quantization noise model.

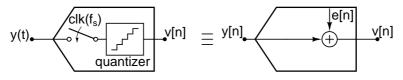

Figure 2.2(b) shows the additive noise equivalent. The quantization noise is assumed to be white and possess a uniform distribution. Denoting the quantization noise by e[n], the input signal by u[n] and the output signal by v[n], the transfer function from input to the output of the quantizer is written as

$$V(z) = \frac{L(z)}{1 + L(z)} \times U(z) + \frac{1}{1 + L(z)} \times E(z)$$

(2.1)

$$= \text{STF} \times U(z) + \text{NTF} \times E(z)$$

(2.2)

where STF (Signal transfer function) denotes the transfer from the input signal to the modulator output. NTF (Noise Transfer function) denotes the transfer function from the quantization noise to the modulator output. They are expressed as

$$STF(z) = \frac{V(z)}{U(z)} = \frac{L(z)}{1 + L(z)}$$

(2.3)

NTF(z) =

$$\frac{V(z)}{E(z)} = \frac{1}{1 + L(z)}$$

(2.4)

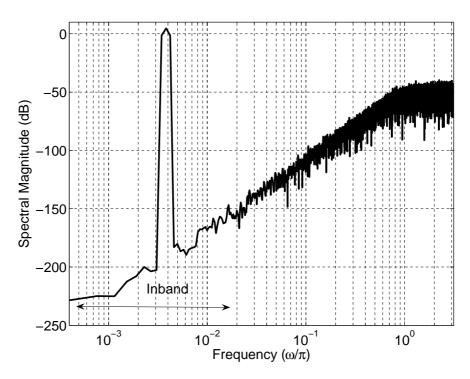

Usually a coarse quantizer of 1 to 4 bits resolution is used. The order of the modulator is same as the order of the loop filter. The NTF is designed to shape the quantization noise out of the signal band by appropriately choosing the loop filter. A typical spectrum of the output of a  $\Delta\Sigma$  modulator in response to a sine wave input is shown in Figure 2.3. The quantization noise is high pass shaped by the loop filter. The in-band signal to noise ratio (SNR) of the spectrum is 118 dB. Higher order modulators and higher quantizer resolutions are used to obtain higher resolution for  $\Delta\Sigma$  modulators [3]. The design of a  $\Delta\Sigma$  modulator is given in the second part of this thesis from Chapter 6.

Figure 2.3: Spectrum of a  $\Delta\Sigma$  modulator, Order: 3, OSR: 64.

### 2.2 Overview of decimation

#### 2.2.1 Downsampling

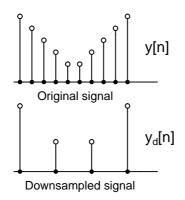

Downsampling is the process of reduction in the sampling rate of a discrete-time signal by dropping samples. Downsampling by a factor of M implies that out of M consecutive samples, M-1 samples are discarded and one sample is retained. Correspondingly the sampling rate of the downsampled signal changes from  $f_s$  to  $f_s/M$ . This is shown in Figure 2.4.

Figure 2.4: Illustration of downsampling by a factor of three.

Mathematically downsampling by a factor of M is expressed as

$$y_d[n] = y[Mn] \tag{2.5}$$

Let  $Y(e^{j\omega})$  and  $Y_d(e^{j\omega})$  denote the spectrum of the signal y[n] and  $y_d[n]$  respectively. The spectrum of the downsampled signal can be written as, [4]

$$Y_d(e^{j\omega}) = \frac{1}{M} \sum_{k=0}^{M-1} Y\left(e^{j\frac{\omega-2\pi k}{M}}\right)$$

(2.6)

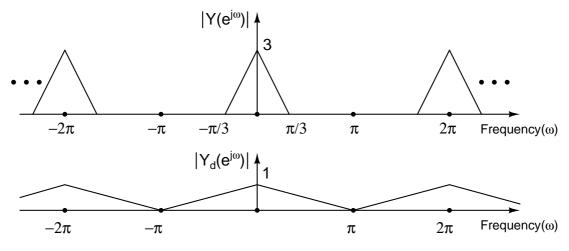

The spectrum of the downsampled signal in relationship with the original signal is illustrated in Figure 2.5. It can be seen that the spectrum of the signal y[n] expands after

Figure 2.5: Spectrum of the downsampled signal when M = 3.

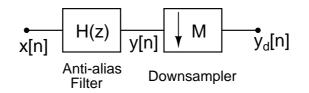

downsampling. To prevent aliasing of the signal,  $Y(e^{j\omega})$  has to be restricted to  $\frac{\pi}{M}$  or  $\frac{f_s}{2M}$ . Hence a digital anti-alias filter is necessary to filter out the components that alias into this band. Anti-alias filtering along with downsampling is termed as decimation. The block level representation of a decimator which downsamples by a factor of M is shown Figure 2.6.

Figure 2.6: A decimator that downsamples by M.

#### **2.2.2 Decimation in** $\Delta \Sigma$ modulation

The output of a  $\Delta\Sigma$  modulator contains the required in-band signal and the shaped noise as shown in Figure 2.3. To convert this oversampled signal to its Nyquist rate, the signal is downsampled by a factor of OSR. To prevent aliasing of the boosted quantization noise to the in-band the signal is digitally low pass filtered a priori. The block level equivalent of a decimator for a  $\Delta\Sigma$  modulator is shown in Figure 2.7.

Figure 2.7: Decimator for a  $\Delta\Sigma$  modulator.

### 2.3 Design targets for the decimator

The decimator described in this thesis is designed for a power optimized continuoustime  $\Delta\Sigma$  modulator [1] that was built in a 0.18  $\mu$ m CMOS process with 1.8 V supply. It is four bit modulator that has an OSR of 64 and operates at the sampling frequency,  $f_s = 3.072$  MHz. The modulator has an SNR of 93 dB in the bandwidth 20 Hz to 24 kHz and consumes a power of 90  $\mu$ W. A power target of 100  $\mu$ W is chosen for the decimator so that a low power  $\Delta\Sigma$  data conversion system can be realized. The characteristics of the  $\Delta\Sigma$  modulator and the requirements of the decimator are tabulated in Table 2.1 and Table 2.2 respectively.

| Table 2.1: Modulator characteristics |                   |  |

|--------------------------------------|-------------------|--|

| Sampling rate                        | 3.072 MHz         |  |

| OSR                                  | 64                |  |

| Nyquist rate                         | 48 kHz            |  |

| Modulator order                      | 3                 |  |

| SNR(20 Hz-24 kHz)                    | 93 dB             |  |

| Power                                | 90 µW             |  |

| Technology                           | $0.18 \mu m CMOS$ |  |

| <b>TT</b> 1 1 | $\sim$ | D !       | •            |

|---------------|--------|-----------|--------------|

| Table         | 1111   | Decimator | requirements |

| raute         | 4.4.   | Decimator | Icquitements |

|               |        |           |              |

|                   | 1                       |

|-------------------|-------------------------|

| No. of input bits | 4                       |

| Input rate        | 3.072 MHz               |

| Output rate       | 48 kHz                  |

| SNR               | 16 bits (96 dB)         |

| Passband edge     | 21.6 kHz                |

| Passband ripple   | $<\pm 0.05 \mathrm{dB}$ |

| Target power      | $< 100 \mu \mathrm{W}$  |

### **CHAPTER 3**

#### Architecture of the decimator

### 3.1 Multistage decimation

The objective of the decimator is to sufficiently attenuate the aliasing noise before downsampling so that the in-band signal to noise ratio (SNR) is not deteriorated. The relative bandwidth of a digital signal, defined as the ratio of the bandwidth of the signal to half the sampling rate, from a  $\Delta\Sigma$  modulator is 1/(2OSR). An ideal anti-alias filter accompanying the decimator has the following characteristics.

$$H(f) = \begin{cases} 1 & 0 \le f \le 1/(2 \text{ OSR}) \\ 0 & 1/(2 \text{ OSR}) < f \le 1/2 \end{cases}$$

(3.1)

But in reality all filters have a transition band of finite width and a stop band gain that is not zero. The anti-alias filter to be realized for the decimator needs to have narrow transition band. Such a filter if realized as a single filter has a very high order (>1000) [5]. A high order filter operating at a high frequency consumes a very high power.

Therefore, instead of using a single anti-alias filter operating at the input sampling rate and then downsampling to the Nyquist rate, filtering and downsampling is done in multiple stages. This is termed as multistage decimation [5][6]. According to (2.6), when a signal of bandwidth  $f_b$  is downsampled from a sampling rate  $f_s$  to  $f_s/M$ , the aliasing region lies centered at  $k \frac{f_s}{M}$  with a bandwidth of  $2f_b$ . Here k takes values  $0,1,2...\lceil M/2\rceil$ where  $\lceil \rceil$  denotes the ceiling function. It is ensured that in each stage, the noise in these aliasing bands are sufficiently attenuated by the filter that precedes the downsampling. The block diagram of this decimator employing multistage decimation is shown Figure 3.1.

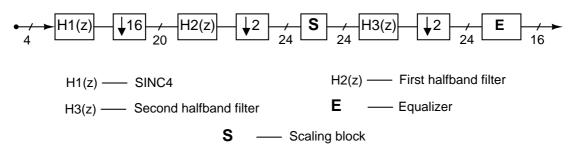

Figure 3.1: Block diagram of the multistage decimator.

The multistage decimator employs three stages of anti-alias filtering. The overall downsampling factor of sixty four is divided as 16, 2, 2 in these three stages. The first stage filter before the initial downsampling (16) is a cascade of four moving average filters (SINC4 filter). This filter operates at the maximum rate,  $f_s$ . A moving average filter can be implemented with only adders (without coefficient multipliers) and helps in saving power [7]. The remaining filtering is done with halfband filters and a downsampling factor of two is employed after each filter [6]. The equalizer corrects the droop caused by the SINC4 filter. The scaling block restores the signal to fullscale of the  $\Delta\Sigma$  modulator. It is intended to have linear phase response for the decimator, hence all filters used in this design have symmetric finite impulse response (FIR) characteristics. Each block and its implementation is described in detail in the rest of this chapter.

#### **3.2** SINC4 filter

The simplest form of digital low pass filtering is averaging N consecutive samples. Averaging N samples is done with a moving average filter/SINC filter. The transfer function of an N tap moving average filter is

$$H(z) = 1 + z^{-1} + z^{-2} + z^{-3} + \ldots + z^{-(N-1)}$$

(3.2)

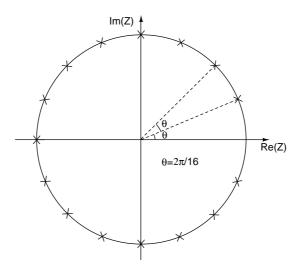

An N tap SINC filter has N-1 complex zeros distributed equally around the unit circle in the  $\mathcal{Z}$  plane as shown in Figure 3.2.

Figure 3.2: Zeros of a 16 tap SINC filter in the Z plane.

The signal is downsampled from 3.072 MHz to 192 kHz by a factor of sixteen after the first stage filtering. According to (2.6) the alias bands are located at integer multiples of  $\frac{f_s}{16}$ . The tap length of the SINC filter is chosen as N = 16 so that the complex zeros that creates nulls are located at the center of these alias bands.

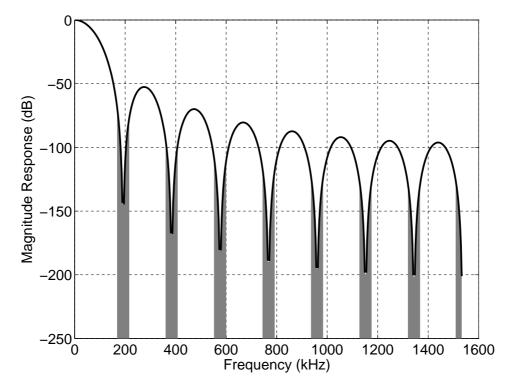

Figure 3.3: Frequency response of the SINC4 filter(aliasing bands in gray).

Attenuation provided in the stop band can be increased by cascading SINC filters. A third order  $\Delta\Sigma$  modulator shapes the quantization noise at its output as  $(1 - z^{-1})^3$  [3].

Hence the quantization noise power spectral density increases with frequency as  $f^3$ . Sufficient attenuation of the shaped quantization noise over the entire band is obtained with a cascade of four SINC filters (SINC4) that has a  $\frac{1}{f^4}$  roll off [8]. The frequency response of the cascade of four sixteen tap SINC filters (SINC4) is shown in Figure 3.3. The shaded areas in the frequency response are the noise aliasing bands for the SINC4 filter.

#### **3.2.1** Hogenauer structure

A convenient implementation of the SINC4 can be obtained by modifying the filter transfer function in (3.2) by introducing a pole and a zero at z = 1 [7].

$$H1(z) = \left[\frac{1-z^{-16}}{1-z^{-1}}\right]^4 = \left[\frac{1}{1-z^{-1}}\right]^4 \left[1-z^{-16}\right]^4$$

(3.3)

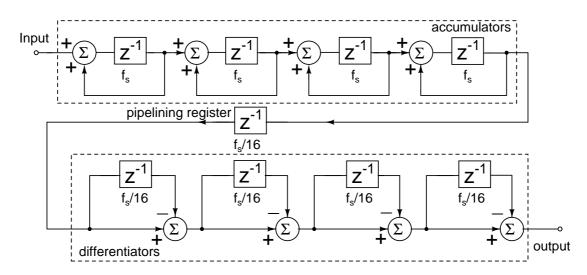

H1(z) along with the downsampling of sixteen is implemented in two steps as shown

|                                                                            | accumulators                                                      | differentiators                             |  |

|----------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------|--|

| $\boxed{\left[\frac{1-z^{-16}}{1-z^{-1}}\right]^4} \rightarrow \boxed{16}$ | $\equiv \left[ \frac{1}{1 - z^{-1}} \right]^4 \longrightarrow 16$ | $\longrightarrow \left[1 - z^{-1}\right]^4$ |  |

Figure 3.4: Implementation of SINC4 as Hogenauer structure.

in Figure 3.4. At first, the accumulation operations  $\left(\frac{1}{1-z^{-1}}\right)^4$  are done at the rate  $f_s$ . Then, the operation  $[1-z^{-16}]^4$  and the downsampling of sixteen are implemented with cascade of four differentiators  $(1-z^{-1})$  working at  $f_s/16$ . This structure is called Hogenauer structure [7].

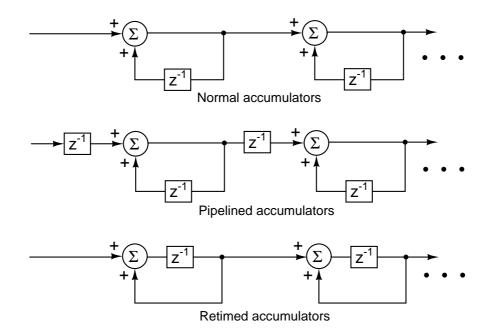

#### 3.2.2 Pipelining and retiming of SINC4

The accumulators are first pipelined by inserting a register at the input of each accumulators as shown in Figure 3.5. The registers are then retimed to a single register in the forward path of each accumulators [9]. Hence the glitches in combinational adders in one accumulator are prevented from propagating to the next accumulator, thereby reducing unwanted switching power.

Figure 3.5: Retiming and pipelining of accumulators for power reduction.

Figure 3.6: Implementation of the SINC4 filter.

Similarly the pipelining register at the output of the fourth accumulator (refer Figure 3.6) prevents the switching data at  $f_s$  propagating through the differentiators. It is determined through simulations that retiming of the registers in the accumulators and the pipelined register saves 46 % of power in the SINC4 stage.

Overflow in the accumulators does not cause signal distortion if the signal representa-

tion is based on wrap around arithmetic (binary, 2's complement) and all register widths are chosen according to the relationship [7].

Bit width

$$= B_{in} + k \log_2 N$$

(3.4)

Here  $B_{in}$  is the input bit width (4 bit binary), k (4) is the number of cascaded SINC stages and N (16) is the tap length of the SINC. Hence all the registers are chosen to be 20 bit wide.

#### **3.3 Halfband filters**

Halfband filters are a class of equiripple FIR filters with order  $N_{ord} = 4 P + 2$ , where  $P \in \{1,2,3...\}$ . Halfband filters have a gain of 0.5 at one fourth of the clock frequency  $(f_{clk}/4)$ . Hence the maximum downsampling factor that can occur after a halfband filtering is two. The middle sample of the impulse response of a halfband filter is 0.5 and the impulse response is symmetric about this sample. Odd tap weights are zero and hence there is a reduction in the number of multipliers employed.

The signal at the output of the SINC4 filter is at four times the Nyquist rate (192 kHz). Two halfband filters along with the downsampling by a factor of two after each filter downconverts the signal to its Nyquist rate. The orders of the halfband filters are chosen such that the overall passband ripple of the decimator is constrained to  $\pm 0.05$  dB and the aliasing noise does not cause degradation in the in-band SNR.

The first halfband filter is chosen to have a wide transition band. A tenth order halfband filter that has a stop band attenuation of 60 dB is chosen. This filter operates with the clock frequency of 192 kHz. The aliasing band lies in the region 72 kHz to 96 kHz.

The second halfband filter provides the final filtering before the signal is downsampled to its Nyquist rate (48 kHz). The filter is designed to have a narrow transition band and a

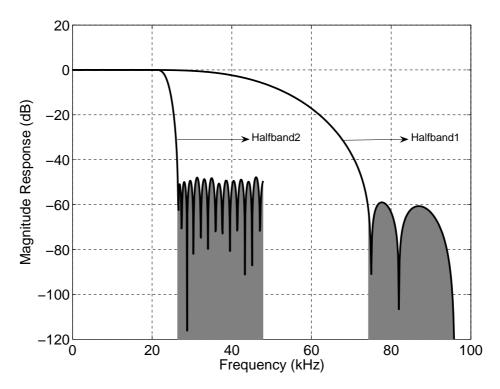

stop band attenuation of 50 dB. A fiftieth order filter is chosen. This filter operates with the clock frequency of 96 kHz. The aliasing band lies in the region 24 kHz to 48 kHz. The frequency response of the first and the second halfband filters are shown in Figure 3.7. The aliasing bands of each downsampling operation is shaded gray.

Figure 3.7: Frequency response: The first and the second halfband filters.

#### **3.3.1** Implementation of the halfband filters

This section deals with various optimization techniques that are implemented in the halfband filters which aid reduction of power and hardware. The three techniques that are employed in halfband filters are

- 1. Polyphase structure

- 2. Canonical signed digits encoding

- 3. Optimal data width in arithmetic units

The signal in halfband filters and subsequent other blocks are encoded in 2's complement.

#### **3.3.1.1** Polyphase structure

Any filter followed by downsampling can be implemented as a polyphase structure [4][9]. The input data stream is split into multiple phases. The filter transfer function is also split into multiple parts and each transfer function operates on each phase of the signal. Outputs from all these phases are combined to produce the filtered and downsampled version of the signal. Each individual phase operates at the downsampled rate and hence the effective frequency of operation of the filter is reduced thereby saving power.

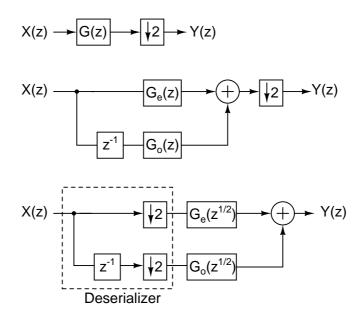

Implementation of a halfband filter as a polyphase structure is explained by the following illustration. Let the filter transfer function be G(z) and the downsampling factor be two. Let G(z) be represented as

$$G(z) = \sum_{i=0}^{L} a_i z^{-i}$$

(3.5)

The transfer function is split into two phases as given in (3.6).

$$G(z) = \left\{ a_0 + a_2 z^{-2} + a_4 z^{-4} + \ldots + a_L z^{-L} \right\} + z^{-1} \left\{ a_1 + a_3 z^{-2} + a_5 z^{-4} + \ldots + a_{L-1} z^{-(L-2)} \right\}$$

=  $G_e(z) + z^{-1} G_o(z)$  (3.6)

Polyphase implementation of the filtering and downsampling is explained in Figure 3.8.

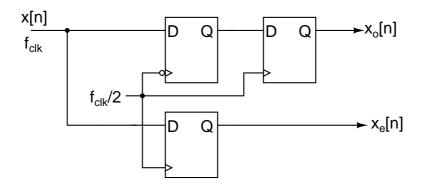

The circuit that splits the input data into odd and even data streams is shown in Figure 3.9. It can be seen that the filters  $G_e(z^{1/2})$  and  $G_o(z^{1/2})$  work at half the clock rate.

Figure 3.8: Polyphase structure in halfband filters.

Figure 3.9: Deserializer: Splits data into even and odd streams.

#### 3.3.1.2 Canonical Signed Digits

In a binary representation of a number, digits are either 0 or 1. In signed digit representation of binary numbers, digits belong to the triplet  $\{-1,0,1\}$ . Signed digit representation of a number is not unique [10]. For example, the number 7 can be written in following ways in signed digit representation.

| (0 | 1  | 1  | $1)_{2}$ | = | 7 |

|----|----|----|----------|---|---|

| (1 | 0  | -1 | $1)_{2}$ | = | 7 |

| (1 | -1 | 1  | $1)_{2}$ | = | 7 |

| (1 | 0  | 0  | $(-1)_2$ | = | 7 |

Encoding a binary number in signed digits representation such that it contains the fewest number of non-zero bits is called canonic signed digit (CSD) [11]. Hence encoding the tap weights of a filter in CSD reduces the number of multiplication operations that saves hardware and power. Unlike the signed digit representation, the CSD representation of a number is unique.

The CSD representation is also applicable for fractional numbers. For e.g.  $0.4375 = 2^{-1} - 2^{-4}$ . Truncation of tap weights to finite number of CSD alters the frequency response of the filter. The number of CSDs in tap weights is decided by the accuracy of the frequency response (passband ripples). In this decimator design, the tap weights are fourteen bits wide.

#### **3.3.1.3** Data width in halfband filters

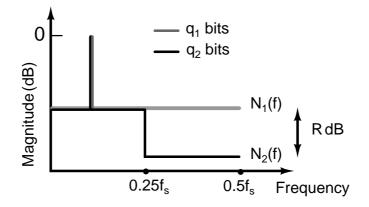

In order to ensure proper filtering of the quantization noise in halfband filters, the digital signal should support adequate dynamic range. More the number of bits in the filtering operation, higher is the dynamic range of the filtered signal. A high dynamic range filtering is required to ensure adequate suppression of the noise in the aliasing bands. The minimum number of bits required is explained with the help of Figure 3.10.

Figure 3.10: Filtering of quantization noise floor.

The quantization noise Power spectral density (PSD) of a digital signal, with fullscale 0 dB, quantized to  $q_1$  bits at a sampling rate 1 Hz is  $N_1(f) = 10^{-6q_1/10}$ . To attenuate

a small band of its quantization noise by  $R \,dB$ , the quantization noise floor has to be lowered by increasing the number of bits to  $q_2$  (Refer Figure 3.10). Hence for the filtered signal the quantization noise PSD is  $N_2(f) = 10^{-6q_2/10}$ . It can be concluded from Figure 3.10 that

$$R = 10 \log_{10} \frac{N_2(f)}{N_1(f)} \tag{3.7}$$

or

$$q_2 = q_1 + \frac{R}{6}$$

(3.8)

It can be seen that every extra bit handles 6 dB more dynamic range in filtering. The signal to be filtered has a resolution of 96 dB ( $q_1 = 16$ ). It is found that a 48 dB attenuation of aliasing noise (with respect to the in-band noise floor) is sufficient to preserve the in-band SNR. Hence the internal states of the filter (adders and multipliers) are twenty four bit wide ( $q_2 = 24$ ).

#### 3.3.1.4 Implementation details of the first halfband filter

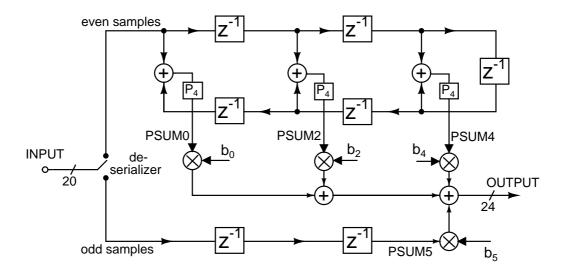

The block diagram of the polyphase implementation of the first halfband filter is shown in Figure 3.11. The  $P_4$  block pads four LSBs to the data path to increase the dynamic range to 24 bits. The tap weights of the filter,  $b_0$ ,  $b_2$ ,  $b_4$ ,  $b_5$  are symmetric about the middle sample  $b_5 = 0.5$ .

Figure 3.11: Polyphase implementation of the first halfband filter ( $10^{th}$  order).

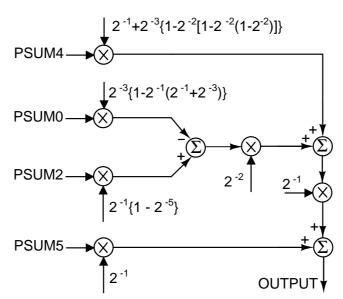

The output of the filter is obtained from the internal states PSUM0, PSUM2, PSUM4, PSUM5 as shown in Figure 3.12. The tap weights are less than unity and hence are expanded in powers of  $2^{-1}$  with CSD encoding. A  $2^{-m}$  in the tap weight corresponds to right shifting the signal by dropping its m LSBs. Hence a tap weight multiplication is obtained by adding and subtracting right shifted signals. This multiplication is further nested based on Horner's rule [6]. This reduces the effective right shift operation and hence the effect of truncation noise. For e.g.  $2^{-3}-2^{-5}-2^{-7} = 2^{-3}\{1-2^{-1}(2^{-1}+2^{-3})\}$ . This nested multiplication requires extra shifting operations compared to the non nested multiplication. However no explicit hardware is required to implement a shifter because shifting involves dropping LSBs.

Figure 3.12: Obtaining output from the internal states.

## 3.4 Equalizer

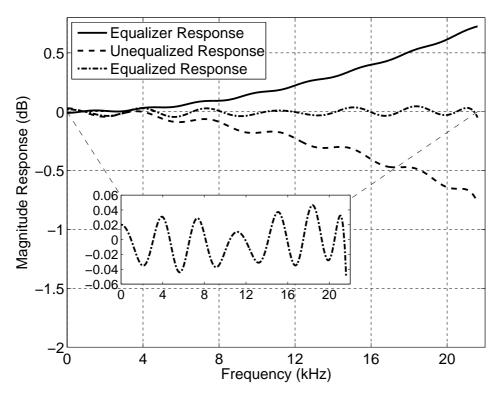

It is required for the decimator to have a passband gain error that is constrained to  $\pm 0.05$  dB. The equalizer is an FIR filter that corrects the passband droop caused by the SINC4 filter [8]. The equalizer works at the Nyquist rate. The magnitude response of the equalizer is inverse that of the SINC4 filter in the in-band (0-24 kHz). A thirty fourth order FIR filter is chosen for equalization. The tap weights of the equalizer are

found using *Parks McClellan* method. As in the halfband filters, the tap weights are encoded in CSD and multiplications are nested. Figure 3.13 shows frequency response of the equalizer, the passband frequency response of the unequalized decimator and the equalized decimator. The inset shows that passband ripples of the decimator is constrained to  $\pm 0.05$  dB. After equalization the signal is rounded from 24 bits to 16 bits by dropping the eight LSBs.

Figure 3.13: Frequency response of the Equalizer, the unequalized & the equalized decimator.

## **3.5 Scaling block**

A  $\Delta\Sigma$  modulator has a maximum stable amplitude (MSA) at which the peak SNR is obtained. Beyond the MSA the modulator goes to instability and the SNR reduces and finally approaches zero [3]. MSA is expressed in percent of fullscale. At peak SNR the output swing of the modulator is MSA × fullscale. In order to achieve the peak SNR at the Nyquist rate, after decimation and truncating the signal to appropriate number of bits, the signal has to swing to its fullscale. Hence the signal is scaled by  $\frac{1}{MSA}$  to obtain fullscale swings at the output of the decimator.

The  $\Delta\Sigma$  modulator in [1] has an MSA around 85 % of the fullscale. The output of the modulator swings fully in its available range due to the presence of large quantization noise. At the output of the first halfband filter, the maximum output swing is found to be 85 % of the fullscale, same as the MSA of the modulator. Hence the scaling is done after the first halfband filter where the quantization noise is attenuated to a level comparable to the noise floor in the in-band.

$$S = \frac{1}{0.8605} = 1 + 2^{-2} \left\{ 2^{-1} + 2^{-2} \left( 2^{-1} + 2^{-3} \left[ 1 - 2^{-2} \right] \right) \right\}$$

The scaling value is kept slightly smaller than  $\frac{1}{MSA}$  to prevent overflow. The presence of passband ripples in other filters and the fact that the decimator operates with a finite number of bits can result in a overflow when the filter processes a signal of amplitude that is close to the fullscale. This scaling value is encoded in CSD and implemented with Horner's rule.

# **CHAPTER 4**

# Synthesis of the decimator

The decimator is designed in a  $0.18 \,\mu\text{m}$  CMOS process with a  $1.8 \,\text{V}$  supply. To make it easy to port the design to different processes, handcrafted circuitry is avoided. The design is developed with standard cells using automated CAD tools. The behavioral description of the filter is written a hardware description language (Verilog) at register transfer level (RTL) abstraction. The CAD tools that are used for designing and testing the decimator are tabulated in Table 4.1.

Table 4.1: CAD tools used for the decimator design

| Tool                       | Purpose                     |

|----------------------------|-----------------------------|

| MATLAB                     | System design and modelling |

| Design Compiler (Synopsys) | Synthesis                   |

| SoC Encounter (Cadence)    | Place & Route               |

| Prime Time (Synopsys)      | Timing verification         |

| Prime Power (Synopsys)     | Power analysis              |

| Modelsim (Mentor)          | Simulation                  |

## 4.1 Description of design flow

The preliminary design involves testing the decimator in MATLAB to ensure that the SNR performance is satisfactory. The resolution of arithmetic operations in MATLAB is the precision of the computer (usually 32 bits). The description of the decimator is then coded in verilog with the appropriate bit precision as described in earlier chapters. An initial simulation of the entire system is carried out by simulating the verilog code with the tool *Modelsim* to verify the functionality and SNR performance.

The verilog netlist of the design is then translated to a gate level netlist using the tool *De*sign Compiler. All design constraints such as load capacitance, area, power, frequency of operation are given during this synthesis.

In Place & Route the CAD tool performs three major tasks

- Place the layout of standard cells according to the floor plan

- Clock tree synthesis (CTS)

- Route the design to meet the timing

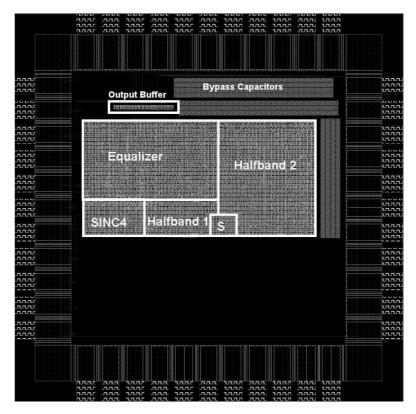

The timing closure is ensured after place and route with *Prime Time*. The design is ensured to be devoid of setup, hold, reset removal and rise/fall time violations. The design after place and route, with the annotation of interconnect delays, is simulated and verified for functionality. The layout of the final design is shown in Figure 4.1. The area occupied by the decimator core is 0.46 mm<sup>2</sup>.

Figure 4.1: Layout of the decimator chip.

### 4.1.1 Synthesis & simulation results

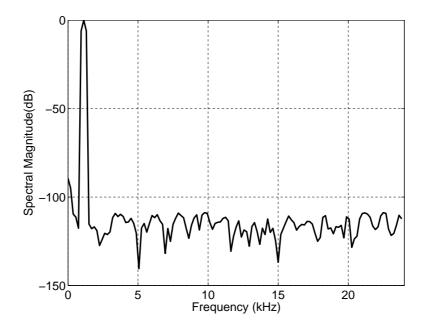

The input test stimulus for the decimator is obtained through simulations in MATLAB with the help of the  $\Delta\Sigma$  toolbox [3]. The signal is translated to corresponding verilog format for simulating it with the netlist obtained after Place & Route. The spectrum of the output signal is obtained and SNR is evaluated at the Nyquist rate. The decimator is tested for SNR performance with sine wave excitation of different frequencies. A sample spectrum from the output of the modulator is shown in Figure 4.2. The peak output SNR of the decimator is 95.8 dB.

Figure 4.2: Simulated spectrum of the decimator output, SNR=95.8 dB.

### 4.1.2 **Power estimation**

The power consumption of a digital circuit depends upon the switching activity in the circuit. The signal dependent power consumption of a digital circuit is analyzed using the tool *Prime Power*. The power consumption is estimated based on observing the switching activity at all nodes in the circuit. A value change dump (VCD) file that represents the switching activity of a circuit for a particular test vector is generated using *Modelsim*. The tool *Prime Power* estimates the power using this VCD file and the

gate level netlist. The power consumption of the decimator for various test inputs is tabulated in Table 4.2. It is seen that the power consumption of the decimator doesn't

| Test stimulus      | <b>Power</b> ( $\mu$ <b>W</b> ) |

|--------------------|---------------------------------|

| Tone at 1.6875 kHz | 96.7                            |

| White noise        | 100.9                           |

| Zero input         | 99.7                            |

Table 4.2: Power consumption for various test inputs

depend upon the type of input. This is because a sequential circuit's toggling activity depends mainly upon the clock rate. The power consumption of various blocks of the decimator is given in Table 4.3.

| Block           | <b>Power</b> ( $\mu$ <b>W</b> ) |

|-----------------|---------------------------------|

| SINC4           | 46.4                            |

| First halfband  | 5.9                             |

| Second halfband | 14.1                            |

| Equalizer       | 15.2                            |

| Scaling block   | 2.3                             |

| Clock tree      | 12.7                            |

| Total           | 96.7                            |

Table 4.3: Power consumption of the blocks of the decimator

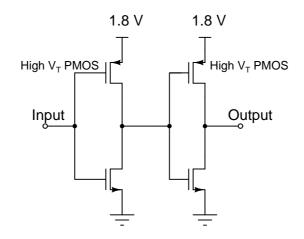

# 4.2 Level translator

The power consumption of any digital circuit can be reduced by reducing the supply voltage in trade off for the speed of operation of the system. It is intended to make the decimator work at a supply smaller than 1.8 V to reduce power. The logic levels of the output from the decimator is converted to 1.8 V with a level translator. The schematic of the level translator is shown in Figure 4.3.

The level translator has a static power consumption if its input logic 1 voltage is lesser than 1.8 V. Hence PMOS transistors with a large threshold voltage ( $V_T = -0.72$  V) are used to reduce this static power consumption.

Figure 4.3: Schematic of the level translator.

Through simulations it is found that a single level translator consumes a power of 245 nA from 1.8 V supply at fast-fast transistor corner when level translating an alternating data that has logic levels 0.9 V and 0 V at a frequency of 48 kHz. Hence the power consumption of seventeen level translators (digital output data and clock) consumes a power of 7.5  $\mu$ W. The power reduction in the decimator core at a reduced supply is expected to be much larger than the increased power consumption in level translators. Hence the overall power consumption of the decimator is expected to reduce further.

# **CHAPTER 5**

# Measured results from the decimator chip

## 5.1 Test setup

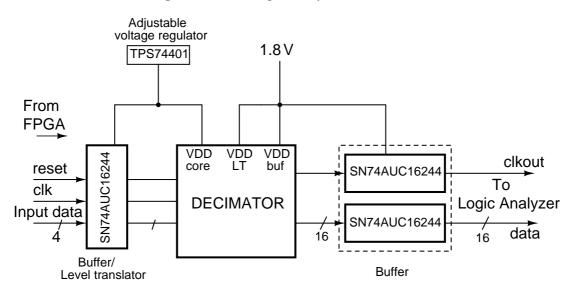

The block diagram of the test setup is shown in Figure 5.1. An FPGA is programmed to emulate the output of the  $\Delta\Sigma$  modulator [1]. The FPGA generates the four bit data synchronized to a 3.072 MHz clock along with the RESET signal. The output signal from the decimator is captured with a logic analyzer.

Figure 5.1: Block diagram of the test setup.

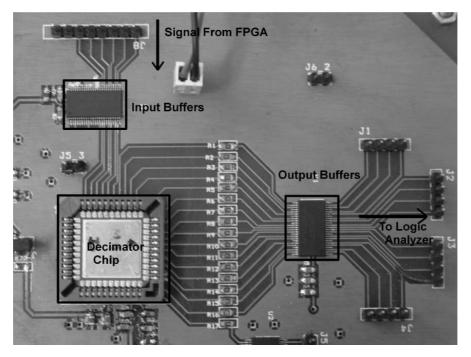

A two layer PCB is designed to test the chip. Provision is made to adjust the supply voltage of the decimator core. Figure 5.2 shows the picture of the PCB designed for testing the chip. The following measurements are made.

- To evaluate the SNR from the decimator's output spectrum for a tone input.

- Compare time domain samples from simulation and measurement for an impulse input.

- Scale the decimator core's supply voltage ensuring reliable operation and observe the power reduction.

Figure 5.2: Picture of the test PCB.

# 5.2 Results from the fabricated chip

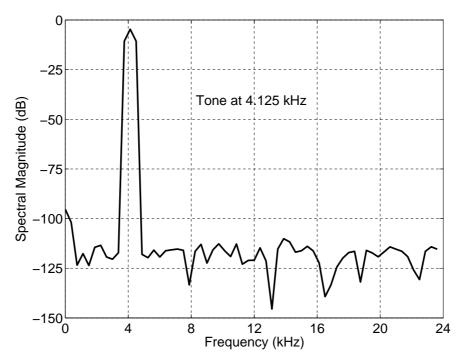

Figure 5.3 shows the spectrum obtained from the output of decimator excited by a sine wave input.

Figure 5.3: Measured spectrum of the decimator's output.

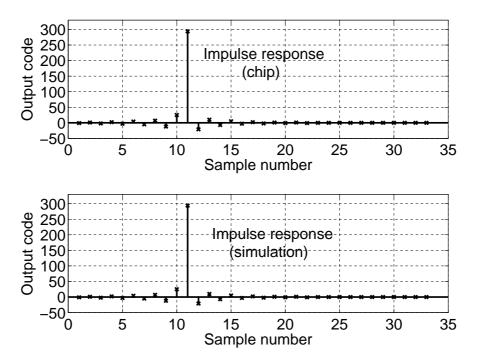

It is found that the SNR computed from this spectrum matches exactly with the SNR obtained from simulations. It is also verified that the time domain impulse response samples from the chip matches with the impulse response samples obtained through simulation. The impulse response samples from the chip and from simulation are shown in Figure 5.4.

Figure 5.4: Comparison of the impulse responses.

## 5.2.1 Power measurement

At the nominal supply of 1.8 V, the power consumption of the chip is  $104 \mu$ W. This matches closely with the simulation estimate of  $96 \mu$ W. It is observed that the chip is functional correctly down to a power supply voltage of 0.9 V when the system is running at 3.072 MHz. The power consumption of the decimator and the level translator across multiple supply voltages is given in Table 5.1.

It is observed that the power reduction obtained in the core is 77.4% at the supply voltage of 0.9 V. The power consumption of the level translators when the core supply is 0.9 V is very high (12.7 times larger than the simulated estimate). It is found that the

| Core power | Decimator Core               |                                 | Level Translator (1.8 V)     |                                 |

|------------|------------------------------|---------------------------------|------------------------------|---------------------------------|

| supply(V)  | <b>Current</b> (µ <b>A</b> ) | <b>Power</b> ( $\mu$ <b>W</b> ) | <b>Current</b> (µ <b>A</b> ) | <b>Power</b> ( $\mu$ <b>W</b> ) |

| 1.8        | 58                           | 104.4                           | $\approx 0$                  | pprox 0                         |

| 1.5        | 46                           | 69.0                            | 0.3                          | 0.54                            |

| 1.2        | 36                           | 43.2                            | 13.2                         | 23.8                            |

| 1.0        | 29                           | 29.0                            | 37.8                         | 68                              |

| 0.9        | 26                           | 23.4                            | 53.8                         | 97                              |

Table 5.1: Power consumption for various supply voltages

threshold voltage of the fabricated PMOS transistors are unusually very low (-0.3 V in comparison to its nominal value of -0.72 V) resulting in a large static power consumption. To avoid this a level translator with latching action is preferred [12].

## 5.3 Summary

A low power decimator has been designed and implemented with the help of standard cells. All levels of optimizations are carried out in the architectural level and automated with CAD tools to obtain quick design. The power consumption of the decimator has been made as same as its modulator [1] which proves that it is possible to design a decimator with as low power as recently published low power  $\Delta\Sigma$  modulators. As the decimator is functional down to 0.9 V, the power consumption can be further reduced by generating 0.9 V from a 1.8 V supply. Table 5.2 gives the performance summary of the decimator.

| No. of input bits               | 4                                |

|---------------------------------|----------------------------------|

| Input rate                      | 3.072 MHz                        |

| No. of output bits              | 16                               |

| Output rate                     | 48 kHz                           |

| SNR                             | 96 dB                            |

| Passband edge                   | 21.6 kHz                         |

| Passband ripple                 | $<\pm 0.05 \mathrm{dB}$          |

| Power consumption(1.8 V supply) | $104\mu\mathrm{W}$               |

| Technology                      | $0.18\mu\mathrm{m}\mathrm{CMOS}$ |

|                                 |                                  |

Table 5.2: Performance summary of the decimator

## **CHAPTER 6**

# $\Delta\Sigma$ modulator fundamentals

Analog to digital converters (ADCs) are systems that convert an analog signal to digital bits through sampling and quantization. An analog signal that is bandlimited to a frequency ( $f_b$ ) can be perfectly reconstructed from its discrete-time samples if the sampling rate ( $f_s$ ) is greater than its Nyquist rate i.e.  $f_s > 2 f_b$ . This principle is referred to as the Nyquist-Shannon sampling theorem. Quantizing the amplitude of the discrete samples can be treated as an addition of an error to the original signal. This error, called the quantization noise, is assumed to be random, uncorrelated with the original signal, uniformly distributed and to have a white spectrum. These assumptions become less valid when the quantization interval (difference between adjacent quantization levels) becomes comparable to the signal amplitude. The block level representation of an ADC is shown in Figure 6.1.

Figure 6.1: Block level representation of an ADC and its additive quantization noise model.

The quality of the digital signal depends on the strength of the quantization noise which in turn depends on the quantization interval  $V_{lsb}$ . The mean squared value of the quantization noise is  $V_{lsb}^2/12$ . The term signal to quantization noise ratio (SQNR) which is the ratio of mean squared value of the signal to the mean squared value of the quantization noise is a measure of the quality of the digital signal. For an N bit ADC that has its fullscale (quantizer saturation limits) of A, the quantization interval is,  $V_{lsb} = \frac{A}{2^N}$ . Hence the maximum SQNR of a sine wave signal that swings fullscale can be expressed

# **6.1** Continuous-time $\Delta \Sigma$ modulation

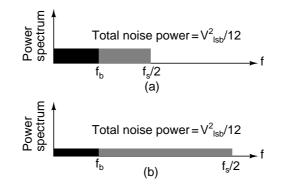

The quantization noise spectrum of a sampled and quantized signal at its Nyquist rate is shown in Figure 6.2(a). The total quantization noise power is  $V_{lsb}^2/12$ . The quantization noise spectrum of an oversampled and quantized signal is shown in Figure 6.2(b). The in-band quantization noise power of the oversampled signal in a bandwidth of  $f_b$  is  $\frac{V_{lsb}^2}{12f_s/2}f_b$ . This can be written in terms of the oversampling ratio as  $\frac{V_{lsb}^2}{12\text{OSR}}$ .

Figure 6.2: Quantization noise spectrum (a) Nyquist rate, (b) Oversampled rate.

Doubling the sampling rate reduces the in-band quantization noise power by a factor of two and hence increases the SQNR by 3 dB. The effective number of bits  $(N_{eff})$  of the conversion is defined using (6.1) as

$$N_{eff} = \frac{\text{SQNR}_{\text{max}}(\text{dB}) - 1.76}{6.02}$$

(6.2)

The quantization noise in the in-band can be further attenuated by placing the ADC inside a negative feedback loop. This process is called  $\Delta\Sigma$  modulation.

Figure 6.3 shows the block diagram of a continuous-time  $\Delta\Sigma$  modulator (CTDSM). It has a continuous-time loop filter, L(s), that has a large gain in the bandwidth of interest.

as

Figure 6.3: Block diagram of a continuous-time  $\Delta\Sigma$  modulator.

The signal is oversampled and quantized to multiple levels by the internal ADC. The DAC feeds back an analog signal back to the loop filter.

Usually a coarse internal ADC of 1 to 4 bits resolution is used. The quantization noise of the internal ADC when referred at the output is suppressed by the large gain of the loop filter. Hence large SQNR of effective number of bits  $(N_{eff})$  of 20 or higher is easily achieved. The required noise transfer function (NTF) is obtained by appropriately choosing the loop filter transfer function L(s). Higher order loop filter provides more suppression of the quantization noise and have aggressive noise shaping. For an  $L^{\text{th}}$ order loop filter having noise transfer function,  $\text{NTF}(z) = (1 - z^{-1})^L$ , the in-band noise power is approximately [13].

$$P_e = \frac{V_{lsb}^2}{12} \frac{\pi^{2L}}{2L+1} \left(\frac{1}{\text{OSR}^{2L+1}}\right)$$

(6.3)

It can be seen that for a given order (L) of the modulator the in-band quantization noise power reduces as 6L+3 dB for every doubling of OSR. Hence higher sampling rates are required to increase the effective number of bits  $(N_{eff})$  for a given signal bandwidth  $(f_b)$ . The in-band quantization noise power can also be reduced by increasing the order (L) of the modulator. Modulators with order greater than two are only conditionally stable [14]. For higher order modulators, the internal ADC gets overloaded even for an input to the modulator which is much smaller than the fullscale of the ADC. This reduces the maximum stable amplitude (MSA) of the modulator.

#### 6.1.1 Advantages of a CTDSM

In discrete-time  $\Delta\Sigma$  modulators (DTDSMs) the loop filter is a discrete-time filter and the sampling is done outside the loop whereas in CTDSMs the loop filter is a continuoustime filter and the signal is sampled inside the loop. CTDSMs are preferred over DTDSMs for the following reasons.

- 1. CTDSMs possess inherent anti-aliasing property which eliminates the need of an external anti-aliasing filter [13]. The loop filter behaves as an anti-alias filter.

- 2. The sampling is done at a less sensitive node of the loop. Hence any imperfections and errors due to sampling are shaped by the NTF.

- 3. CTDSMs can operate at a much higher clock rate compared to discrete-time modulators [13]. The loop filter in a CTDSM which is usually implemented with active RC integrators or  $g_m - C$  integrators has less stringent requirements for the settling of the op-amps in comparison to a discrete-time modulator.

### 6.1.2 Performance measures

#### 6.1.2.1 Signal to noise ratio

Signal to noise ratio (SNR) is the ratio of signal power to the integrated noise power in the in-band. The signal is usually a tone whose frequency is lesser than  $f_b$ . The in-band noise power is evaluated from the spectrum of the modulator's output by integrating the noise power in the bandwidth  $0 - f_b$ . Signal to noise and distortion ratio (SNDR) is a term that is the ratio of signal power to the sum of the noise power and distortion components. Hence the effective number of bits  $(N_{eff})$  of the digitization process is modified as

$$N_{eff} = \frac{\text{SNDR}_{\text{max}}(\text{dB}) - 1.76}{6.02}$$

(6.4)

#### 6.1.2.2 Dynamic range

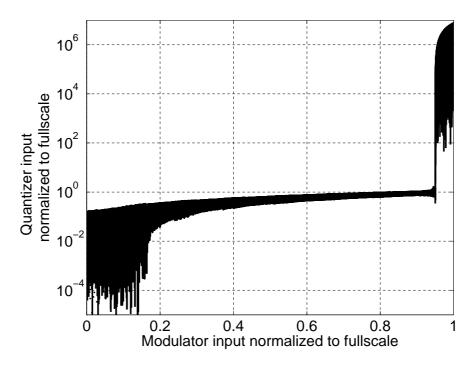

There exists a range of input amplitudes for which the output SNR of the modulator is positive. As the input signal amplitude increases from a small value the SNR increases proportionally. The input amplitude to the internal ADC/quantizer that contains the signal and the shaped quantization noise also increases proportionally. When the input amplitude reaches a critical amplitude, termed as the maximum stable amplitude (MSA), the internal ADC gets overloaded and as a result the modulator tends to be unstable. Figure 6.4 shows an example plot of the input to the internal ADC as the input amplitude to the modulator is ramped slowly. The MSA is around 88 % of the fullscale at which the input to the ADC starts increasing rapidly.

Figure 6.4: Plot of input to the internal ADC when the modulator input is a slow ramp.

For signal amplitudes larger than the MSA, the SNR rapidly drops to zero. The ratio of maximum signal amplitude to the minimum signal amplitude for which the SNR of the modulator remains positive is termed as the dynamic range (DR) of the modulator.

# 6.2 Design targets for the CTDSM

A large SQNR with effective number of bits of the order of 20 or more can be easily achieved in audio bandwidths with  $\Delta\Sigma$  modulators. However, the circuit performance of a CTDSM is limited by electronic noise of resistors and transistors in the circuit, the nonlinearity of the feedback DAC and the loop filter, clock jitter and excess loop delay. The performance summary of a CTDSM that is designed for 15 bit resolution in audio bandwidth is given in Table 6.1.

| Table 6.1: Performance summary of the CTDSM [1] |                         |  |

|-------------------------------------------------|-------------------------|--|

| Signal bandwidth/Clock rate                     | 24 kHz/3.072 MHz        |  |

| Dynamic range/SNR/SNDR                          | 93.5 dB/92.5 dB/90.8 dB |  |

| Active area                                     | $0.72\mathrm{mm}^2$     |  |

| Process/Supply voltage                          | 0.18 μm CMOS/1.8 V      |  |

| Power dissipation                               | $90\mu\mathrm{W}$       |  |

| Figure of merit                                 | 0.049 pJ/level          |  |

This work targets to design a CTDSM to achieve SNR of 108 dB (18 bit) by scaling the design [1] for noise and addressing various nonidealities. The design targets for the CTDSM are given in Table 6.2.

| rable 0.2. Cribbin design specifications |                                  |

|------------------------------------------|----------------------------------|

| Signal bandwidth                         | 20 Hz - 24 kHz                   |

| SNR/Dynamic Range                        | 108 dB                           |

| Quantizer fullscale                      | $3 V_{ppd}$                      |

| Technology                               | $0.18\mu\mathrm{m}\mathrm{CMOS}$ |

| Supply voltage                           | 1.8 V                            |

Table 6.2: CTDSM design specifications

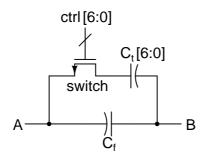

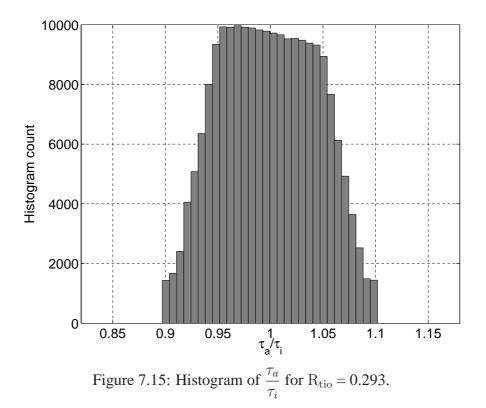

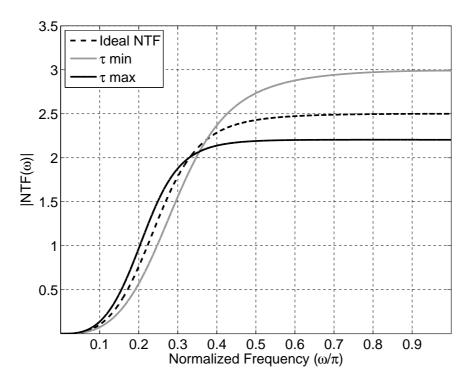

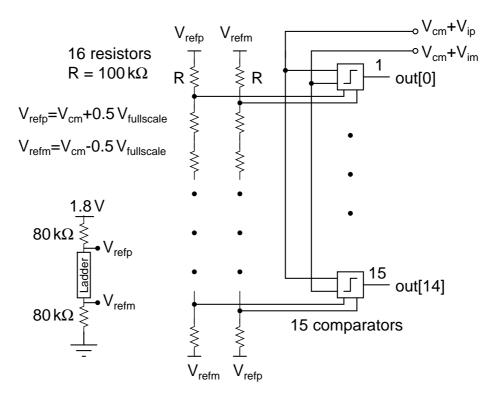

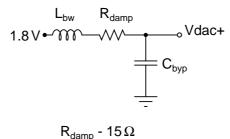

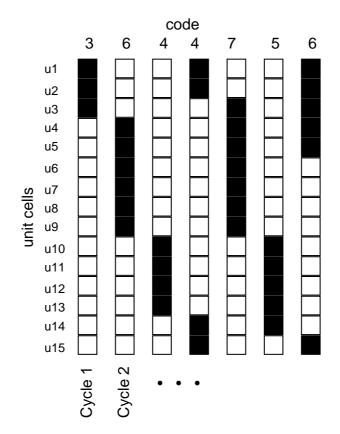

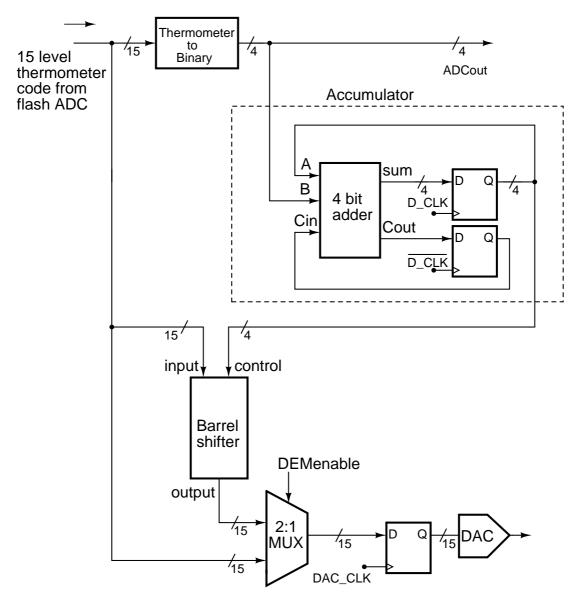

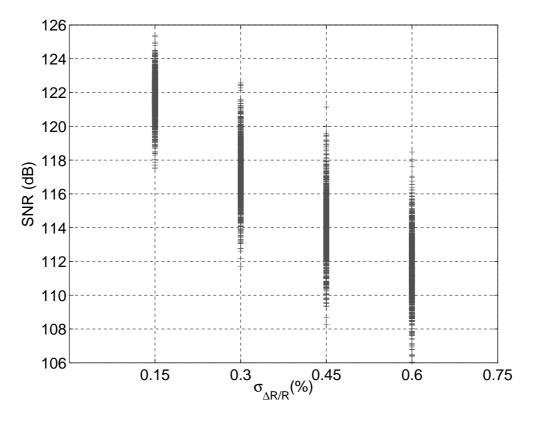

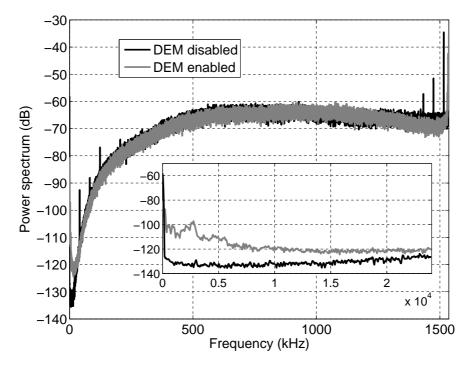

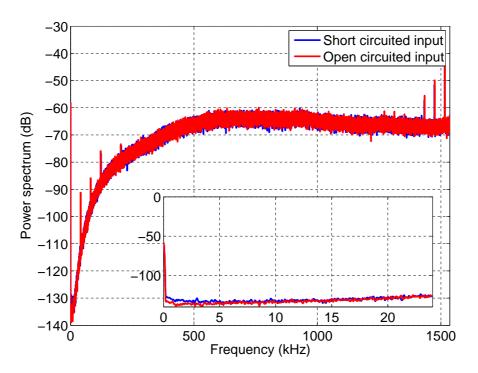

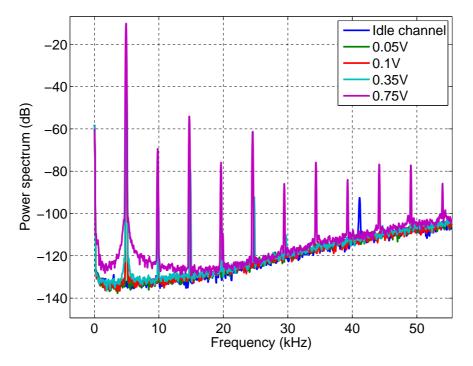

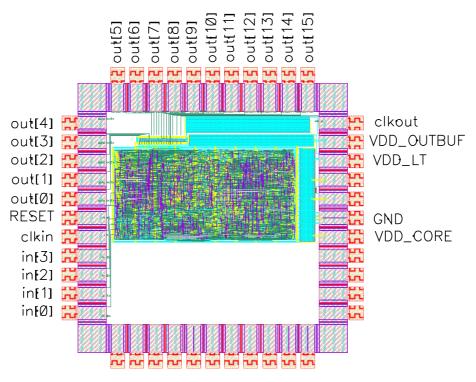

# 6.3 Nonidealities in a CTDSM