# Design of a Low Power Class-D Amplifier for Hearing Aids

A THESIS

submitted by

#### AMRITH SUKUMARAN

for the award of the degree

of

#### MASTER OF SCIENCE

(by Research)

**CERTIFICATE**

This is to certify that the thesis titled Design of a Low Power Class-D Am-

plifier for Hearing Aids, submitted by Amrith Sukumaran, to the Indian

Institute of Technology Madras, for the award of the degree of Master of Sci-

ence, is a bonafide record of the work done by him under my supervision. The

contents of this thesis, in full or in parts, have not been submitted to any other

Institute or University for the award of any degree or diploma.

Dr. Y. Shanthi Pavan

Research Advisor,

Professor,

Dept. of Electrical Engineering,

IIT-Madras,

Chennai 600 036

Place: Chennai

Date:

#### ACKNOWLEDGEMENTS

I would like to thank my research advisor, Dr. Shanthi Pavan for giving me this wonderful opportunity to work on this project. His suggestions were sound and timely, which ensured the smooth progress of this work. His technical expertise proved very useful both for this project and to help strengthen my understanding of circuits and systems. The basics of sigma delta converters that I had learnt from his class was very useful. Above all, I am extremely grateful to him for the confidence he had on me.

I would like to thank Dr.Krishna Vasudevan for his class on Power converters analysis and design. The basics learnt from this class made me always feel at ease with the concepts of switched mode conversion which was vital for this work. The innumerous after-class technical discussions I had with him were invaluable and will be remembered for a long time to come. I would like to thank Dr. Nagendra Krishnapura for the technical discussions I had with him and the useful suggestions he provided during testing. I would also like to thank Dr. Vinita Vasudevan, Dr. T. Natarajan and Dr. Babu Viswanathan for serving on my GTC panel.

Among my lab mates, I thank Prabhu shankar for introducing me to the basics of Delta Sigma converters. The innumerous discussions I had with him and the lunch-time chats will be cherished for a long time to come. I thank Pradeep Krishna for the technical and non-technical discussions I have had with him. The infinite number of brainstorms we had right from circuits to stock markets were really enlightening and will be remembered for a long time to come. Pradeep and Prabhu made my stay here a really memorable one. I am grateful to Kunal Karanjkar who designed the frontend portion of this chip. His cooperation enabled

a quick tape out of the design and his timely help during tape out and testing proved really valuable.

I thank Shankar Parameshwaran for having introduced me to digital IC design flow and for ensuring smooth network facilities in TI lab, Hariharan for teaching me how to fuse codes in FPGA and Vallabh for helping me with board design. I would also like to extend my thanks to Vikas Singh and I Rajesh. I would also like to thank Ankesh Jain, S.Radha, A.B.Karthikeyan, Nagarajesh, Debashish, Sumit, Ganpath, Vikram, Komail, Sreelakshmi, Paresh Jain and all others who had helped me either directly or indirectly. I extend my thanks to the EE office and administrative staff of our department, especially Mrs. Sumathi, Mrs. Janaki and Mr. Sarnath for the timely help in sorting out the administrative issues and for helping in purchasing the components. My sincere thanks also goes to the DIT(India) for funding this project.

Last but not the least, it was the unconditional love and support from my parents that had made this work possible. I dedicate this thesis to my grandmother D.Kamala who was with me to encourage me during my downs and motivated me to do still better. I also dedicate this thesis to my grandfather K.V.Devanathan, my mother Sujatha and my sister Aashritha. They have waited far too long for this moment.

#### ABSTRACT

Ipods, mobile phones, computers and scores of modern gadgets store data digitally. Here, core analog information such as video and audio are encoded in digital bits. Personal assistant devices such as hearing aids is another example where the analog audio is encoded digitally. Encoding audio digitally makes signal processing and conditioning easy. There are a number of powerful Digital Signal Processors(DSP) available in the market that can process digital signals accurately and reliably. This digitally processed data must then be converted back into analog sound waves for human reception. This work deals with the design of the digital to analog converter for a digital hearing aid.

The primary difficulty in converting high resolution (sixteen bits and greater) digital signals into analog is in maintaining the quality of the signal. The converter must not distort the signal and must not add it's own noise. The most important requirement for all portable and body worn devices is battery life. Therefore, the digital to analog converter should be highly efficient to extend the battery life and also to avoid frequent recharging of the batteries. The concept of class-D amplification comes as a natural choice where high efficiency is required. The design and implementation of digital input class-D amplifiers has been discussed in detail in this work. The advantages and disadvantages of various digital input class-D topologies have also been detailed out. It is seen that direct conversion of high resolution digital to analog is wasteful of power and degrades signal quality and hence a two step approach has been adopted. The first step is to convert the high resolution digital input into a 1 bit digital signal. In the second step, this digital signal is converted into analog. The various problems associated with using the digital output to directly drive the speaker are that of insufficient supply regula-

tion and other driver non-idealities. It is seen that adopting a negative feedback loop around the class-D driver stage mitigates all the above mentioned problems to a great extent. Yet another problem is the effect of clock jitter at the digital to analog interface. This is a critical problem and has been suppressed by adopting a Finite Impulse Response DAC(FIR-DAC). The design and implementation of the FIR-DAC has been detailed out in this thesis. The dominant source of nonlinearity in closed loop class-D driver stages and ways of improving the linearity using the assisted opamp technique has also been discussed. The design of comparator with inbuilt non overlap generator has also been proposed.

Miscellaneous blocks such as Serial Peripheral Interface(SPI), Bandgap Voltage reference and Low Battery Monitor(LBM) has been discussed. A test board has been designed to aid the testing of the chip. The issues that are to be considered while designing a test board for this sort of an application has been discussed briefly. The thesis concludes with measurement results.

# TABLE OF CONTENTS

| $\mathbf{A}$ | CKN  | OWLEDGEMENTS                       | ii |

|--------------|------|------------------------------------|----|

| $\mathbf{A}$ | BST] | RACT                               | iv |

|              | LIS  | T OF TABLES                        | ix |

|              | LIS  | T OF FIGURES                       | x  |

| $\mathbf{A}$ | BBR  | EVIATIONS                          | XV |

| 1            | Intr | roduction                          | 1  |

|              | 1.1  | Motivation                         | 1  |

|              | 1.2  | Design objective                   | 3  |

|              | 1.3  | Basics of class-D operation        | 3  |

|              | 1.4  | Class-D amplifiers in hearing aids | 5  |

|              | 1.5  | Thesis organization                | 6  |

| 2            | Dig  | ital Input Class-D Amplifiers      | 8  |

|              | 2.1  | Choice of architecture             | 8  |

|              |      | 2.1.1 Delta Sigma approach         | 8  |

|              |      | 2.1.2 PWM approach                 | 10 |

|              | 2.2  | Implementation                     | 13 |

|   |     | 2.2.1    | Cross-point deriver                                         | 13 |

|---|-----|----------|-------------------------------------------------------------|----|

|   |     | 2.2.2    | Digital Delta Sigma modulator                               | 17 |

|   |     | 2.2.3    | Interpolator                                                | 21 |

|   |     | 2.2.4    | UPWM                                                        | 25 |

|   |     | 2.2.5    | Performance summary                                         | 26 |

| 3 | Ana | alog se  | ction of class-D amplifier                                  | 28 |

|   | 3.1 | Introd   | luction                                                     | 28 |

|   | 3.2 | Target   | t specifications                                            | 30 |

|   | 3.3 | Loop     | filter Design                                               | 31 |

|   |     | 3.3.1    | Finite Impulse Response DAC (FIR-DAC)                       | 39 |

|   |     | 3.3.2    | Improving linearity of first integrator- the assisted opamp |    |

|   |     |          | technique                                                   | 46 |

|   |     | 3.3.3    | Transconductor-Amplifier(TA) design                         | 50 |

|   | 3.4 | Comp     | arator                                                      | 54 |

|   |     | 3.4.1    | Comparator as a dead-time generator                         | 55 |

|   | 3.5 | Buffer   | and H-Bridge driver                                         | 58 |

|   | 3.6 | Perfor   | mance summary                                               | 60 |

| 4 | Mis | scellane | eous Blocks and Layout                                      | 62 |

|   | 4.1 | Serial   | Peripheral Interface- SPI                                   | 62 |

|   | 4.2 | Low E    | Battery Monitor (LBM)                                       | 64 |

|   | 4.3 | Bandg    | gap Voltage Reference                                       | 67 |

|              | 4.4   | On-chip Master current generator and distributor   | 72         |

|--------------|-------|----------------------------------------------------|------------|

|              | 4.5   | Chip Floorplan and Layout                          | 73         |

| 5            | Test  | ting and Measurement Results                       | <b>7</b> 6 |

|              | 5.1   | Board Design                                       | 76         |

|              | 5.2   | Measurement results                                | 78         |

|              |       | 5.2.1 16-bit digital to 1-bit digital converter    | 78         |

|              |       | 5.2.2 Analog class-D amplifier                     | 79         |

| 6            | Con   | nclusion                                           | 82         |

| $\mathbf{A}$ | Effic | ciency degradation in practical class-D amplifiers | 84         |

| В            | Nor   | nlinearity in UPWM                                 | 86         |

| $\mathbf{C}$ | Line  | earized, Low-frequency model of PWM block          | 87         |

| D            | Priı  | nted Circuit Board(PCB) schematic                  | 89         |

# LIST OF TABLES

| 2.1 | Design specifications for the class-D backend driver section       | 13 |

|-----|--------------------------------------------------------------------|----|

| 2.2 | Performance summary of the digital section of the class-D backend  |    |

|     | driver                                                             | 27 |

| 3.1 | Target specifications for the analog section of the class-D driver | 31 |

| 3.2 | Performance comparison with reported designs                       | 61 |

# LIST OF FIGURES

| 1.1  | Principle of Class-D amplification                                                 | ]  |

|------|------------------------------------------------------------------------------------|----|

| 1.2  | Digital hearing aid                                                                | 2  |

| 1.3  | (a)Single-ended PWM coding, (b)Differential PWM coding                             | ٩  |

| 1.4  | Class-D amplification- Principle of operation                                      | 4  |

| 1.5  | Class-D amplification- Speaker load                                                | ٢  |

| 1.6  | Digital input digital output DSM and Delta Sigma DAC                               | 6  |

| 2.1  | Direct Delta Sigma modulation                                                      | Ć  |

| 2.2  | Two stage approach- Delta sigma modulation + Analog PWM modulation                 | ć  |

| 2.3  | Direct PWM modulation                                                              | 11 |

| 2.4  | Hybrid approach- Essentially PWM modulation                                        | 11 |

| 2.5  | Hybrid approach- Approximating NPWM modulation                                     | 12 |

| 2.6  | (a)Leading edge modulation, (b)Trailing edge modulation, (c)Double-edge modulation | 14 |

| 2.7  | PSD of ideal NADS modulation                                                       | 15 |

| 2.8  | Cross-point deriver- Estimating naturally sampled points                           | 15 |

| 2.9  | Digital Delta-Sigma modulator                                                      | 17 |

| 2.10 | Error feedback digital Delta Sigma modulator                                       | 18 |

| 2.11 | Allowed word lengths for stable operation                           |    |  |

|------|---------------------------------------------------------------------|----|--|

| 2.12 | Matching IIR-NTF with FIR-NTF                                       |    |  |

| 2.13 | Architecture of the FIR loop filter                                 |    |  |

| 2.14 | Overall architecture of digital Delta Sigma modulator               | 21 |  |

| 2.15 | Interpolation filter and the explicit low pass FIR filter           | 23 |  |

| 2.16 | Operation of repeating the same value at a higher rate              | 23 |  |

| 2.17 | Frequency response of the inherent filtering                        | 24 |  |

| 2.18 | Overall frequency response of the interpolator (320 kHz corresponds |    |  |

|      | to $\frac{f_s}{2}$ )                                                | 25 |  |

| 2.19 | PSD of the signals at the output of various blocks                  | 26 |  |

| 2.20 | Amplitude sweep                                                     | 27 |  |

| 3.1  | Clock jitter modulating with data and raising the inband            | 29 |  |

| 3.2  | Architecture of closed-loop Class-D amplifier                       | 31 |  |

| 3.3  | Second order closed-loop Class-D amplifier                          | 32 |  |

| 3.4  | Second order closed-loop Class-D amplifier with triangular carrier  |    |  |

|      | generator                                                           | 33 |  |

| 3.5  | Ripple stability criteria being violated                            | 34 |  |

| 3.6  | Waveforms at required nodes for calculating stability requirements. | 35 |  |

| 3.7  | Linearized Class-D loop                                             | 36 |  |

| 3.8  | Closed loop class-D amplifier with component values indicated       | 39 |  |

| 3.9  | Magnitude and phase response of the Class-D loop                    |    |  |

| 3.10 | Architecture of a 4-tap FIR-DAC                                     | 40 |  |

| 3.11 | Jitter cancelling mechanism in FIR-DAC                       |    |  |

|------|--------------------------------------------------------------|----|--|

| 3.12 | Jitter sensitivity comparison                                | 13 |  |

| 3.13 | Schematic of a 10-tap differential FIR-DAC                   |    |  |

| 3.14 | Schematic of unit delay block- D flip-flop                   | 15 |  |

| 3.15 | The assisted opamp technique                                 | 17 |  |

| 3.16 | Implementation of the assisted opamp technique               | 18 |  |

| 3.17 | Assistant for the feedback current                           | 19 |  |

| 3.18 | Assistant for the input FIR-DAC current                      | 50 |  |

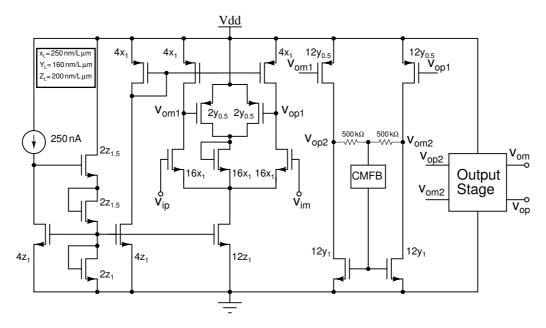

| 3.19 | Schematic of TA of first integrator                          | 51 |  |

| 3.20 | Principle of feedforward compensation                        | 51 |  |

| 3.21 | Schematic of the CMFB amplifier                              | 52 |  |

| 3.22 | Magnitude and phase response of the transconductor-amplifier | 53 |  |

| 3.23 | Schematic of TA of second integrator                         | 53 |  |

| 3.24 | Schematic of comparator                                      | 55 |  |

| 3.25 | Schematic of output stage                                    | 55 |  |

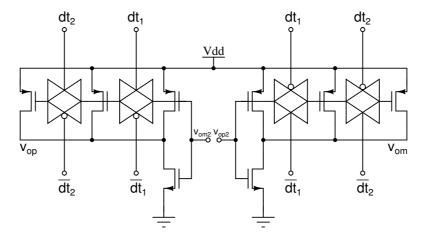

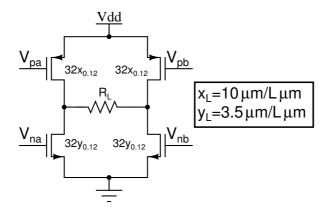

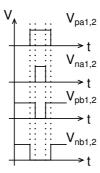

| 3.26 | H-Bridge with non-overlapping data inputs                    | 56 |  |

| 3.27 | Mechanism of dead-time generation                            | 56 |  |

| 3.28 | Tuning the dead-time                                         | 58 |  |

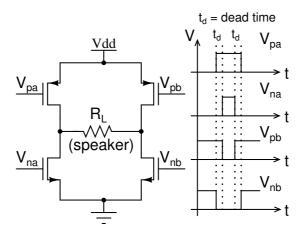

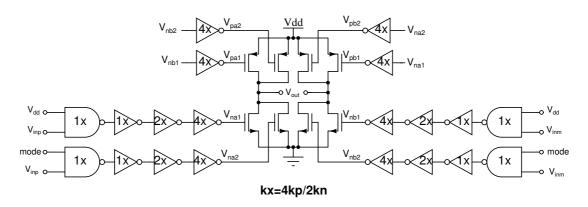

| 3.29 | H-Bridge driver                                              | 59 |  |

| 3.30 | Driving the H-Bridge                                         | 59 |  |

| 3.31 | The timings for meeting non-overlap requirements             | 59 |  |

| 3.32 | Frequency response of second order LC low pass filter        | 3O |  |

| 3.33 | PSD at the output of Class-D loop                              | 61 |

|------|----------------------------------------------------------------|----|

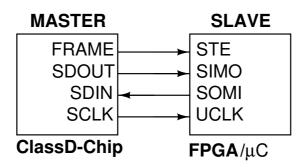

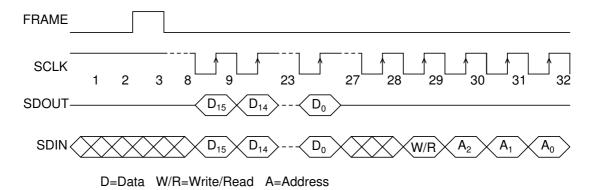

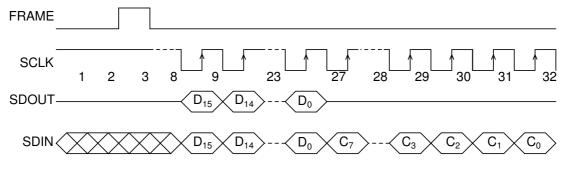

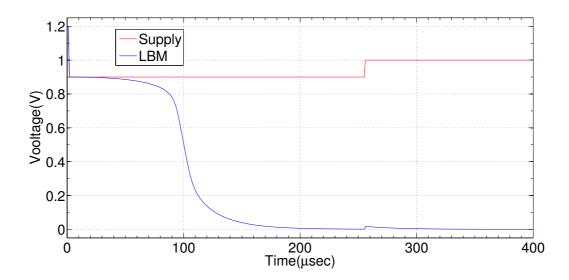

| 4.1  | SPI protocol- Master Slave communication                       | 62 |

| 4.2  | Address frame                                                  | 63 |

| 4.3  | Control word frame                                             | 63 |

| 4.4  | Read frame                                                     | 64 |

| 4.5  | Low battery monitor                                            | 65 |

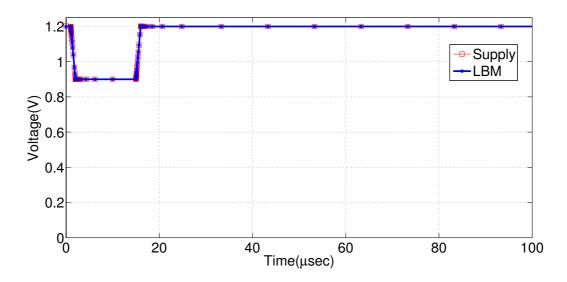

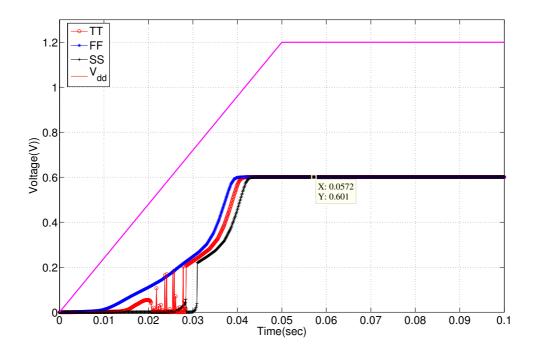

| 4.6  | Low-battery indication                                         | 66 |

| 4.7  | Normal operation                                               | 66 |

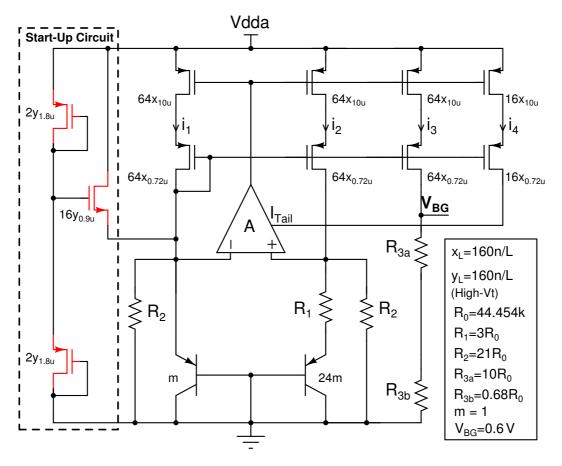

| 4.8  | Fractional Bandgap voltage reference                           | 67 |

| 4.9  | Amplifier used in bandgap                                      | 69 |

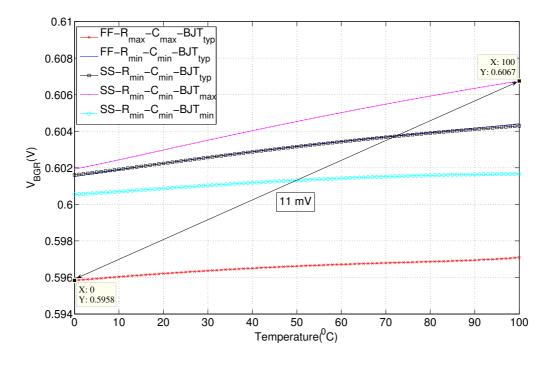

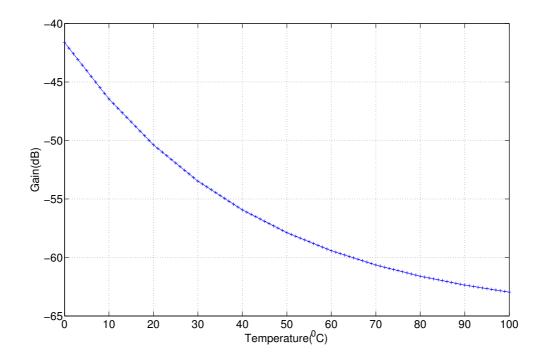

| 4.10 | Temperature dependence of Bandgap output                       | 70 |

| 4.11 | PSRR of Bandgap output                                         | 71 |

| 4.12 | Starting up the bandgap                                        | 71 |

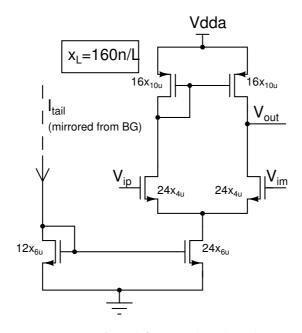

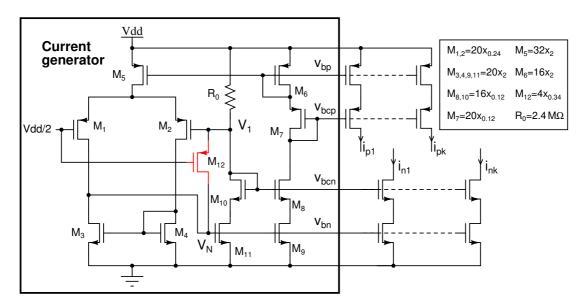

| 4.13 | Master current source                                          | 72 |

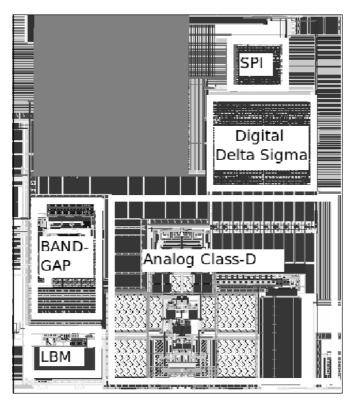

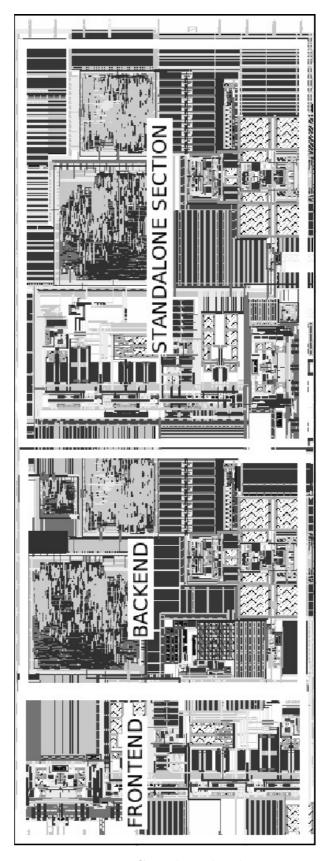

| 4.14 | Layout of the entire backend                                   | 74 |

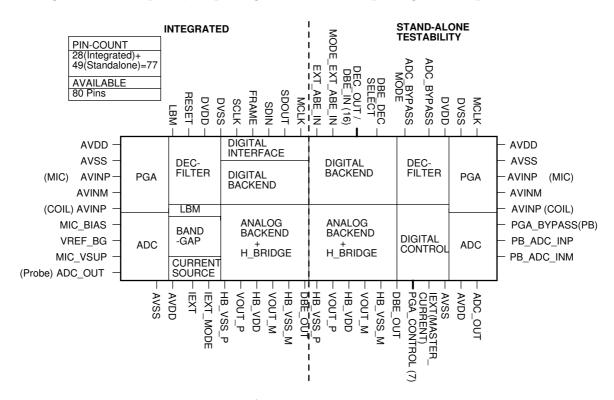

| 4.15 | Floorplan of the entire chip with pin-out details              | 74 |

| 4.16 | Complete chip layout                                           | 75 |

| 5.1  | Snapshot of the board                                          | 77 |

| 5.2  | Snapshot of the Measurement setup                              | 78 |

| 5.3  | Measurement setup for measuring performance of digital class-D |    |

|      | section                                                        | 78 |

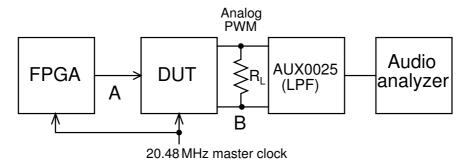

| 5.4  | Measured PSD of the digital output                             | 79 |

| 5.5 | Amplitude sweep measurements                                  | 76 |

|-----|---------------------------------------------------------------|----|

| 5.6 | Measurement setup for measuring performance of analog class-D |    |

|     | section                                                       | 80 |

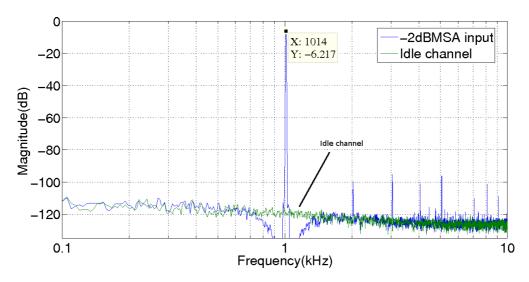

| 5.7 | PSD of the filtered analog PWM signal                         | 80 |

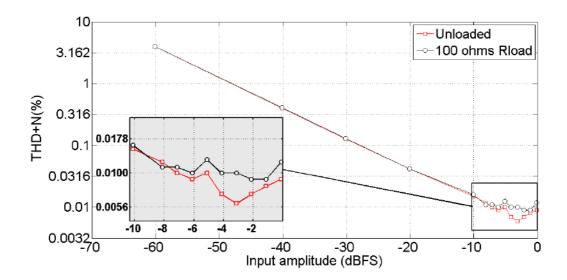

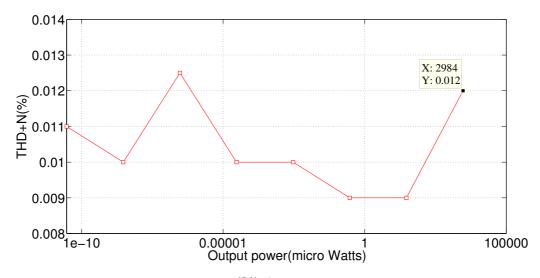

| 5.8 | THD+N(%) for various input amplitudes                         | 81 |

| 5.9 | THD+N(%) for various output powers                            | 81 |

| A.1 | Parasitics in class-D driver stage                            | 84 |

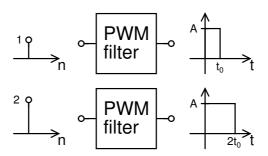

| B.1 | Impulse response of a PWM filter                              | 86 |

| C.1 | Linearizing the PWM block                                     | 87 |

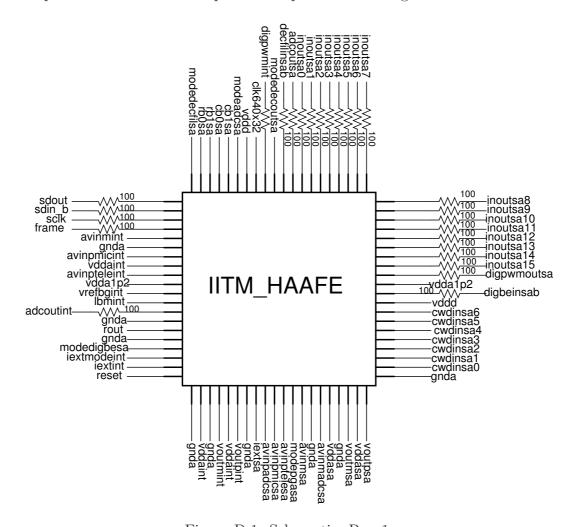

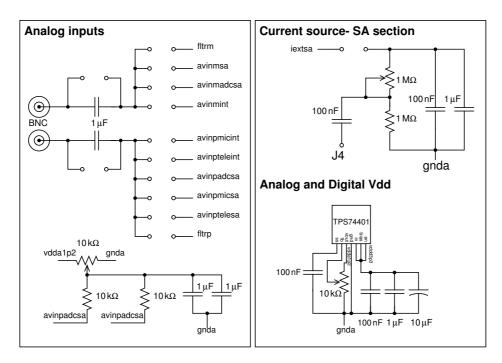

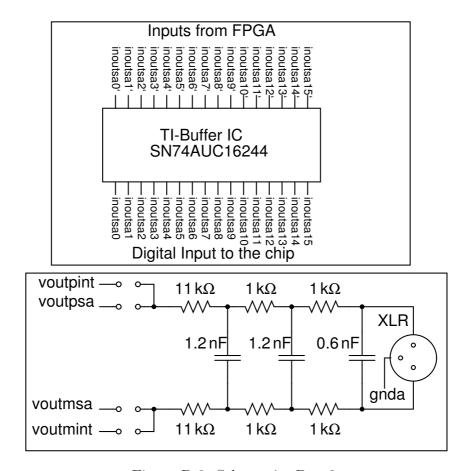

| D.1 | Schematic- Page1                                              | 89 |

| D.2 | Schematic- Page2                                              | 90 |

| D 3 | Schematic- Page3                                              | 90 |

#### **ABBREVIATIONS**

ADC Analog to Digital Converter

**BGR** Bandgap Reference

CMFB Common Mode Feedback

DAC Digital to Analog Converter

**DSM** Delta Sigma Modulator

**DSP** Digital Signal Processor

FIR Finite Impulse Response

MSA Maximum Stable Amplitude

**NPWM** Natural Pulse Width Modulation

NTF Noise Transfer Function

**OBG** Out of Band Gain

**OSR** Oversampling Ratio

PGA Programmable Gain Amplifier

**PSD** Power Spectral Density

PVT Process Voltage Temperature

**PWM** Pulse Width Modulation

**SNDR** Signal to Noise and Distortion Ratio

SPI Serial Peripheral Interface

STF Signal Transfer Function

**THD** Total Harmonic Distortion

UGB Unity Gain Bandwidth

**UPWM** Uniform Pulse Width Modulation

### CHAPTER 1

#### Introduction

# 1.1 Motivation

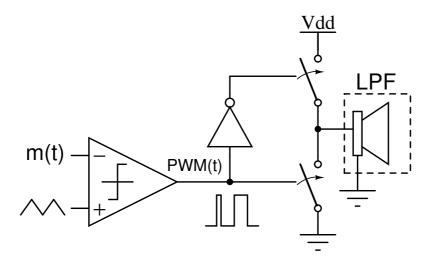

Figure 1.1: Principle of Class-D amplification.

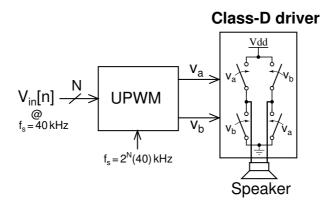

The idea of class-D amplification was proposed more than fifty years ago. The idea is to encode the amplitude information in pulse widths by a coding scheme called pulse width modulation(PWM). The PWM signal is represented using only two amplitude levels and a switch arrangement as shown in Fig.1.1 is used to drive the speaker load. Class-D amplification is still a widely researched topic. The property that makes class-D amplification extremely attractive is efficiency. It is theoretically 100% efficient. This property has made it a formidable competitor to the traditional class-AB audio amplifiers. Distortion and MOSFET technology had been the primary bottlenecks which had restricted class-D amplifiers till the last two decades from making deep inroads into the high-end audio market. With advancements in transistor technology, switches were capable of operating at higher speeds and offered more reliability and these properties proved extremely

favorable for class-D operation. The linearity problem in class-D has also been addressed widely over the past two decades. Solutions range from adopting careful open loop design practices, adopting negative feedback. Since class-D amplifiers are highly efficient it has now become the preffered choice for portable audio. They generate lesser heat than traditional class-A or class-AB amplifiers. This avoids heat sinks almost completely and has led to reduction in size and weight. Another advantage is in its demodulation. The demodulator is just a conventional low pass filter. [1] gives a good overview of the applications where class-D amplifiers have been employed.

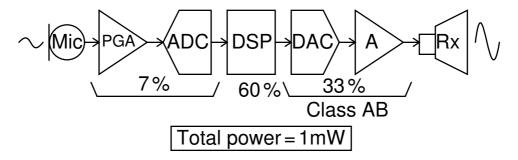

An important area where class-D amplifiers are dominating are in hearing aids. The basic components of a modern hearing aid is shown in Fig.1.2. The typical power budgetting in a state of the art digital hearing aid is shown in Fig.1.2[2]. Signal processing requirements will be increasing further in future hearing aids which implies that the DSP would be working at higher power levels. However on the other hand, the overall power consumption cannot be increased further, else the battery life would come down drastically. Therefore, the power consumed by other blocks need to be reduced. Taking the signal chain in Fig.1.2 as a specific example, it can be seen that the backend driver consumes about 33% of the total system's power of 1 mW. By adopting a class-D driver stage for the backend, the power consumption can be easily brought down to less than 10% of the total power. This would enable us to allocate higher power to the DSP for providing advanced functionalities.

Figure 1.2: Digital hearing aid.

# 1.2 Design objective

The main objective of this work was to design and fabricate the backend section of a digital hearing aid. A class-D backend driver stage was designed for this purpose. The specifications targetted was in accordance with a commercial product-AIC111. It is a hearing aid chip designed by Texas Instruments.

## 1.3 Basics of class-D operation

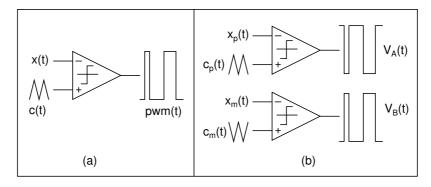

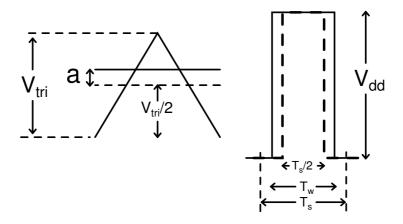

The efficiency advantage of class-D amplifiers is mainly due to the way the signal is encoded. The audio signal which is continuous in amplitude and time can be encoded into pulse widths by comparing it with a relatively higher frequency carrier waveform[3]. The implementation of this coding is shown in Fig.1.3. The output pwm(t) is a two level signal containing the required audio information in its pulse widths.

Figure 1.3: (a)Single-ended PWM coding, (b)Differential PWM coding.

This two level differential signal is given to the structure in Fig.1.4.

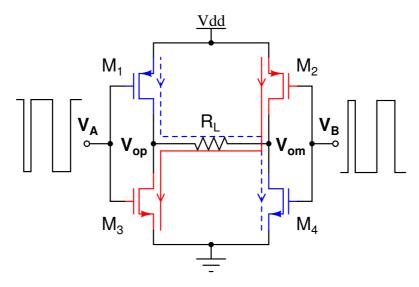

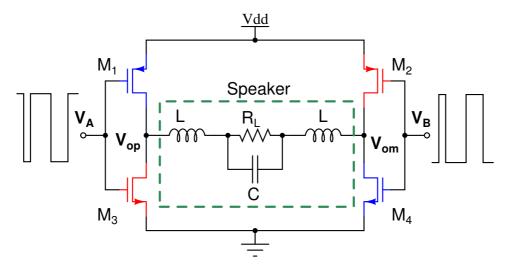

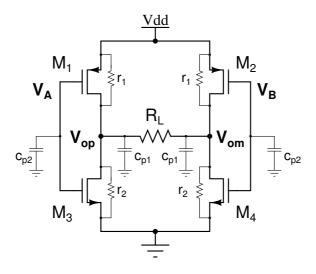

Let  $R_L$  represent the speaker load. When  $V_A$  is high,  $V_B$  is low and  $M_3$  and  $M_2$  are switched on. This causes the load current to flow from  $V_{om}$  to  $V_{op}$ . During this state the voltage across  $M_3$  and  $M_2$  is zero and the current through them is  $\frac{V_{dd}}{R_L}$ . During the state when  $V_A$  is low,  $M_1$  and  $M_4$  are on, causing the load current to flow from  $V_{op}$  to  $V_{om}$ . During this state the voltage across  $M_1$  and  $M_4$

Figure 1.4: Class-D amplification- Principle of operation.

is zero and the current through them is  $\frac{V_{dd}}{R_L}$ . Therefore at any instant, either the voltage across a pair of transistors are zero or the current through them is zero. This implies that no power is dissipated by the transistors and therefore all the power taken from the supply is transferred to the load resulting in a theoretically hundred percent efficiency.

An advantageous property of the class-D technique is its very simple demodulation. Eventhough the audio information is encoded in pulse widths, recovering the information back is as simple as low pass filtering the PWM waveform. Therefore, the demodulator is just a low pass filter. In the case of speaker loads, the physical construction of the speaker can be electrically modelled as a low pass filter depicted in Fig.1.5 Apart from this low pass filtering, the human ear accounts for further low pass filtering, therefore an explicit low pass filter can be avoided. These properties have made class-D amplifiers an ideal choice for ultra low power audio applications. However, one has also to give importance to practical issues that degrade efficiency in class-D amplifiers. These issues are discussed in Appendix. A.

Figure 1.5: Class-D amplification- Speaker load.

# 1.4 Class-D amplifiers in hearing aids

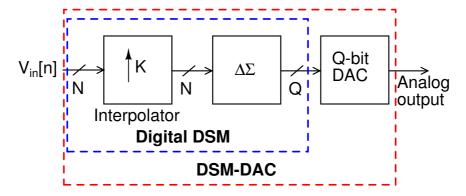

As already seen in chapter.1.1, digital hearing aids have a driver stage which can adopt the principle of class-D amplification. The DSP might output a 16-bit word stream or even a 24-bit word stream in the case of very high-end audio applications. The problem now is faithfully transforming the 16-bit/24-bit digital signal into analog without any increase in the noise floor and without distorting the input. For converting such high word lengths, it would be almost impossible with conventional Nyquist DACs due to the required component tolerances. Component trimming or other special techniques might be required to achieve good linearity with a considerable increase in the cost of fabrication. Typically for word lengths greater than 12 bits, oversampling digital to analog converters are used. Here, the quantization error noise floor is made to spread out in frequency while maintaining the overall quantization error power. In addition to that, the quantization error in the signal band is shaped out for further improvement in performance. This is finally followed by filtering off the high frequency contents outside the signal bandwidth. The system which performs the above operations is popularly called as Delta Sigma converters or Delta Sigma Modulators (DSM). Delta Sigma converters which accept digital inputs and provide digital outputs are called digital to digital Delta Sigma converters. Those that accept digital inputs and provide analog outputs are called Delta Sigma DACs(Fig.1.6).

Figure 1.6: Digital input digital output DSM and Delta Sigma DAC.

Both these types of systems are used in digital hearing aids. In hearing aids which has a digital to digital delta sigma, the digital output is converted into analog by means of a conventional Nyquist DAC and then converted into PWM waveform for achieving high efficiency. The advantages and disadvantages of the above techniques are discussed in Chapter.2. This thesis focuses on the analysis, design and measurement of a class-D amplifier for hearing aids.

# 1.5 Thesis organization

The rest of the thesis is organized as follows;

Chapter 2 discusses how a sixteen bit digital input signal can be converted into a single bit digital signal without distorting the signal.

Chapter 3 discusses why using the above signal directly to drive the speakers is disadvantageous. Further, design of a closed loop driver stage has been proposed as a solution to overcome the disadvantages of directly driving the speakers.

Chapter 4 discusses about other blocks like Serial Peripheral Interface (SPI), Bandgap

Reference(BGR), Low Battery Monitor(LBM) and on-chip current generator. It also discusses chip layout.

Chapter 5 deals with board design, testing and measurement results.

Chapter 6 concludes the thesis and puts forth possible improvements to the existing design.

#### CHAPTER 2

# Digital Input Class-D Amplifiers

#### 2.1 Choice of architecture

In a digital hearing aid, the class-D driver must accept a high resolution(say 16 bits) digital input word that must drive the speakers. Implementation of Nyquist DACs for resolutions greater than 16 bits becomes very non-economical. Practical issues like component mismatches come into picture that makes trimming of elements a must. Therefore, other methods have to be adopted to achieve this digital to analog conversion. A commonly used approach is to convert the higher bit digital signal into a lower bit one and then employ a conventional Nyquist DAC. An important requirement for these DACs is that the output signal must be a 1-bit signal so that the principle of class-D amplification can be employed. This chapter discusses in detail as to how this connversion can be achieved.

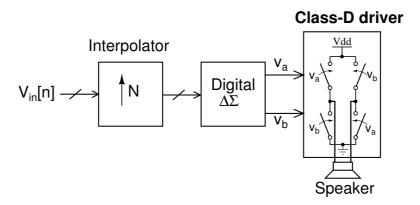

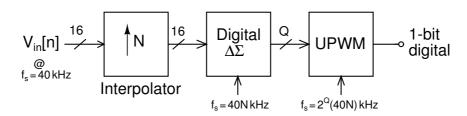

## 2.1.1 Delta Sigma approach

Here the principles of oversampling and noise shaping is used to encode sixteen bits of information in just one bit. The sixteen bit input word is interpolated and fed into a digital delta sigma modulator as shown in Fig.2.1. This 1-bit signal can be used to drive the H-Bridge which further drives the speakers. This method is popularly known as digital input delta-sigma class-D amplifiers[4].

However this approach suffers from the following disadvantages;

Requires a high carrier frequency to yield the required performance. This

leads to a high average switching frequency and thus leads to efficiency

degradation.

Figure 2.1: Direct Delta Sigma modulation.

- Relatively low maximum stable input amplitude that can be applied to the system. Reduces dynamic range.

- Modulation of clock-jitter and supply noise with data. This will cause an increase in the inband noise floor.

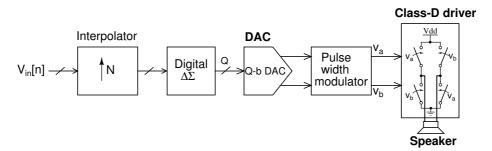

The high average switching frequency can be reduced by using a bit-flipping technique as described in [4]. Another approach is to convert the sixteen bit digital word into an intermediate bit-width using delta-sigma modulation[5]. This is followed by a conventional multi-bit Nyquist DAC. However, the conversion does not stop here. This analog signal should be then encoded into pulse widths to be able to use the concept of class-D amplification. This PWM signal is then used to drive the speakers through a H-Bridge. This technique is illustrated in Fig.2.2.

Figure 2.2: Two stage approach- Delta sigma modulation + Analog PWM modulation.

To achieve the same performance, this method requires a lower carrier frequency. This will decrease the average switching frequency and hence the switching losses in the driver stage. This improves the system efficiency. Another benefit is that the maximum stable input amplitude is also higher than that in the previous

method. The above benefits are due to the fact that the quantization noise has been considerably reduced. However, to adopt the principle of class-D amplification one must initially convert the analog signal into a PWM signal. Pulse width modulation can be done by comparing the analog signal with a triangular or a sawtooth carrier. The PWM signal is then given to the H-Bridge which drives the speakers.

Even this approach suffers from quite a few disadvantages;

- The thermal noise and linearity of the multibit-DAC determines the overall dynamic range and linearity of the system respectively.

- Multi-bit DAC requires higher power to satisfy dynamic range and linearity requirements and thus reduces the overall system efficiency.

- To avoid aliasing, the carrier frequency used in the PWM modulator must be greater than the digital DSM's clock frequency. To mitigate this problem an anti-aliasing low-pass filter must be used before the PWM modulator. Again, the linearity and the noise introduced by this filter will be a problem.

- The other non-linearities associated with the PWM generation will also affect the performance of the system.

There are another class of converters which uses pulse width modulation and are described next.

# 2.1.2 PWM approach

Theoretically, the sixteen bit digital input signal can be mapped to  $2^{16}$  pulse widths. This process of mapping a discrete-time input into pulse widths is known as UPWM- Uniform pulse width modulation. The resulting PWM waveform can be given as input to H-Bridge which then drives the speakers as illustrated in Fig.2.3. Though the idea is simple, there are practical difficulties in its implementation. If the 16-bit digital input comes at a rate of, say  $40\,\mathrm{kHz}$ , then the clock required for UPWM conversion would be  $2^{16}\cdot40\,\mathrm{kHz}$ , i.e.  $2.56\,\mathrm{GHz}$ . Clocks of this frequency are difficult to generate and would cause the PWM generator block to

consume considerable power. Another disadvantage with the above approach is the inherent non-linearity in direct PCM to PWM conversion. In other words, UPWM is a non-linear modulation scheme[6].

Figure 2.3: Direct PWM modulation.

An elegant approach has been proposed [7, 8] to address the problems encountered by the above system. The idea is to reduce the word length of the input signal (to say, Q) by using delta sigma modulation and then performing UPWM modulation on this reduced word length. The advantage with this approach is that the operating frequency of the pulse generator block is drastically reduced. This system is shown in Fig.2.4. In short, the delta-sigma modulator helps to drastically reduce

Figure 2.4: Hybrid approach- Essentially PWM modulation.

the frequency of operation of the pulse generator block. However, there is one fundamental disadvantage associated with this system and that is non-linearity. The process of directly mapping a uniformly sampled signal into pulse widths(UPWM) is a non-linear operation in itself[6]. This operation leads to high levels of signal distortion. The distortion causing mechanism is described in Appendix. B. The solution to this problem is to mimic naturally-sampled PWM(NPWM).

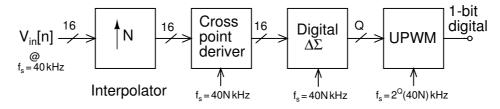

Natural PWM refers to the process of converting naturally sampled points into pulse widths. Naturally sampled points refer to those points that are got as the intersection between an equivalent analog signal and an analog carrier. From a different perspective, the naturally sampled points can lie anywhere in the amplitudetime plane. The reason that one strives to approach towards NPWM is that it does not give rise to base-band distortion[3], eventhough there can be harmonic/nonharmonic distortion due to the spilling of sidebands. However in digital systems, the sampling is uniform and the amplitude is quantized. Converting this type of a signal into pulse widths leads to direct base-band distortion. Therefore, the input signal must not be directly noise-shaped and converted into pulse widths. Instead, the cross points of the input signal with a sawtooth/triangular carrier (both hypothetically assumed to be continuous in time and amplitude) has to be estimated. This cross-point information can be given to a delta-sigma converter and then converted into pulse widths. This method essentially performs the NPWM operation. Therefore, it is also called Pseudo NPWM or algorithmic PWM[8]. This system is illustrated in Fig.2.5.

Figure 2.5: Hybrid approach- Approximating NPWM modulation.

The PWM-based approach has several advantages when compared with the deltasigma-based approach.

- The pulse repetition frequency is lower.

- The achievable dynamic range is higher. (Larger amplitude inputs can be applied without causing stability issues)

- If the cross-points are accurately calculated, the PWM-approach would theoretically be extremely linear, since it approaches NPWM.

- The output of the pulse generator block is always one bit in amplitude and thereby lends itself directly to class-D amplification.

Considering the advantages of the PWM-approach, the system in Fig.2.5 has been adopted for this work.

# 2.2 Implementation

The targeted performance is shown in Table 2.1

Table 2.1: Design specifications for the class-D backend driver section

| Signal bandwidth | 100 Hz to 10 kHz        |  |

|------------------|-------------------------|--|

| Input bit-width  | 16 bits at 40 kHz       |  |

| SNR              | >96 dB                  |  |

| THD              | better than -85 dB      |  |

| Supply voltage   | 1.2 V                   |  |

| Technology       | 130 nm standard process |  |

The design of each block of Fig.2.5 is described in detail in the following subsections.

## 2.2.1 Cross-point deriver

The reason cross-point deriver is being discussed first is that the PWM modulation scheme is decided at this stage. Depending on the modulation scheme, the sampling frequency of the delta-sigma converter would be fixed. System-wise, the interpolator and the delta-sigma modulator comprise closely related blocks and would be discussed together. However, it is to be kept in mind that the input to this block is the output of the interpolator.

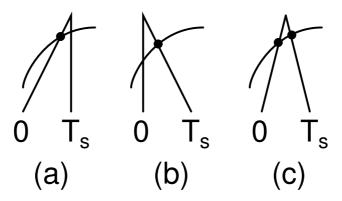

The main aim of the cross-point deriver block is to estimate what would have been the cross-points if a continuous-time version of the input signal was compared with a continuous-time carrier. An important design parameter to be chosen here is the type of carrier that is to be assumed. The carrier waveform can either be leading-edge or trailing-edge sawtooth(NADS) or a triangular waveform(NADD) as shown in Fig.2.6.

Figure 2.6: (a)Leading edge modulation, (b)Trailing edge modulation, (c)Double-edge modulation.

The benefit of double sided modulation is that the even components of the carrier and the intermodulation components cancel out [6]. However, now two crosspoints would be required for every pulse. Therefore, the pulse generator must employ two counters one for counting the delay and the other for generating the width[7]. Therefore, this scheme requires more hardware and is complicated in implementation. If the carrier is a sawtooth only one cross-point information is required for every pulse and thus the delay for the pulse to start would always be zero(in trailing edge modulation). This means that a single counter would be sufficient. It would be an up-counter if the modulation was trailing edge PWM and a down-counter if it was a leading edge modulation or vice versa depending on implementation. Therefore, single-sided, leading edge sawtooth was chosen as the carrier.

Now that the modulation scheme has been fixed, the next design parameter to choose is the carrier frequency. If the cross-point deriver block works exactly as required, then the modulation can be considered to be NPWM. Ideally, the output spectrum should look like that in Fig.2.7. The noise floor is limited by the simulation accuracy only.

From Fig.2.7 it can be seen that there is no base-band distortion but there are lot of side-bands for the carrier. If the carrier frequency is small, these sidebands can extend all the way down into the signal band. This could either lead to harmonic

Figure 2.7: PSD of ideal NADS modulation.

or non-harmonic distortion. From Fig.2.7, it is seen that at least 10 sidebands of the carrier are visible above the noise floor. Infact, taking more number points for calculating the PSD would reveal the buried harmonics. Therefore, there is a lower limit to the carrier frequency. In addition to the above, the cross-point deriver block would not be able to approach the NPWM cross-points precisely in practice. This would lead to direct signal-distortion. Another issue is that the carrier frequency has to be chosen such that the delta sigma modulator would be able to faithfully encode the cross-point information. Taking into account these practical issues, the carrier frequency has been fixed to be 64 times the signal band-edge frequency so that the design requirements are met.

The next step is to implement an algorithm that estimates the naturally sampled cross-points. The idea is illustrated in Fig.2.8.

Figure 2.8: Cross-point deriver- Estimating naturally sampled points.

Consider a single period of the carrier as shown in Fig.2.8. Let  $s_1$  and  $s_2$  be two adjacent samples of the digital message. Let tri(t) be the hypothetical continuous-time, leading-edged sawtooth carrier. If the hypothetical equivalent analog message is m(t), then the cross-point is  $Y_0$  as shown. Since the carrier frequency is many times higher than the message frequency, m(t) can be assumed to be piecewise linear within each carrier cycle. This gives;

$$m(t) = \frac{s_2 - s_1}{T_s} t + s_1 \tag{2.1}$$

and

$$tri(t) = \frac{2k}{T_s}t - k \tag{2.2}$$

Equating the above two gives the instant at which both curves meet. This instant is mapped into amplitude and the resulting solution can be calculated to be

$$Y_0 \approx \frac{k(s_1 + s_2)}{2k + s_1 - s_2} \tag{2.3}$$

The above equation has a division operator. In digital implementations, division operations are power hungry and would require extra hardware. Therefore, binomial theorem was applied to bring the denominator into the numerator. 2k can be taken out as a common factor and since  $\frac{s_1-s_2}{2k}$  is very small due to oversampling, the binomial approximation would be relatively accurate even with only the first order term. The final equation is

$$Y_0 \approx \frac{1}{4k}(s_1 + s_2)(2k - s_1 + s_2) \tag{2.4}$$

The above equation is coded in verilog and is synthesized using Design Vision. A point to note is that the word-length of each cross-point need not be higher than that of the interpolated digital input signal. In other words, the number of digital codes between any  $s_1$  and  $s_2$  is very large. Since the value of the cross-point will be somewhere between  $s_1$  and  $s_2$ , extra resolution need not be allocated for the

resultant cross-points.

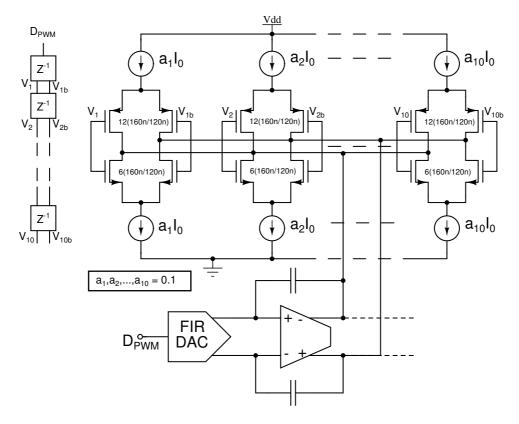

#### 2.2.2 Digital Delta Sigma modulator

Figure 2.9: Digital Delta-Sigma modulator.

The requirement of this block is to faithfully encode the sixteen bit cross-point information in a smaller number of bits. The oversampling ratio(OSR) for this modulator has already been fixed by choosing the carrier frequency of the sawtooth in the previous block. Therefore, the OSR is 32. Now, the design choices to be made are the number of quantizer bits and the order of the loop filter. It is a well known fact that the output of the delta sigma not only contains the cross-point information but also considerable high-frequency shaped quantization noise power. Therefore, both the signal and the high-frequency noise gets pulsewidth-modulated and would cause fold-back into the signal band. The amount of fold-back can be reduced by reducing the amount of high frequency content at the output of the DSM. This can be done by increasing the number of quantizer bits or reducing the out-of-band-gain (OBG). However, reducing the OBG would increase the in-band noise floor and thus degrade the accuracy with which the cross-points are encoded. Therefore the option is to choose a higher number of quantizer bits that would satisfy the requirements both in the signal band and in the highfrequency band. However, the number of bits in the quantizer must not be chosen too high, as it means the clock frequency required for pulse generator(UPWM) block would also be high. Considering these factors and through simulations it was decided to use a five bit quantizer for the DSM.

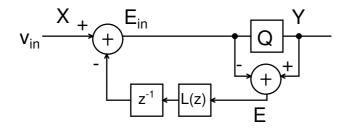

The architecture of the DSM is chosen to be of the error-feedback type as shown

in Fig.2.10.

Figure 2.10: Error feedback digital Delta Sigma modulator.

The advantage with this architecture is that if the noise transfer function(NTF) is FIR then the loop filter can also have an FIR structure. This fact can be confirmed from the below equations.

$$E_{in}(z) = X(z) - E(z)L(z)z^{-1}$$

(2.5)

$$E(z) = Y(z) - E_{in}(z) \tag{2.6}$$

$$Y(z) = E(z) + X(z) - E(z)L(z)z^{-1}$$

(2.7)

$$=X(z) + E(z)[1 - L(z)z^{-1}]$$

(2.8)

This equation is of the form

$$Y(z) = STF(z)X(z) + NTF(z)E(z)$$

(2.9)

Therefore,

$$STF = 1 \tag{2.10}$$

$$NTF = 1 - L(z)z^{-1} (2.11)$$

$$L(z) = z[1 - NTF(z)]$$

(2.12)

Therefore, if NTF is FIR, the loop filter transfer function is also FIR. An FIR implementation is advantageous because the word-lengths for all the internal nodes can be pre-determined exactly and it does not give rise to stability issues if properly

designed [9].

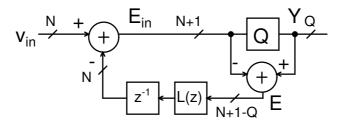

The condition for stability of an error feedback digital delta sigma modulator is that the maximum gain of the loop filter should be less than  $2^{Q-1}$ . Here, Q is the number of quantizer bits. In order to prove this, consider Fig.2.11. Assume that

Figure 2.11: Allowed word lengths for stable operation.

initially both the input and fedback signal has a word length of N bits. Then,  $E_{in}$  will have N+1 bits. Since the digital quantizer is just a word truncator, E will have N+1-Q bits. Now if a loop filter with a worst case gain of  $2^Q$  is chosen then, the output of the loop will have N+1 bits. Therefore, in the next cycle,  $E_{in}$  will have N+2 bits and so on. Two cycles later,  $E_{in}$  will have N+3 bits. Therefore, ultimately the system blows up and saturates. This proves that the maximum gain the loop filter can have for stable operation is  $2^{Q-1}$ .

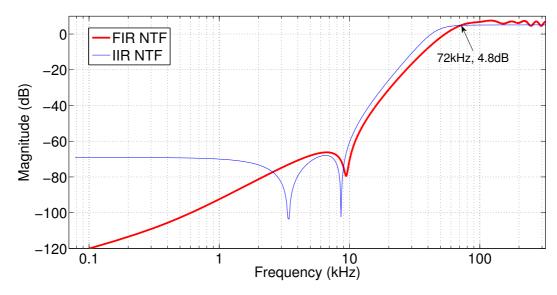

Next, the procedure for designing the loop filter is discussed. MATLAB has a toolbox named the delta sigma toolbox which can aid in the design of delta sigma modulators. However, if both Out of Band Gain(OBG) and order are fixed, it can give only IIR-NTFs. Therefore, the IIR-NTF has to be converted into FIR-NTF through custom design. This IIR-NTF is chosen so that it conforms to the stability criteria as discussed in the previous subsection. From the stability criteria it can be deduced that the worst case gain(OBG) of the NTF can be one greater than that of the loop filter's. Since a five bit quantizer is to be used, the maximum loop filter gain is restricted to be 16 and therefore that of the NTF can be 17. From simulations, a fifteenth order FIR-NTF was designed to give approximately the

same frequency response as that of the IIR-NTF. The NTF obtained was,

$$NTF(z) = 1.0000 - 1.3945z^{-1} - 0.3906z^{-2} + 0.2822z^{-3} + 0.4072z^{-4}$$

$$+ 0.2979z^{-5} + 0.1514z^{-6} - 0.0645z^{-7} - 0.1611z^{-8} - 0.0752z^{-9}$$

$$- 0.0664z^{-10} - 0.0460z^{-11} + 0.0254z^{-12} - 0.1064z^{-13} + 0.1406z^{-14}$$

$$(2.13)$$

The NTF frequency response is shown in Fig.2.12. This NTF response is after the coefficients were quantized. It is due to this coefficient quantization that the complex zeros are not exactly on the imaginary and thus have a relatively lower quality factor.

Figure 2.12: Matching IIR-NTF with FIR-NTF.

The loop filter transfer function is obtained as,

$$L(z) = 1.3945 + 0.3906z^{-1} - 0.2822z^{-2} - 0.4072z^{-3}$$

$$-0.2979z^{-4} - 0.1514z^{-5} + 0.0645z^{-6} + 0.1611z^{-7} + 0.0752z^{-8}$$

$$+0.0664z^{-9} + 0.0460z^{-10} - 0.0254z^{-11} + 0.1064z^{-12} - 0.1406z^{-13}$$

$$(2.14)$$

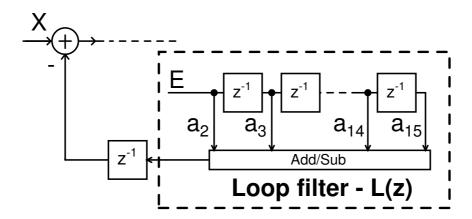

The FIR structure of the loop-filter L(z) is shown in Fig.2.13. Here,  $a_k$  refers to

the  $k^{th}$  coefficient of the NTF(Eq.2.13).

Figure 2.13: Architecture of the FIR loop filter.

The overall digital delta sigma modulator with word lengths is shown in Fig.2.14 This architecture was coded in verilog and synthesised using Design Vision.

Figure 2.14: Overall architecture of digital Delta Sigma modulator.

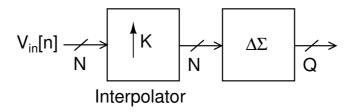

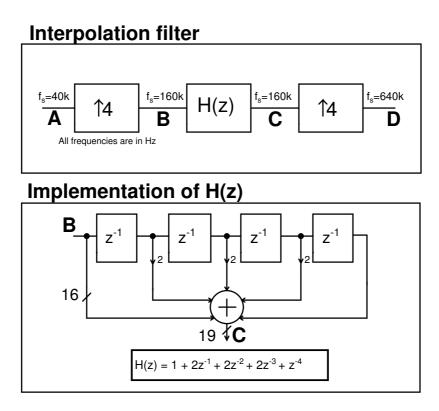

#### 2.2.3 Interpolator

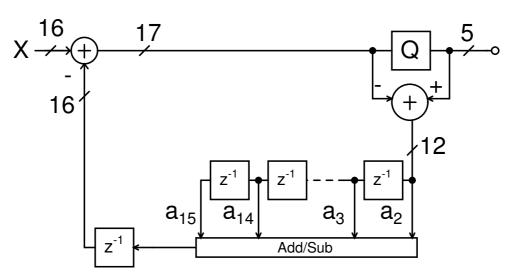

The input to the DSM block must be at the frequency of operation of the DSM. However, the input signal is a sixteen bit signal coming at 40 kHz. Therefore, the incoming signal has to be upsampled without distorting the signal band. The signal band-edge is 10 kHz and the OSR of the DSM is 32. Therefore, the DSM works at 640 kHz. Hence, the interpolator must interpolate by a factor of sixteen.

Interpolating by a factor of 16 at one shot would make its design very complicated and would waste considerable power. Instead, the interpolation can be split into multiple stages. There are multiple options to interpolate by a factor of 16. They are, 2x2x2x2, 2x4x2,4x4,2x8 and 8x2. It turns out that after every stage of interpolation a Low Pass Filter(LPF) is required to attenuate the images at the multiples of the carrier frequency. Therefore in the case of an 8x2 interpolator, the LPF would be operating at a very high frequency and hence its wasteful on power. Another reason is that the normalized cut-off frequency of the LPF would be very small leading to difficulties in its design. In the case of 2x8 interpolator, the design of the first LPF would be optimal but that of the final LPF would be more difficult because of lower normalized cut-off frequencies. 2x2x2x2 and 2x4x2 interpolators would require more low pass filters than the others and hence use more power and may lead to more in-band signal droop. The 4x4 interpolator is optimal in the sense that only two LPFs are needed, with the design complexity distributed evenly between the two stages. Hence a 4x4 interpolator has been adopted. The structure of the 4x4 interpolator along with the LPF H(z) is shown in Fig. 2.15. It is to be noted that all the coefficients were chosen as a power of two as the multiplication can be easily done by just bit-shifts. However choosing such integer coefficients makes the DC gain greater than unity and specifically eight in this particular design. This filtered output is again upsampled by four. However this does not cause an increase in word length. Therefore, the output signal of the interpolator (which is the input to the cross-point deriver) is nineteen bits wide.

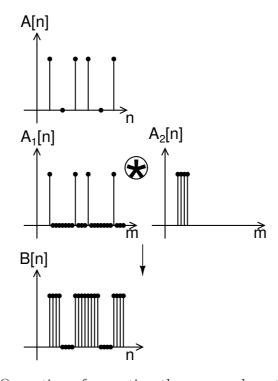

Upsampling by 4 is just repeating the same sample 4 times, but at a faster rate. B[n] is obtained from A[n] as shown in Fig.2.16.

Figure 2.15: Interpolation filter and the explicit low pass FIR filter.

Figure 2.16: Operation of repeating the same value at a higher rate.

Let the discrete-time Fourier transforms of the signals can be written as,

$$A[n] \leftrightarrow A(e^{j\omega}) \tag{2.15}$$

$$A_1[n] \leftrightarrow A(e^{j4\omega}) \tag{2.16}$$

$$A_2[n] \leftrightarrow 1 + e^{-j\omega} + e^{-2j\omega} + e^{-3j\omega}$$

(2.17)

$$=4e^{-j\frac{3\omega}{2}}\cos\left(\frac{\omega}{2}\right)\cos(\omega) \tag{2.18}$$

$$B[n] \leftrightarrow A_1(e^{j\omega})A_2(e^{j\omega}) \tag{2.19}$$

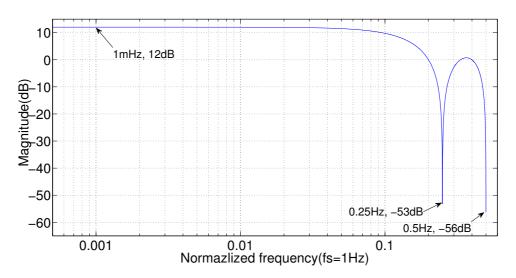

The above equation has nulls at  $\frac{f_s}{4}$  and  $\frac{f_s}{2}$  and therefore repeating the same value does inherent filtering as shown in Fig.2.17.

Figure 2.17: Frequency response of the inherent filtering.

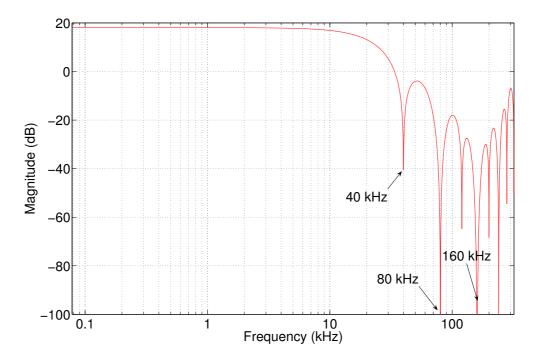

The second stage of interpolation by four is similar to that of the first stage. Therefore, there are three stages of filtering in all, where one is an explicit filter H(z) and the other two are the inherent filtering got by repeating the same value four times. From simulations it was found that another stage of explicit filtering is not required. Overall frequency response of the interpolator is shown in Fig.2.18.

Figure 2.18: Overall frequency response of the interpolator (320 kHz corresponds to  $\frac{f_s}{2}$ ).

#### 2.2.4 UPWM

This forms the final block of the sixteen bit digital to one bit digital converter. This block takes in DSM's five bit output and maps it into pulse widths. This is nothing but a counter which gets a start pulse based on the input amplitude it receives from the DSM. It receives the stop bit at the beginning of every carrier cycle. This block needs to work at  $2^5 \cdot 640 \,\mathrm{kHz}$ , i.e,  $20.48 \,\mathrm{MHz}$ . This block needs the highest frequency sampling clock in the whole system and hence the power consumed by this block would be significant. Thanks to the DSM block this highest frequency was restricted to  $20.48 \,\mathrm{MHz}$ .

All the above blocks were coded in verilog and the functionality was tested using MODELSIM. Once the design requirements were met, the gate-level synthesis was done using DESIGN VISION. The synthesized block was laid out using ENCOUNTER.

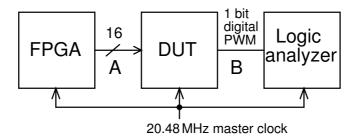

#### 2.2.5 Performance summary

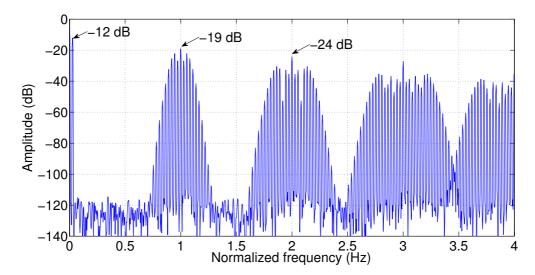

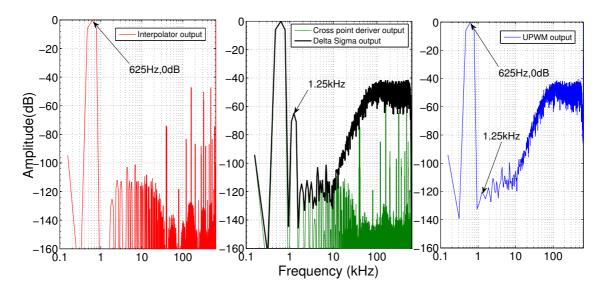

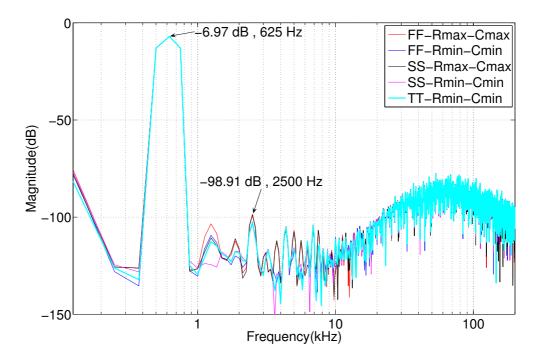

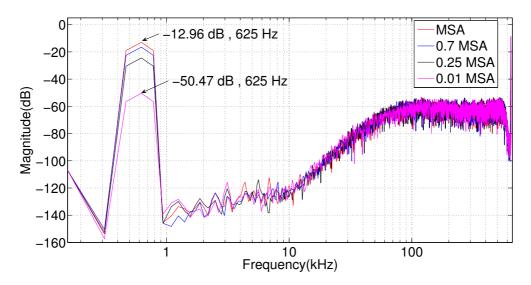

The layout-extracted netlist was simulated and the PSD of the signals at various nodes were plotted. The input signal is a single-tone sinusoid having an amplitude 0.95 times the maximum stable amplitude and a frequency of 625 Hz. The output spectrum was calculated after applying a Hanning window and averaging the PSDs over two cycles. This is shown in Fig.2.19

Figure 2.19: PSD of the signals at the output of various blocks.

With reference to Fig.2.19, it is clear that the final UPWM output is distortion free eventhough the output of the delta sigma modulator and the cross-point deriver are distorted. However, these should not be considered as distortion but instead as pre-distortion. This predistortion gets cancelled by the distortion of the UPWM block. Hence, the output will be free of distortion as shown in Fig.2.19.

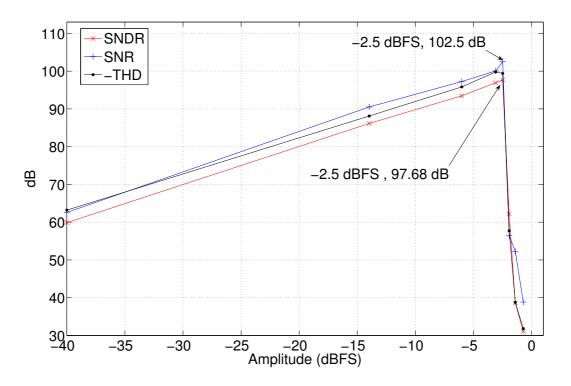

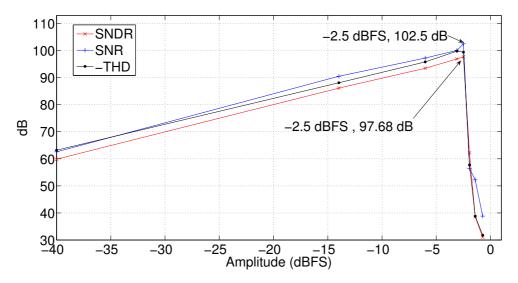

The input amplitude was swept and the SNDR, SNR and THD was calculated for each input amplitude. This curve is plotted in Fig.2.20. From Fig.2.20, it is clear that the dynamic range specifications are also met.

The performance achieved from the sixteen bit to one bit converter is tabulated in Table 2.2.

The UPWM block consumes the maximum power as it operates at the maximum

Figure 2.20: Amplitude sweep

Table 2.2: Performance summary of the digital section of the class-D backend driver

| Area                | $250\mu\mathrm{m} \times 250\mu\mathrm{m}$ |

|---------------------|--------------------------------------------|

| Power               | $33~\mu W$                                 |

| Interpolator        | 17 %                                       |

| Cross-point deriver | 7 %                                        |

| Digital DSM         | 32%                                        |

| UPWM block          | 38%                                        |

| SNDR                | $97.662\mathrm{dB}$                        |

| THD                 | $-102.225\mathrm{dB}$                      |

clock frequency of  $2^5 \cdot 640 \, \text{kHz} = 20.48 \, \text{MHz}$ . From Table.2.2 it is clear that the required specifications were met. The next step is to use this one bit signal to drive the speakers. This is discussed in the next chapter.

## CHAPTER 3

## Analog section of class-D amplifier

### 3.1 Introduction

The procedure to convert a sixteen bit signal into a one bit signal without losing any information was discussed in Chapter 2. Now, this one bit signal should be applied to the speakers without any further loss in the signal quality. Apart from that, it must also be able to efficiently drive the speakers.

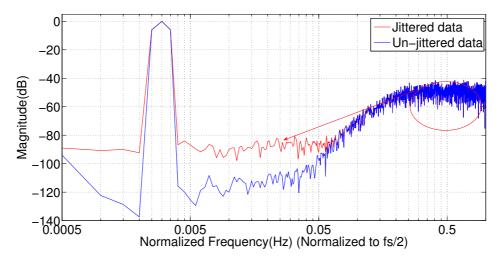

If the one bit digital signal is directly applied to class-D power stage, there are several issues that degrade the quality of the signal. The most important issue is clock jitter-data modulation. The problem of jitter occurs at the digital to analog interface and is especially severe for systems whose output has a large amount of high frequency content. A typical example is the DSM. The clock used for the digital system will usually have jittery edges and therefore the DAC's output will also have jittery edges. This causes the charge transferred into the speaker also to be jittery. This phenomenon causes the clock jitter spectrum to modulate with the data spectrum and increases the noise floor within the signal band. In the case of oversampled converters, the high frequency regions(around  $\frac{f_s}{2}$  contribute to much of the increase in the inband noise floor. This is depicted in Fig.3.1

One way to mitigate this problem is to retime the data using a low-jitter clock and then give it to the H-Bridge. However, getting a low jitter clock might be expensive and/or power hungry. Another way to mitigate this problem is using a one bit switched capacitor DAC(SC-DAC). Here the amount of charge transferred is independent of the clock and is ideally limited only by the noise on the references used for the charge-transfer. Therefore, the jitter suppression can be ideally very

Figure 3.1: Clock jitter modulating with data and raising the inband.

good. Other types of DAC pulses can also be chosen to reduce jitter-sensitivity. However, there is an important issue with using DAC pulses that are not rectangular. Non-rectangular pulses do not lend themselves directly to adopt the principle of class-D amplification. Another stage of PWM would be required to convert the signal back into rectangular shape. This was illustrated in Chapter.2 in Fig.2.2. Since now the final PWM stage requires generation of an analog carrier and uses an analog comparator, there are many sources of non-linearities and errors which can counter the advantage of reducing jitter.

Since jitter should definitely be suppressed to be able to meet the design requirements, changes must be made in the DAC pulse shape even at the expense of using an analog PWM block. However, a negative feedback loop would have to be built around the PWM driver stage to suppress the non-idealities encountered there. It turns out that, using a closed-loop analog class-D stage does not only help in choosing an arbitrary pulse shape to keep jitter under control, but also is very beneficial to suppress other non-idealities in the driver stage.

Another important reason why a closed loop solution is much better than an open loop one is that of PSRR. Any noise or stray signal on the supply or ground modulates with the data. If data is represented as D(t) and the output voltage

across the load as  $V_L(t)$  then,

$$V_L(t) = [V_{dd}(t) - V_{gnd}(t)] \cdot D(t)$$

(3.1)

The data is either +1 or -1. Therefore, the supply spectrum convolves with the data spectrum giving rise to problems similar to that of jitter data modulation. This issue is severe at high input amplitudes. A proven approach to improve the PSRR is to build a feedback loop around the H-Bridge. This solves many problems at one go. It helps improve the PSRR considerably, attenuates nonlinearities arising due to dead-time and finite rise and fall times of the PWM signal. The dead-time nonlinearity is particularly severe in class-D amplifiers and hence a closed loop solution is a must for hi-fidelity and large dynamic range audio amplifiers. Therefore, a closed loop analog solution has been adopted in this work. Since a closed-loop analog class-D driver stage is going to be employed, it is advantageous in many aspects to make the loop fully differential. A fundamental advantage is that the H-Bridge can output four times higher power than that of a single ended structure. The other benefits are that all even harmonics gets cancelled out and the disturbances that are common-mode to the loop is rejected. Another important advantage specific to audio applications is that the DC component across the load can be removed without using a negative supply. DC across the speaker can potentially damage it. If a negative supply is not available, huge DC blocking capacitors which occupy excessive area would need to be used. On the other hand, going for a fully differential structure would mean double the number of components and hence four times the area (all the four switches must have twice the width of the single-ended version to maintain the same on-resistance).

## 3.2 Target specifications

The targetted performance is shown in Table 3.1

Table 3.1: Target specifications for the analog section of the class-D driver

| Signal bandwidth | $100\mathrm{Hz}$ to $10\mathrm{kHz}$ |

|------------------|--------------------------------------|

| Dynamic range    | > 94.50  dB                          |

| THD              | better than $-70.00\mathrm{dB}$      |

| Thermal noise    | $12\mu V_{rms}$                      |

| PSRR             | $> 55 \mathrm{dB}$                   |

| Output impedance | $20\Omega/40\Omega$                  |

# 3.3 Loop filter Design

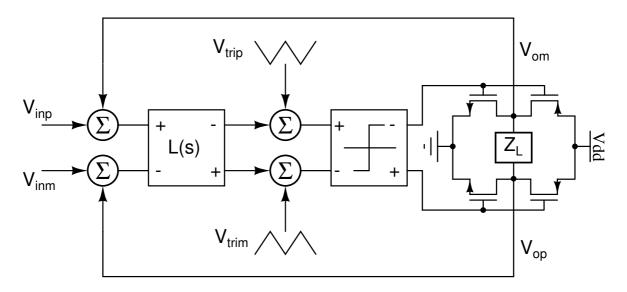

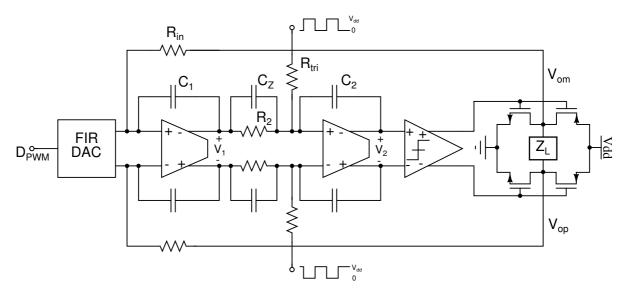

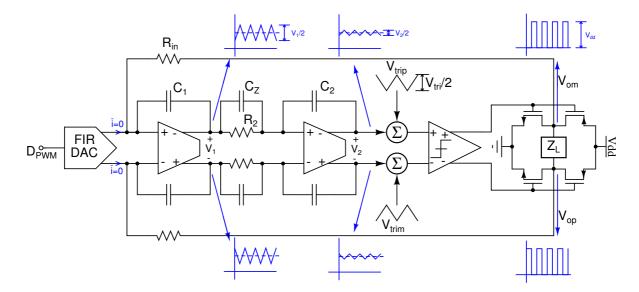

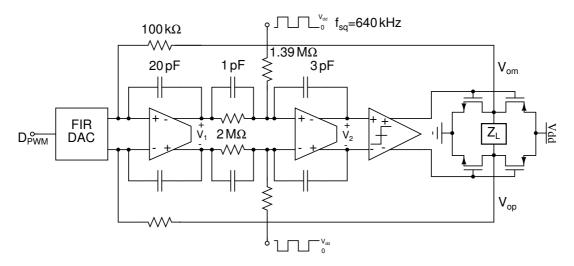

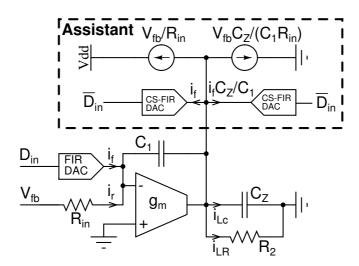

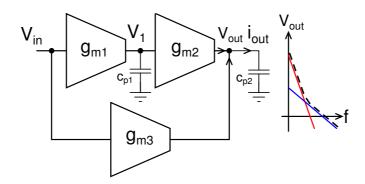

Figure 3.2: Architecture of closed-loop Class-D amplifier.

Fig. 3.2 shows the architecture of a closed-loop class-D amplifier. The first summer calculates the error between the input signal and the fedback signal within the unity gain bandwidth of the loop. This error signal is applied as input to the loop filter, L. The loop filter is generally an integrator or a cascade of integrators. Effectively, the differential output of the loop filter is compared with a differential triangular carrier to generate the PWM signal. This PWM signal is given as input to the H-Bridge which drives the speakers. This type of modulation is known as NADD modulation (where both the message and carrier are out of phase across the differential arms) and is well suited for fully differential circuits because it has no common-mode component at its output. Another advantage is that the radiation from the output wires that carry the PWM is minimum because of no common-mode components (only common-mode components radiate).

The design choices that are to be made are, the loop filter's order and bandwidth and the triangular carrier's amplitude and frequency. All the above parameters cannot be chosen in a single-shot and some iteration is required. The frequency of the triangular carrier is chosen based on the allowable switching loss, inband performance and the type of demodulation filter. Too high a switching frequency would cause efficiency degradation due to higher switching losses but would lead to a lower order demodulation filter and a better inband performance. On the other hand, a lower carrier frequency would lead to lower switching losses but at the expense of a poorer inband performance and a higher order demodulation filter. A compromise has to be arrived on the carrier frequency, weighing the requirements of the above three issues. From simulations, 640 kHz was chosen to be the carrier frequency.

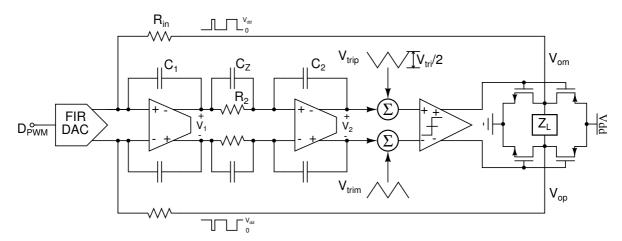

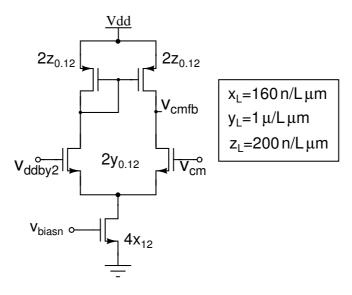

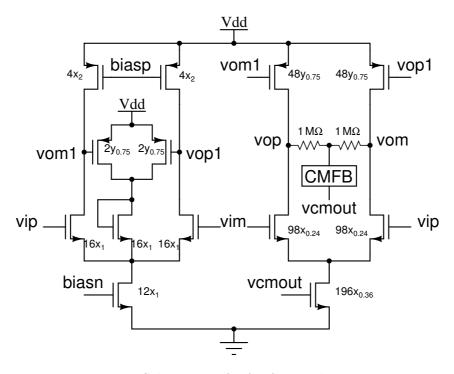

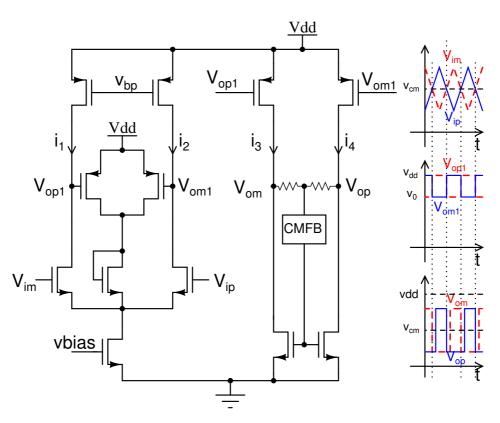

The next design choice to make is the order of the loop filter. As a starting point, the Unity Gain Bandwidth(UGB) of the loop can be assumed to be 300 kHz, which is at least two times lower than the carrier frequency. If it is desired to have at least 50 dB loop gain at the signal band-edge frequency of 10 kHz, a second order loop filter would be required. The architecture of the second order loop filter is shown in Fig.3.3. The reason for choosing such an architecture and the reason for using FIR-DAC will become clear later in this chapter.

Figure 3.3: Second order closed-loop Class-D amplifier.

It should be noted that implementing the system in Fig.3.3 would require a triangle

wave generator and a summer. A better implementation of this system is shown in Fig.3.4. In this modified version, a pulse voltage waveform having fifty percent

Figure 3.4: Second order closed-loop Class-D amplifier with triangular carrier generator.

duty cycle is integrated by the second integrator. Therefore, the output of the second integrator is the sum of the triangular carrier and the output of the second order loop filter. Therefore, the second integrator is used to advantage as it acts both to increase low-frequency loop gain and as a triangle wave generator. This architecture is advantageous in the sense that, the system-clock or its sub-multiple can be directly used as the square wave that gets integrated to form the triangular carrier. Another advantage is that the high-frequency jitter in the square-wave clock is attenuated by the second integrator before getting shaped by the feedback loop [10].

The next important thing to be considered is stability. There are two main reasons that cause instability in closed-loop PWM class-D amplifiers. They are;

- 1. Ripple stability criteria[6]- High loop-UGB, or in other words, the slope of the loop-filter's output being greater than the slope of the triangular carrier.

- 2. Excessive delay in the loop or phase margin problem.

The first requirement is fundamental to PWM loops whereas the second is a general design issue in all negative feedback loops. To state the first stability problem

differently, if the amplitude of the signal that is to be compared with the triangular carrier is greater than the amplitude of the triangular carrier itself, then PWM output is saturated and no natural sampling occurs. This condition is illustrated in Fig.3.5. In principle, the dotted pulse should have been generated but it was missed due to overloading.

Figure 3.5: Ripple stability criteria being violated.

This is similar to the overloading of quantizers in a delta sigma modulator. When this condition occurs the pulse width becomes greater than one sampling period. This will cause the integrator's output to saturate. It might happen that the modulator will never be able to come out of this saturated state, since the feedback is broken. This is a large signal phenomenon and it depends on the system architecture. For converting the above stability criteria in terms of system parameters, consider Fig.3.3. Fig.3.3 is chosen instead of Fig.3.4 for a more visually intuitive analysis. Let's initially restrict the input to be only DC having an amplitude of  $V_{cm}$  which is equal to  $\frac{V_{dd}}{2}$ . This is the amplitude that gives the maximum worst-case ripple and it corresponds to a duty cycle(D) of 0.5. Ideally, by virtue of negative feedback, one would expect the second integrator's differential output to also be just a DC voltage of value  $V_{cm}$ . However, due to the high-frequency components in the fedback signal, additional ripple is introduced over the DC waveform as shown in Fig.3.6.

The swing at  $V_1$  is mainly due to the ripple caused by the fedback PWM voltage and the swing at  $V_2$  is sum of the scaled ripple at  $V_1$  and the wanted signal. The second order path does not contribute much to the ripple at  $V_2$  because of its very

Figure 3.6: Waveforms at required nodes for calculating stability requirements.

low gain at the carrier frequency ( $\frac{1}{T_s}).$  Therefore;

$$|V_1| = \frac{V_{dd}}{R_{in}C_1} \frac{T_s}{2} \tag{3.2}$$

$$|V_2| \approx \frac{V_{dd}}{R_{in}C_1} \frac{T_s}{2} \frac{C_Z}{C_2} \tag{3.3}$$

The condition for stability is;

$$V_2 < V_{tri} \tag{3.4}$$

$$\frac{V_{dd}}{R_{in}C_1} \frac{T_s}{2} \frac{C_Z}{C_2} < V_{tri} \tag{3.5}$$

From Fig.3.4,

$$V_{tri} = \frac{V_{dd}}{R_{tri}} \frac{T_s}{2C_2} \tag{3.6}$$

therefore from Eq.3.5,

$$\frac{V_{dd}}{R_{in}C_1} \frac{T_s}{2} \frac{C_Z}{C_2} < \frac{V_{dd}}{R_{tri}} \frac{T_s}{2C_2}$$

$$R_{tri} < R_{in} \frac{C_1}{C_Z} \tag{3.7}$$

The above equation shows that there is a minimum required triangular carrier

amplitude below which the modulator becomes unstable. Another point to take away from this derivation is in Eq.3.7. From it, it is clear that changing the supply or  $f_s$  does not change the stability of the loop(in this particular architecture). Therefore, this loop's stability is supply and clock-frequency independent.

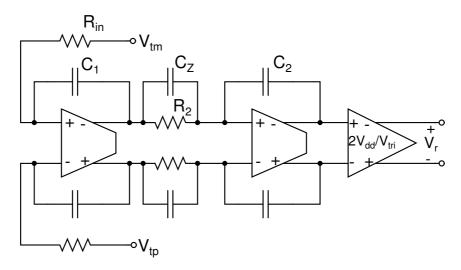

It is also possible to derive a relation between the UGB of the loop and the carrier frequency that ensures that the loop remains stable. To calculate the UGB of the loop, consider the linearized version of the open loop of the corresponding closed-loop class-D amplifier which is shown in Fig.3.7.

Figure 3.7: Linearized Class-D loop.

Note that the FIR-DAC does not come into picture as it is across a low-impedance node and ground. From Fig.3.3, the nonlinear block is the PWM generator which includes the comparator and the H-Bridge driver. The low-frequency linear model of these two blocks put together is a simple gain stage having a gain  $\frac{2V_{dd}}{V_{tri}}$  as explained in Appendix. C.

The UGB of the open-loop is derived below;

$$V_r(s) = -V_{td} \frac{1}{sR_{in}C_1} \left[ \frac{C_Z}{C_2} + \frac{1}{sR_2C_2} \right] \frac{2V_{dd}}{V_{tri}}$$

(3.8)

where  $V_{td}$  is  $V_{tm} - V_{tp}$

For the loop to remain stable, the loop-gain must cross the UGB with a slope of

-20 dB/decade. In other words, the system should be first order around the loop's UGB. Therefore, the zero frequency is chosen to be well within the UGB. This implies that the system is asymptotically first order around UGB and hence we can neglect the second order path for calculating the UGB. Therefore,

$$UGB = \frac{C_Z}{R_{in}C_1C_2} \frac{2V_{dd}}{V_{tri}}$$

(3.9)

Combining Eq.3.5 and Eq.3.9;

$$UGB < \frac{2f_c}{\pi} \tag{3.10}$$

Here,  $f_c$  is the triangular carrier frequency. However, if the input is a signal, then the ripple is superimposed on a scaled version of the input signal at the input of the comparator. Therefore, in practice, the carrier frequency is chosen at least two to five times the required loop bandwidth.

To tackle the second problem of excessive delay around a loop, a fast path/bypass path is provided around one of the delay causing blocks. In other words a zero is introduced into the loop. From Fig.3.3, 3.4, the capacitor  $C_Z$  is the compensation capacitor which provides a bypass path around the second integrator at high frequencies. This can also be thought of as adding a zero to the loop, with the zero frequency being  $\frac{1}{R_2C_Z}$ . Therefore, correctly choosing the value of capacitor  $C_Z$  solves the phase margin problem.

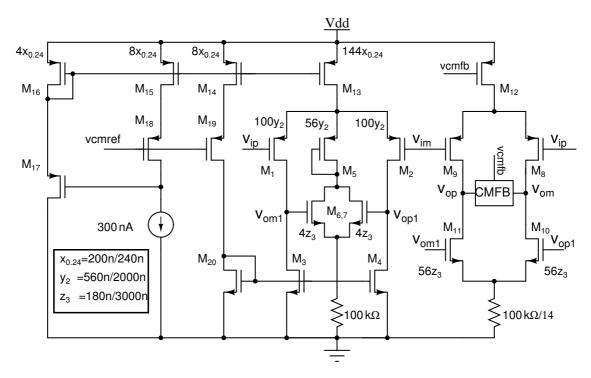

The next design step is to choose components such that the noise-power constraints are met. The maximum allowed noise power is 144 pW (Table.3.1). The major contributors of noise in this system are the feedback resistors, input resistors(FIR-DAC) and the amplifier of the first integrator. For now, the FIR-DAC can be assumed to be a simple resistor of value  $R_{in}$  within the range of analysis, that is, the signal band. Let  $S_{R_{in,n}}$  and  $S_{amp1,n}$  denote the input-referred noise power spectral density of the resistors(and also for the FIR-DAC) and the amplifier of

the first integrator, respectively. It is also assumed for now that, the amplifier is a simple two-stage, Miller-compensated structure. Then the contribution of thermal noise at the output is;

$$S_{out,n} = 4S_{R_{in,n}} + 4S_{amp1,n} (3.11)$$

where,  $S_{R_{in},n}$ =4kTB $R_{in}$ +flicker noise, where k=Boltzman's constant, B=signal bandwidth(10 kHz),  $T_{max}$ =343 K and  $S_{amp1,n} = \frac{16kT}{3g_m}$ + flicker noise, where  $g_m$  is the transconductance of the input pair of the amplifier of the first integrator. The load transistors of the first stage also contributes to noise but however the noise power is divided by the  $g_m^2$  of the input pair. Therefore, if the  $g_m$  of the input pair is chosen much higher than the load transistor's  $g_m$ , its noise contribution would be relatively less. It should be noted that the flicker noise is also a dominant contributor to the inband noise power. The bulk of the noise contribution comes from the lower frequencies. However, this noise can be easily reduced by increasing the device sizes and does not cause a direct power penalty as in the case of reducing thermal noise. However, since now the devices are larger, the parasitics also increase and one might be required to burn more power to meet the required specifications.

$R_{in}$  is mainly chosen based on noise(Eq.3.11) and linearity constraints. Therefore, the input resistors cannot be very large in value. The input resistors cannot also be too small because it would then demand huge currents from the non-linear amplifiers of the integrators. This might give rise to linearity issues depending upon the architecture adopted for the amplifier. This is also wasteful of power as a larger quiescent current is required in the driving stage of the amplifier in the first integrator in order to keep the distortion at respectable levels. From the allowed noise budget, it is advantageous to make the resistor contribute more to noise than the amplifier. Since now, to reduce the noise contribution from the amplifier, more power will be burnt to increase the  $g_m$  of the input pair and always increasing the  $g_m$  of the amplifier would have other benefits namely, reducing problems due

to transistor mismatch, random offsets and any error at the output of the first stage. Therefore it was decided to make the resistor contribute 60% of the 144 pW budget. This corresponds to a typical resistance value of  $100 \,\mathrm{k}\Omega$  after accounting for process and temperature variations of the resistance.

The components  $C_1$ ,  $R_2$ ,  $C_Z$ ,  $C_2$  and  $V_{tri}$  were chosen based on the stability constraints(Eq.3.10) and the required loop-UGB(300 kHz). Through simulations, the system parameters decided upon is shown in Fig.3.8. (Note:  $V_{dd}=1.2\,\text{V}$ ). The values arrived at is after node-scaling.

Figure 3.8: Closed loop class-D amplifier with component values indicated.

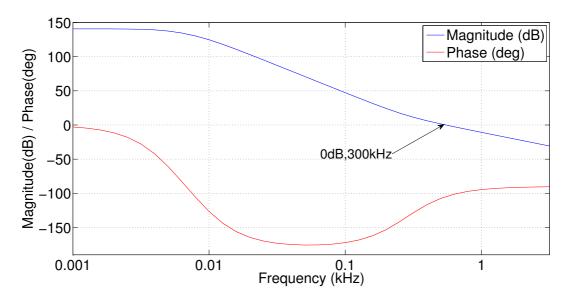

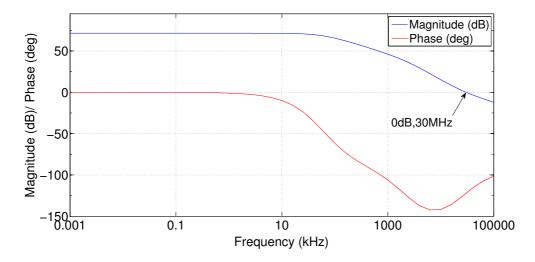

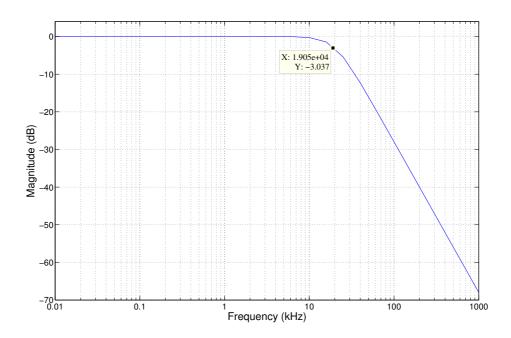

The loop gain and the phase margin plots vs frequency is shown in Fig.3.9.

## 3.3.1 Finite Impulse Response DAC (FIR-DAC)

The problem of clock-jitter modulating with the data surfaces at the digital to analog interface. The reason is that the charge transferred in each cycle into the analog blocks is itself jittery due to the jittery clock. One solution is to use a switched capacitor DAC(SC-DAC). Here, the amount of charge transferred is independent of the clock as long as the capacitor charges/discharges to the final value. However, it draws huge spiky currents during clock transitions which will cause the amplifier in the first integrator to slew. This slewing causes the amplifier

Figure 3.9: Magnitude and phase response of the Class-D loop.

to become non-linear and causes distortion. Another way is to retime the 1-bit digital output using a low-jitter clock. The disadvantage in this approach is the requirement/availability of a low-jitter clock.

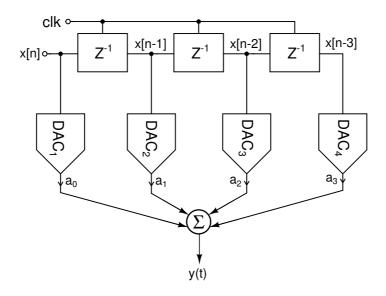

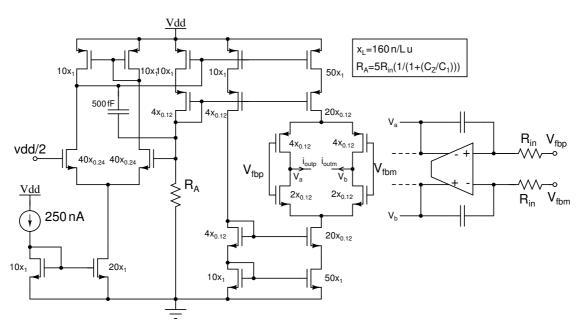

An elegant way of reducing the effect of jitter on the amount of charge transferred is by using an FIR-DAC. The general structure of an FIR-DAC is shown in Fig.3.10. It is to be realized that the major contribution to increase in inband noise floor due

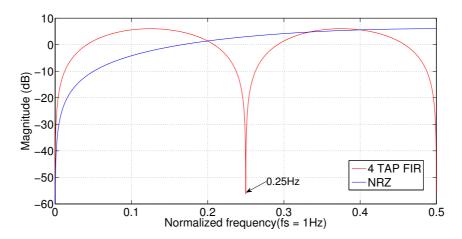

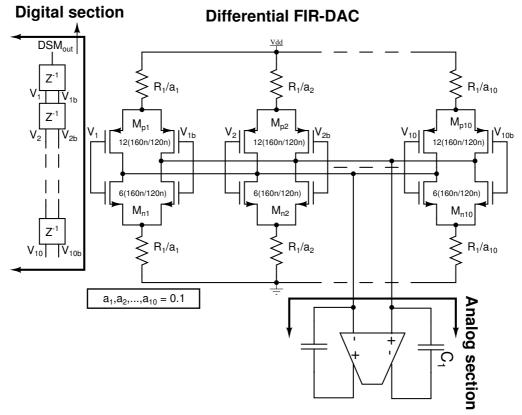

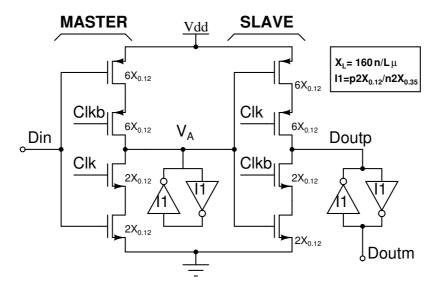

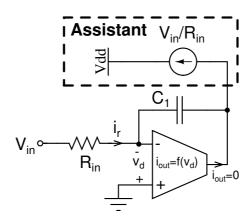

Figure 3.10: Architecture of a 4-tap FIR-DAC.

to data-jitter modulation is from the folding back of high frequency components of the data. Hence by filtering out the high frequency data, the amount of fold-back can be reduced. This is exactly what an FIR-FILTER-DAC does. Therefore, the basic idea is to filter out the high frequency components around  $\frac{f_s}{2}$ .

The mechanism by which this architecture reduces jitter can be understood with the help of Fig.3.11.

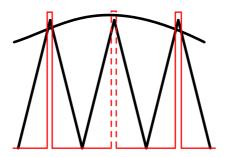

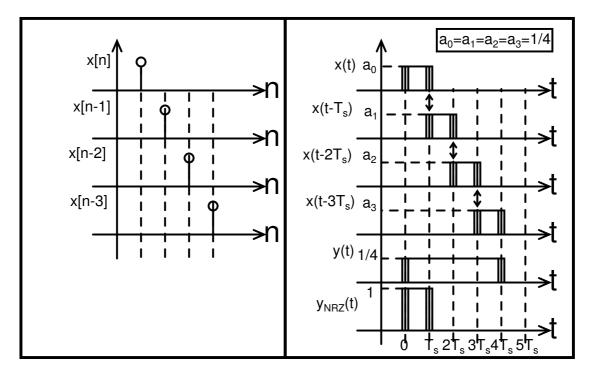

Figure 3.11: Jitter cancelling mechanism in FIR-DAC.

All the DAC elements are of the Non-Return-to-Zero(NRZ) type. Assume for simplicity that all the coefficients has the same value. The co-efficients are scaled to make the DC gain unity. Consider the input x[n] to be a digital impulse. The corresponding signal at each node of Fig.3.10 is shown in Fig.3.11. The jittery edges during data transitions is due to the fact that the instant at which the clock changes its state itself is jittery and quite random. Therefore the area of the shaded portion represents the error in the amount of charge that has been transferred to the analog system due to the clock edges being jittered. From the illustration, the main point to note is that any error in the charge transferred in the current cycle is compensated by the error in the charge transferred in the next cycle. This is because, if the clock period of the current cycle increases (relative to the ideal reference period) then, the clock period of the next cycle

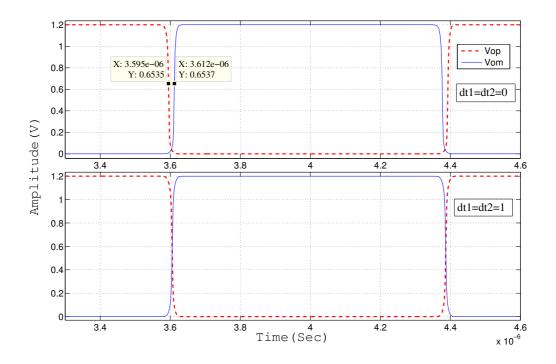

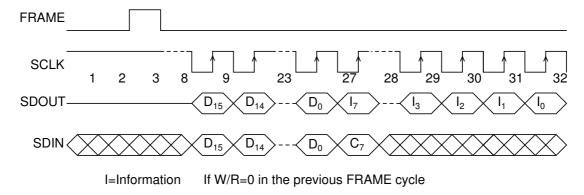

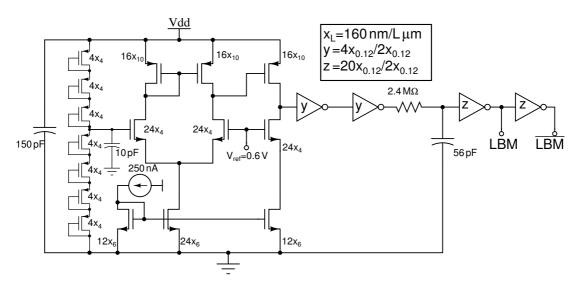

automatically reduces (assuming the other edge is jitter-free). This cancellation property is true for all the intermediate cycles except for the first and the last cycle. Therefore, only the jitter in the first and the last cycle matters. The error in charge that gets compensated is indicated by double-arrows in Fig.3.11. The above cancellation does not occur if say a Return-to-Zero DAC(RZ-DAC) is used for the DAC elements but however, it gives lower jitter sensitivity than a simple RZ DAC because of the filtering of high frequency components.