## Theory, Practice, and Fundamental Performance Limits of High-Speed Data Conversion Using Continuous-Time Delta-Sigma Modulators

by

James A. Cherry

A Ph.D. thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Ottawa-Carleton Institute for Electrical and Computer Engineering, Department of Electronics, Carleton University, Ottawa, Ontario, Canada

November 20, 1998

© 1998 by James A. Cherry

#### Acknowledgments

For research inspiration, thanks to Omid Shoaei and Lars Risbo for their thought-provoking Ph.D. theses, Joe Jensen and Gopal Raghavan at HRL for their paper which got me interested in high-speed  $\Delta\Sigma M$ , and big thanks to Weinan Gao for discussions on theory and for allowing me access to his circuit design for simulation and testing purposes which resulted in a much more practical and relevant final thesis for me. I am grateful to him.

At Nortel, thanks to Robert Hadaway for access to the SiGe process, Sorin Voinigescu and Dave Marchesan for assistance with layout and simulation, Etienne Bernard and Marie Quinn for die cutting, José Macedo and Glen Tiegs for packaging suggestions, Icy Jackson for packaging the test chips, and big thanks to Dr. Peter Schvan for all his help getting me access to the building and computer system and for allowing me to use the SPICE files for his original prototype.

For modulator testing, thanks to Sergiy Uhanov and Nagui Mikhail for help with procuring and calibrating measurement equipment, big thanks to Joe Jensen and Gopal Raghavan at HRL for letting me capture bit streams on their high-speed oscilloscope, and biggest thanks to Philip J. Lauzon for his tireless design, redesign, and assembling of printed circuit boards.

Most of all, thanks to my supervisor, Martin Snelgrove, for seeing me through six years of graduate school and encouraging me, and to Melissa Fritz for putting up with my schedule during the last year and supporting me.

#### Abstract

We consider the design of high-speed continuous-time delta-sigma modulators for analog-todigital conversion. Many of the nonidealities that affect performance in discrete-time modulators do likewise in continuous-time modulators, yet there are three additional important considerations unique to continuous-time modulators. The first, excess loop delay, is the time delay between the quantizer clock and the output of the feedback, which affects stability and dynamic range; its effect can be reduced by employing return-to-zero-style DACs and feedback coefficient tuning. The second, clock jitter, whitens the output spectrum in the quantization noise notch and lowers SNR; a carefully-designed VCO will alleviate its effects for all but very wideband or high-resolution modulators. The third, quantizer metastability, also whitens the output spectrum and lowers SNR; it is essential to use a three half-latch quantizer over a simple master/slave design to provide extra regeneration, and even then it is best not to clock faster than about 5% of maximum transistor switching speed. A design procedure is given for band pass modulators whose intended application is conversion of analog signals at one quarter of the sampling frequency, and a fabricated 4GHz modulator for 1GHz signal conversion is simulated, tested, and redesigned to improve its performance from 6 bits to 10 bits. Finally, the appropriateness of high-speed continuous-time delta-sigma modulation is considered for various applications.

## Contents

| 1 | Intro             | oduction | n                                    | 1  |

|---|-------------------|----------|--------------------------------------|----|

|   | 1.1               | Motiva   | ntion                                | 1  |

|   | 1.2               | Contril  | butions                              | 2  |

|   | 1.3               | Organi   | zation                               | 3  |

| 2 | $\Delta \Sigma N$ | A Conc   | epts                                 | 5  |

|   | 2.1               | A Brie   | f Introduction to $\Delta \Sigma M$  | 5  |

|   |                   | 2.1.1    | Operating Principles                 | 5  |

|   |                   | 2.1.2    | Design Choices                       | 9  |

|   | 2.2               | Perform  | mance Measures                       | 14 |

|   |                   | 2.2.1    | Power Spectrum Estimation            | 14 |

|   |                   | 2.2.2    | Signal to Noise Ratio (SNR)          | 17 |

|   |                   | 2.2.3    | Other Performance Measures           | 23 |

|   | 2.3               | Simula   | tion Methods                         | 27 |

|   |                   | 2.3.1    | Discrete-Time Modulator Simulation   | 27 |

|   |                   | 2.3.2    | Continuous-Time Modulator Simulation | 29 |

|   | 2.4               | Summa    | ary                                  | 31 |

| 3 | $\Delta \Sigma$ N | /I Imple | ementation Issues                    | 33 |

|   | 3.1               | Nonide   | ealities in $\Delta \Sigma Ms$       | 33 |

|   |                   | 3.1.1    | Op Amps                              | 34 |

|   |      | 3.1.2           | Mismatch and Tolerance                              | 38 |

|---|------|-----------------|-----------------------------------------------------|----|

|   |      | 3.1.3           | Quantizers                                          | 39 |

|   |      | 3.1.4           | Circuit Noise                                       | 39 |

|   |      | 3.1.5           | Other Nonidealities                                 | 40 |

|   | 3.2  | Import          | ant CT $\Delta \Sigma$ M Papers: A Survey           | 42 |

|   |      | 3.2.1           | Paper List                                          | 42 |

|   |      | 3.2.2           | High-Speed CT $\Delta \Sigma$ M Performance Summary | 48 |

|   | 3.3  | Summ            | ary                                                 | 51 |

| 4 | Exce | ess Looj        | o Delay                                             | 53 |

|   | 4.1  | Prelim          | inaries                                             | 54 |

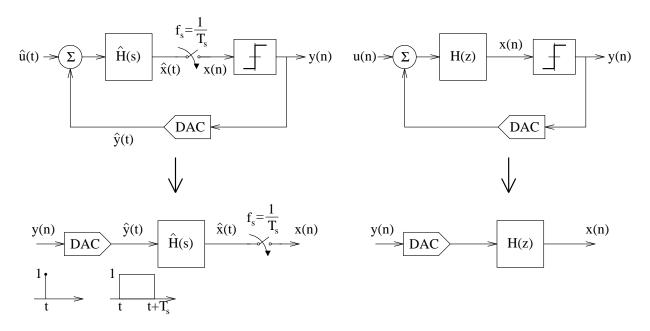

|   |      | 4.1.1           | CT/DT Modulator Equivalence                         | 55 |

|   |      | 4.1.2           | Usefulness of Equivalence                           | 56 |

|   |      | 4.1.3           | Effect of Excess Loop Delay                         | 59 |

|   | 4.2  | Double          | e Integration Modulator                             | 63 |

|   |      | 4.2.1           | Root Locus                                          | 63 |

|   |      | 4.2.2           | In-Band Noise                                       | 64 |

|   |      | 4.2.3           | Maximum Stable Amplitude                            | 66 |

|   |      | 4.2.4           | Dynamic Range                                       | 67 |

|   | 4.3  | $f_s/4~{ m Fe}$ | ourth-Order Band Pass Modulator                     | 68 |

|   | 4.4  | Higher          | -Order Modulators                                   | 72 |

|   | 4.5  | Modul           | ators with a Multibit Quantizer                     | 77 |

|   | 4.6  | Compe           | ensating for Excess Loop Delay                      | 78 |

|   |      | 4.6.1           | DAC Pulse Selection                                 | 78 |

|   |      | 4.6.2           | Feedback Coefficient Tuning                         | 80 |

|   |      | 4.6.3           | Additional Feedback Parameters                      | 84 |

|   | 4.7  | Summ            | ary                                                 | 86 |

| 5 | Cloc | k Jitter |                                                  | 89  |

|---|------|----------|--------------------------------------------------|-----|

|   | 5.1  | Prelim   | inaries                                          | 90  |

|   |      | 5.1.1    | Modulator Architecture                           | 90  |

|   |      | 5.1.2    | Simulation Method                                | 91  |

|   | 5.2  | Effect   | of Clock Jitter on an Ideal CT $\Delta \Sigma M$ | 92  |

|   |      | 5.2.1    | LP Modulators with NRZ Feedback                  | 92  |

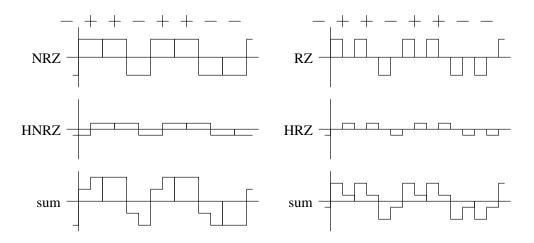

|   |      | 5.2.2    | Modulators with RZ and/or HRZ Feedback           | 97  |

|   | 5.3  | Clocki   | ng with a VCO                                    | 100 |

|   |      | 5.3.1    | Modeling VCO Phase Noise                         | 100 |

|   |      | 5.3.2    | Effect of Accumulated Jitter on Performance      | 102 |

|   | 5.4  | Summ     | ary                                              | 106 |

| 6 | Qua  | ntizer N | Metastability                                    | 107 |

|   | 6.1  | Backgr   | round                                            | 107 |

|   |      | 6.1.1    | Initial Observations                             | 108 |

|   |      | 6.1.2    | z-Domain Extraction                              | 109 |

|   |      | 6.1.3    | Examining the Errors                             | 110 |

|   |      | 6.1.4    | Usefulness of z-Domain Extraction                | 111 |

|   | 6.2  | Latche   | s and Metastability                              | 113 |

|   |      | 6.2.1    | Digital Circuits vs. $\Delta \Sigma Ms$          | 114 |

|   |      | 6.2.2    | Characterization Method for $\Delta \Sigma Ms$   | 116 |

|   |      | 6.2.3    | Validation of Quantizer Model                    | 118 |

|   | 6.3  | Real Q   | Quantizer Performance Effects                    | 121 |

|   | 6.4  | Mitiga   | ting Metastability Performance Loss              | 127 |

|   |      | 6.4.1    | Parameter Scaling                                | 127 |

|   |      | 6.4.2    | Regeneration Time                                | 128 |

|   |      | 6.4.3    | Preamplification                                 | 130 |

|   |      | 6.4.4    | Additional Latching Stages                       | 132 |

|   |      | 6.4.5    | Other Modulator Architectures                    | 135 |

|   | 6.5  | Maximum Clocking Frequency                                       |

|---|------|------------------------------------------------------------------|

|   | 6.6  | Summary                                                          |

| 7 | A 40 | <b>GHz Fourth-Order Band Pass</b> $\Delta \Sigma \mathbf{M}$ 141 |

|   | 7.1  | General Design Considerations                                    |

|   |      | 7.1.1 Element Parameter Selection                                |

|   |      | 7.1.2 Design Procedure                                           |

|   |      | 7.1.3 Parameters for This Design                                 |

|   | 7.2  | Circuit Blocks                                                   |

|   |      | 7.2.1 Resonator                                                  |

|   |      | 7.2.2 Latch                                                      |

|   |      | 7.2.3 Output Buffer                                              |

|   |      | 7.2.4 DAC                                                        |

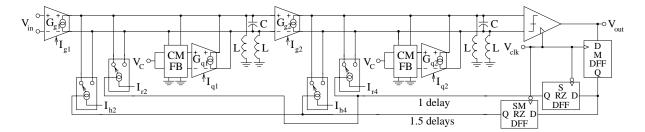

|   |      | 7.2.5 Complete Circuit                                           |

|   | 7.3  | Measurement Results                                              |

|   |      | 7.3.1 Resonator                                                  |

|   |      | 7.3.2 Latch                                                      |

|   |      | 7.3.3 Output Buffer                                              |

|   |      | 7.3.4 DAC                                                        |

|   |      | 7.3.5 Dynamic Range                                              |

|   | 7.4  | Result Commentary                                                |

|   |      | 7.4.1 Design for Testability                                     |

|   |      | 7.4.2 Known Circuit Problems                                     |

|   |      | 7.4.3 Unaddressed Circuit Issues                                 |

|   | 7.5  | Summary                                                          |

| 8 | Cone | clusions 207                                                     |

|   | 8.1  | Summary of Contributions and Results                             |

|   | 8.2  | Practical $\Delta \Sigma M$ Applications                         |

iv

|   | 8.3 Future Work                                     | 211 |

|---|-----------------------------------------------------|-----|

| A | DR Derivations                                      | 227 |

|   | A.1 VCO Clock Jitter                                | 227 |

|   | A.2 Three Half-Latch Quantizer                      | 228 |

| B | <b>BP</b> $\Delta \Sigma$ <b>M</b> Measurement Aids | 231 |

vi

# **List of Figures**

| 2.1  | Basic components of a $\Delta \Sigma M$ for ADC.                               | 6  |

|------|--------------------------------------------------------------------------------|----|

| 2.2  | Linearizing the quantizer in a $\Delta \Sigma M$                               | 6  |

| 2.3  | STF(z) and $NTF(z)$ for circuit of Example 2.1                                 | 7  |

| 2.4  | Simulated output bit stream power spectrum.                                    | 8  |

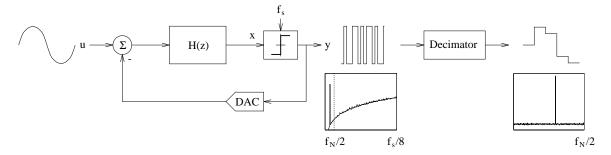

| 2.5  | Complete $\Delta \Sigma M$ ADC block diagram including decimator               | 9  |

| 2.6  | General <i>m</i> th-order low pass $\Delta \Sigma M$ structure                 | 10 |

| 2.7  | Typical radio receiver application for a band pass $\Delta \Sigma M$           | 12 |

| 2.8  | A multistage $\Delta \Sigma \mathbf{M}$                                        | 13 |

| 2.9  | Effect of windowing: (a) unwindowed output spectrum, (b) windowed output spec- |    |

|      | trum                                                                           | 16 |

| 2.10 | Effect of averaging on spectrum variance.                                      | 18 |

| 2.11 | Unwindowed averaged periodogram near dc.                                       | 19 |

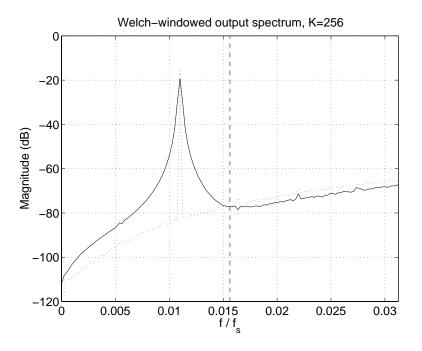

| 2.12 | Hann-windowed averaged periodogram near dc                                     | 21 |

| 2.13 | Welch-windowed averaged periodogram near dc.                                   | 22 |

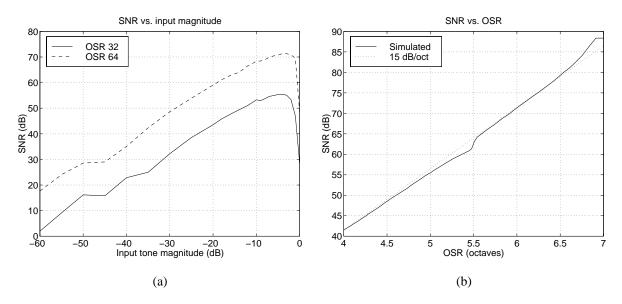

| 2.14 | Performance of ideal double integration $\Delta \Sigma M$                      | 24 |

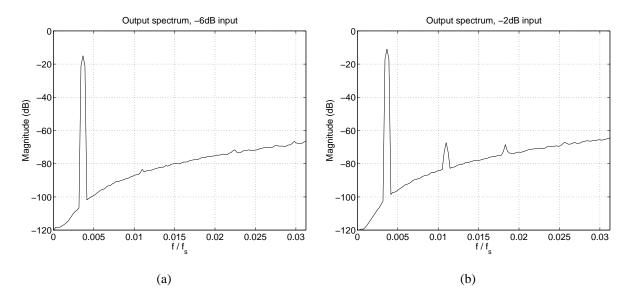

| 2.15 | Increase in baseband harmonics for inputs near full scale: (a) -6dB input, (b) |    |

|      | -2dB input                                                                     | 25 |

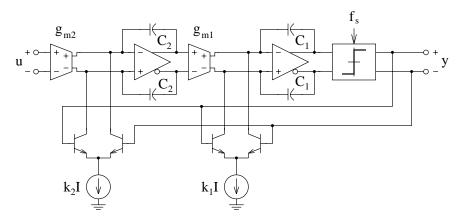

| 2.16 | In P second-order CT $\Delta \Sigma M$ by Jensen et al                         | 25 |

| 2.17 | A general DT $\Delta \Sigma M$ including input prefiltering                    | 28 |

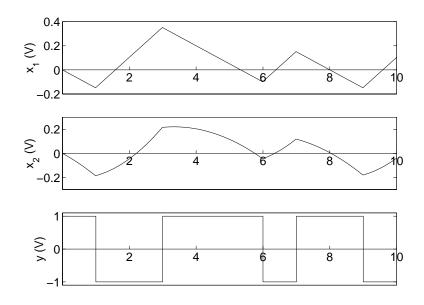

| 3.1  | Typical integrator output and quantizer waveforms.                             | 36 |

| 3.2  | Output spectra using op amps with (a) no slew-rate limiting, (b) slew-rate limiting.          | 37 |

|------|-----------------------------------------------------------------------------------------------|----|

| 3.3  | Ideal vs. real spectra in double integration modulators.                                      | 51 |

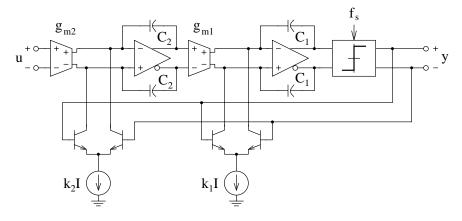

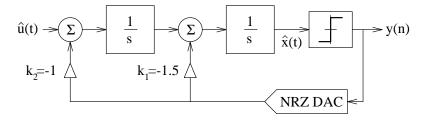

| 4.1  | Example of high-speed double integration CT $\Delta \Sigma M$                                 | 53 |

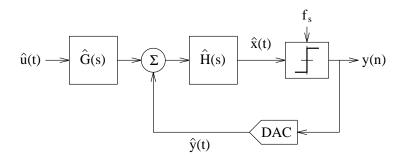

| 4.2  | General CT $\Delta \Sigma M$ block diagram.                                                   | 54 |

| 4.3  | Open-loop CT $\Delta \Sigma M$ and its DT equivalent.                                         | 55 |

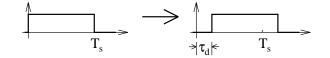

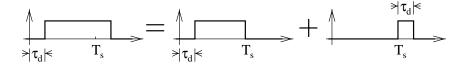

| 4.4  | Illustration of excess loop delay on NRZ DAC pulse.                                           | 59 |

| 4.5  | Delayed NRZ pulse as a linear combination.                                                    | 62 |

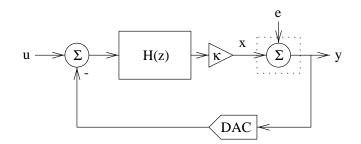

| 4.6  | Linearized $\Delta \Sigma \mathbf{M}$ with one-bit quantizer arbitrary gain $\kappa$ .        | 64 |

| 4.7  | Effect of loop delay on root locus of $NTF(z, \tau_d)$                                        | 65 |

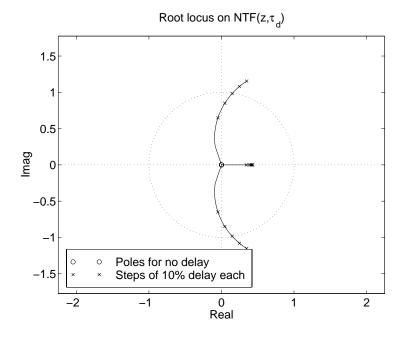

| 4.8  | (a) Output spectrum from double integration CT $\Delta\Sigma M$ (b) in-band noise for zero    |    |

|      | input as a function of loop delay                                                             | 66 |

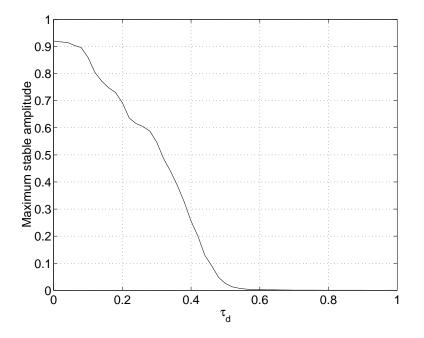

| 4.9  | Maxmimum stable amplitude for double integration CT $\Delta \Sigma M. \ldots \ldots \ldots$   | 67 |

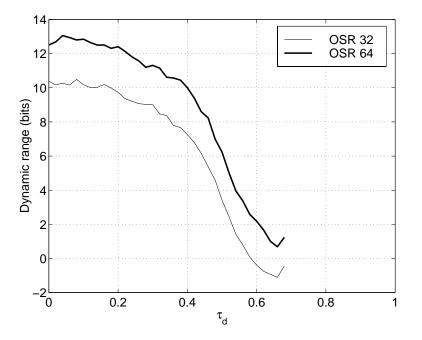

| 4.10 | Dynamic range for double integration CT $\Delta \Sigma M$                                     | 68 |

| 4.11 | Block diagram for LP CT $\Delta \Sigma M$ from Figure 4.1.                                    | 69 |

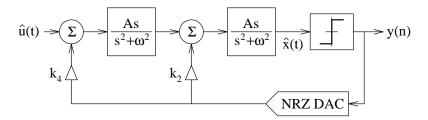

| 4.12 | Block diagram for BP CT $\Delta \Sigma M$ with integrators replaced by resonators that cannot |    |

|      | implement desired equivalent $H(z)$                                                           | 69 |

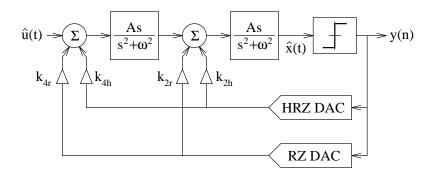

| 4.13 | Multi-feedback BP CT $\Delta \Sigma M$ architecture                                           | 70 |

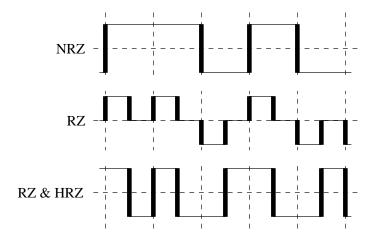

| 4.14 | Common DAC pulse types.                                                                       | 70 |

| 4.15 | ECL-style latched comparator with preamplification for enhanced resolution at                 |    |

|      | high speed. For an NRZ comparator, connect the final differential pair via the                |    |

|      | dashed lines; for RZ, connect the dotted lines instead                                        | 71 |

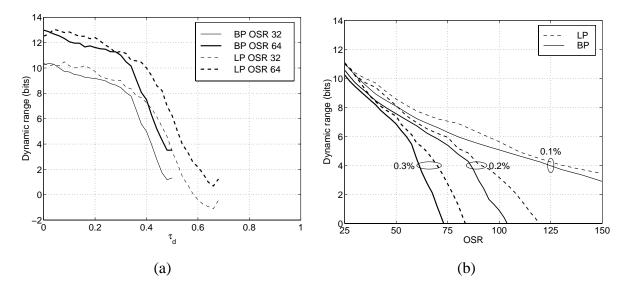

| 4.16 | (a) Dynamic range for multi-feedback BP CT $\Delta \Sigma M$ , with comparison to double      |    |

|      | integration results. (b) Same graph with OSR as independent variable; numbers on              |    |

|      | curves are $\tau_d \times f_N$                                                                | 72 |

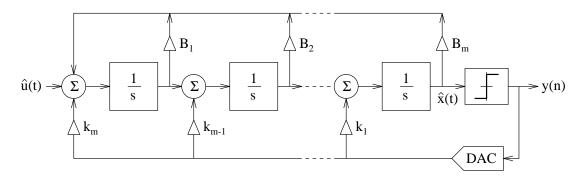

| 4.17 | Block diagram for general high-order LP CT $\Delta \Sigma M$                                  | 73 |

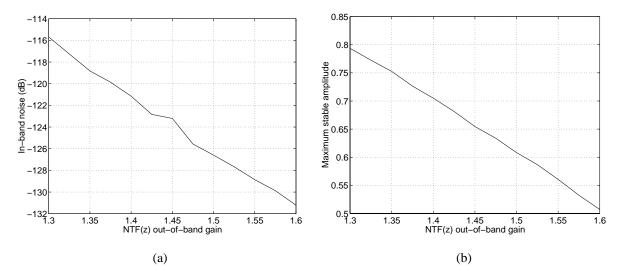

| 4.18 | Effect of out-of-band-gain on fifth-order Chebyshev modulator: (a) IBN, (b) MSA.              | 74 |

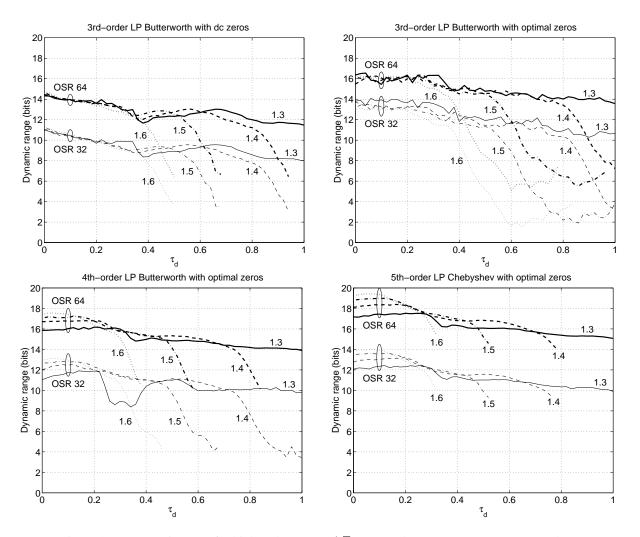

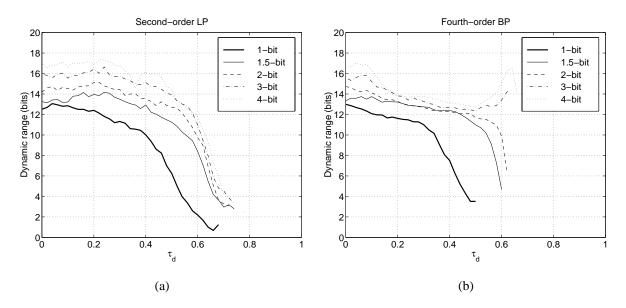

| 4.19 | Dynamic range for high-order LP CT $\Delta\Sigma Ms.$ Numbers on curves are OOBG values.      | 75 |

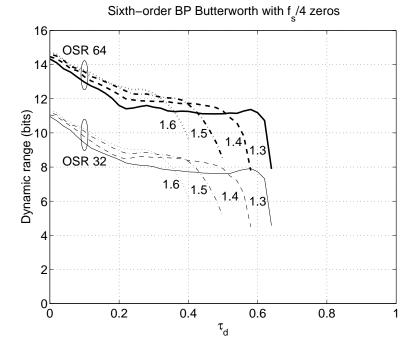

| 4.20 | Dynamic range for sixth-order BP CT $\Delta \Sigma M$ . Numbers on curves are OOBG values.    | 76 |

|      |                                                                                               |    |

| 4.21 | Modulators with multibit quantizers: (a) second-order LP, (b) fourth-order BP $77$                       |

|------|----------------------------------------------------------------------------------------------------------|

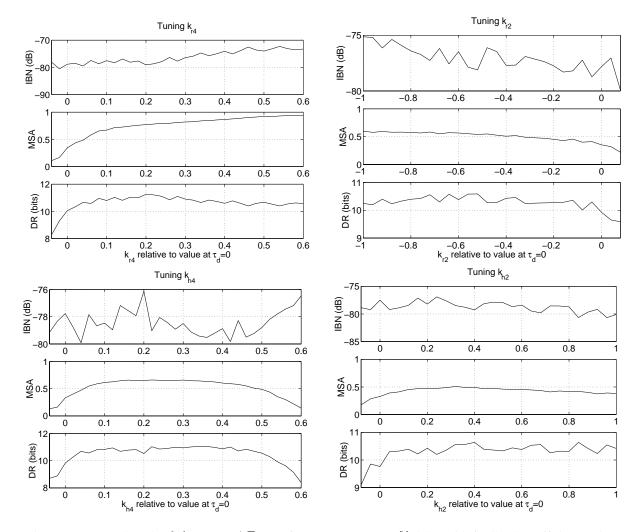

| 4.22 | Fourth-order $f_s/4$ BP CT $\Delta\Sigma M$ performance at $\rho_d = 35\%$ delay with feedback           |

|      | coefficient tuning                                                                                       |

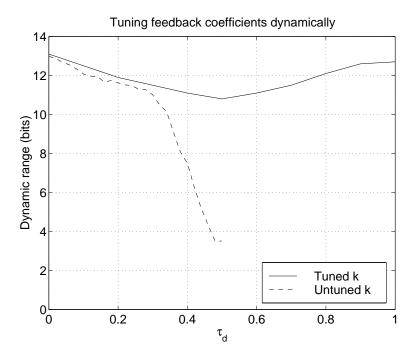

| 4.23 | Multi-feedback BP modulator dynamic range with $k$ tuning                                                |

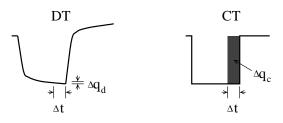

| 5.1  | Clock jitter effect in DT vs. CT design                                                                  |

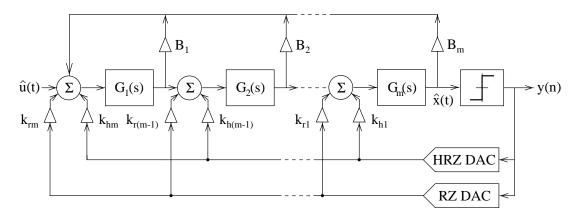

| 5.2  | Block diagram for general CT $\Delta \Sigma M$ architecture                                              |

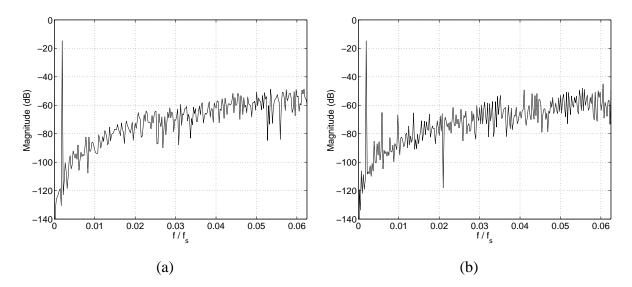

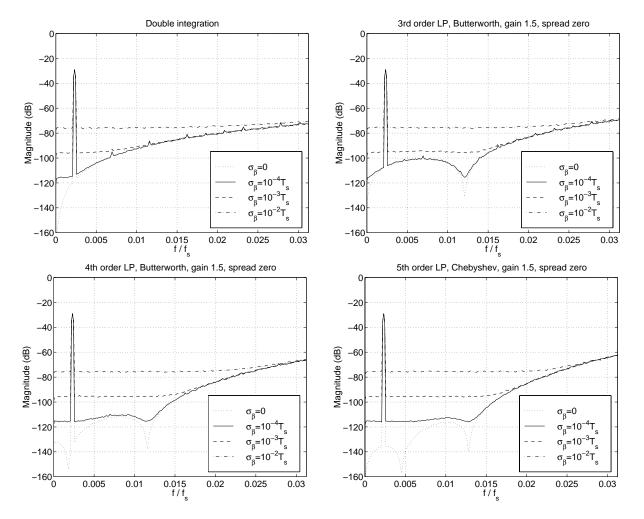

| 5.3  | Output spectra for NRZ LP modulators with clock jitter                                                   |

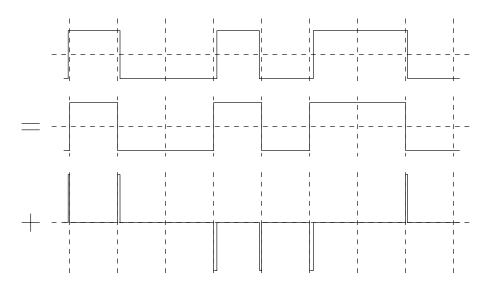

| 5.4  | Equivalent representations of a jittered bit stream                                                      |

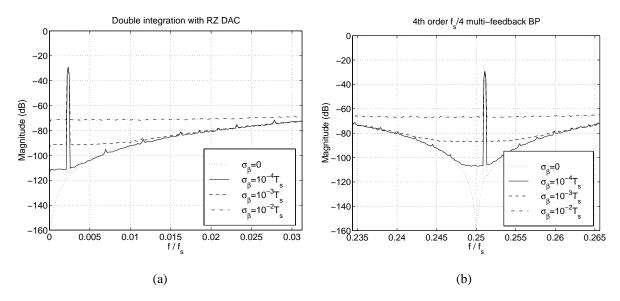

| 5.5  | Output spectra for (a) LP RZ and (b) BP RZ/HRZ modulators                                                |

| 5.6  | Error sequence energy in different types of modulator                                                    |

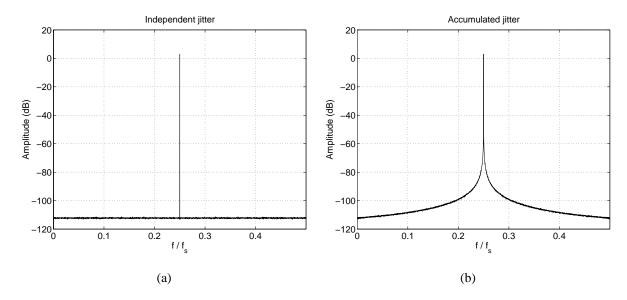

| 5.7  | Unwindowed spectra of sine wave carriers sampled with jitter: (a) independent                            |

|      | jitter, (b) accumulated jitter                                                                           |

| 5.8  | Phase noise plot for accumulated jitter sampling of sine wave                                            |

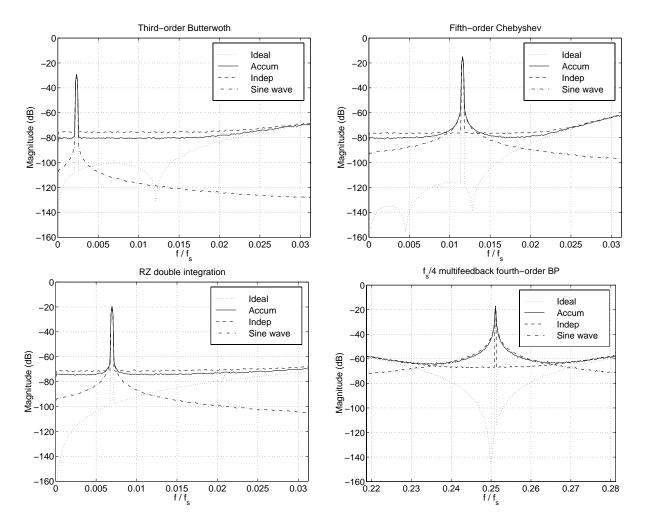

| 5.9  | Comparison of $\Delta \Sigma M$ spectra for independent and accumulated jitter, including                |

|      | spectrum of single tone at output of jittered S/H                                                        |

| 6.1  | Typical output spectra for (a) SPICE prototype, (b) C program using the same                             |

|      | parameters                                                                                               |

| 6.2  | Examples of z-domain extraction from SPICE data                                                          |

| 6.3  | First and second integrator output waveforms from SPICE showing additional ex-                           |

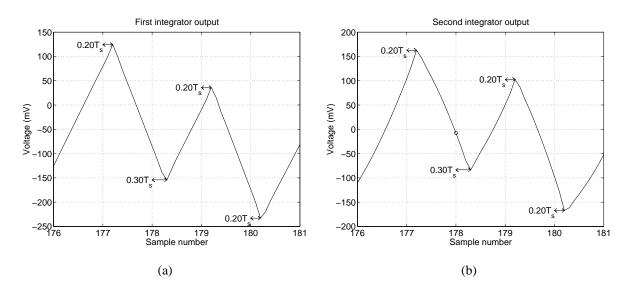

|      | cess delay at sample 178                                                                                 |

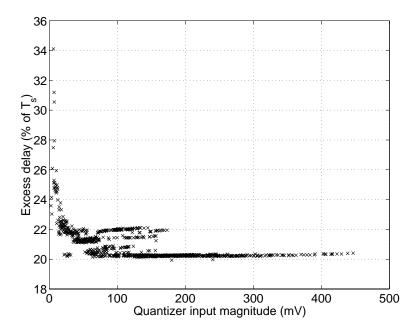

| 6.4  | Effect of finite quantizer gain on excess loop delay                                                     |

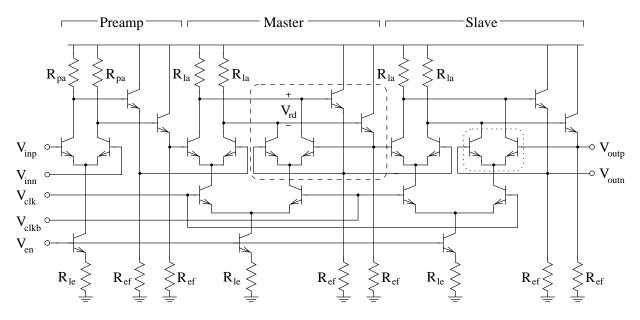

| 6.5  | Typical high-speed CT $\Delta\Sigma {\rm M}$ master-slave latched comparator with preamplifier.<br>. 114 |

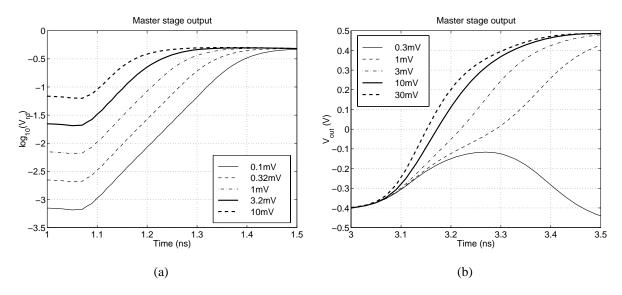

| 6.6  | Output of (a) master stage, (b) slave stage                                                              |

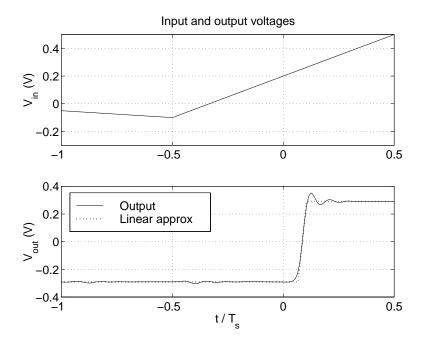

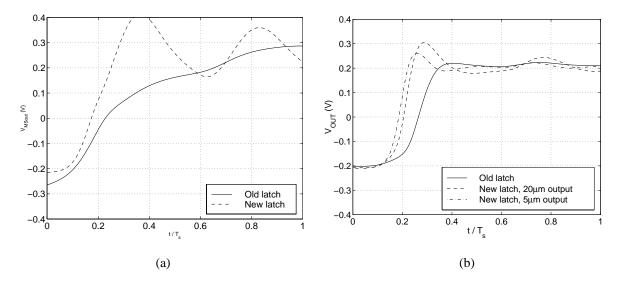

| 6.7  | SPICE input and output waveforms with linear approximation to output                                     |

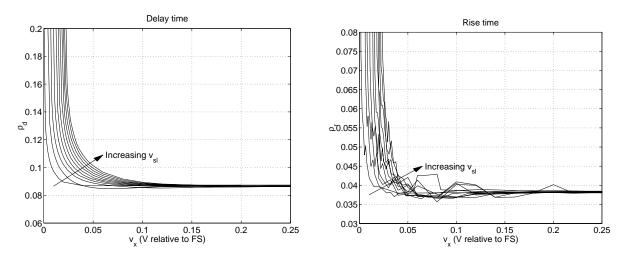

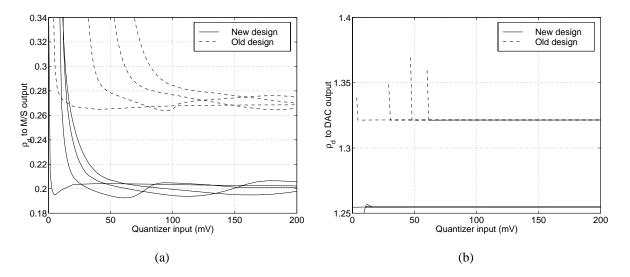

| 6.8  | Example of numerically-characterized $\rho_d$ and $\rho_r$ values                                        |

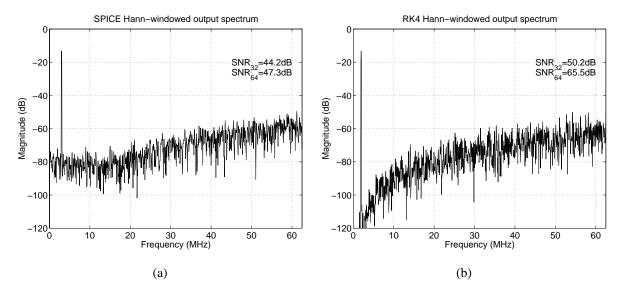

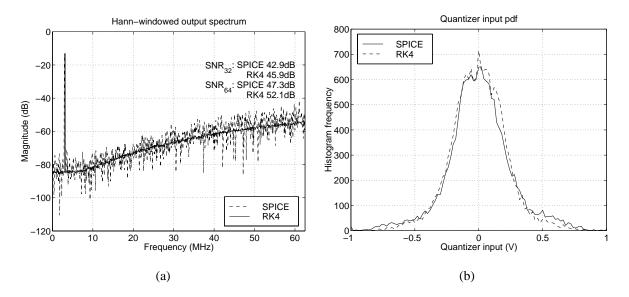

| 6.9  | Comparison of SPICE and Runge-Kutta simulation programs: (a) output spectra,                             |

|      | (b) quantizer input pdfs                                                                                 |

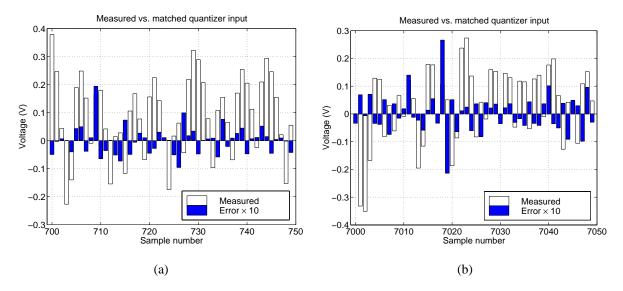

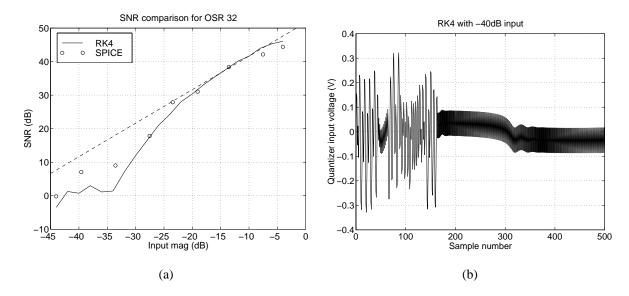

| 6.10       | Comparison of SPICE and Runge-Kutta simulation programs: (a) dynamic range                                 |

|------------|------------------------------------------------------------------------------------------------------------|

|            | plot, (b) quantizer input limit cycle for low magnitude input                                              |

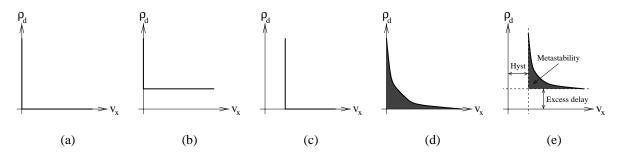

| 6.11       | Quantizer characteristics: (a) ideal, (b) excess delay, (c) hysteresis, (d) metastabil-                    |

|            | ity, (e) practical. Metastability severity is proportional to the area of the shaded                       |

|            | region                                                                                                     |

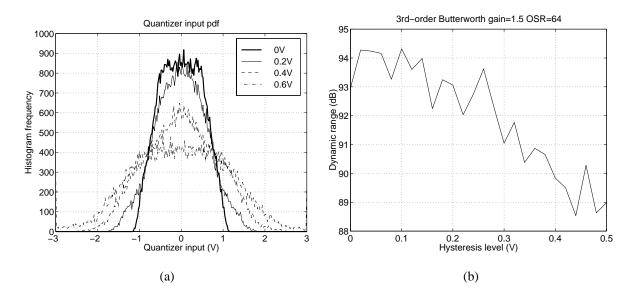

| 6.12       | Quantizer hysteresis in third-order Butterworth modulator: (a) quantizer input pdf,                        |

|            | (b) modulator dynamic range                                                                                |

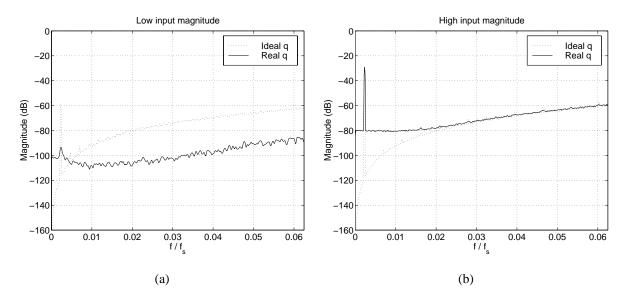

| 6.13       | Typical output spectra from double integration $\Delta \Sigma M$ with a real quantizer: (a) low            |

|            | input amplitude, (b) high input amplitude                                                                  |

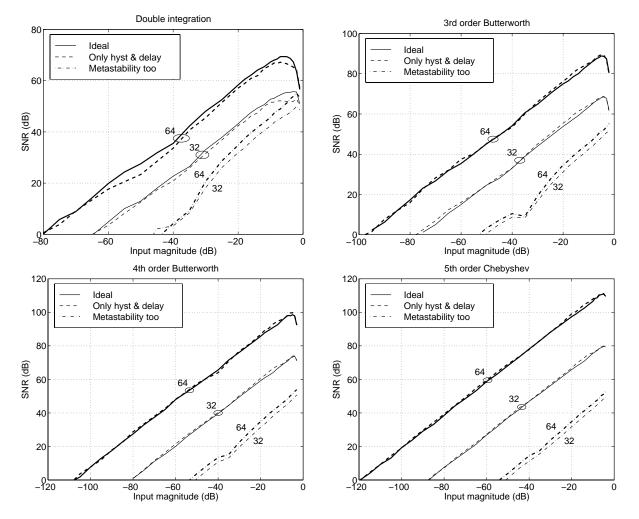

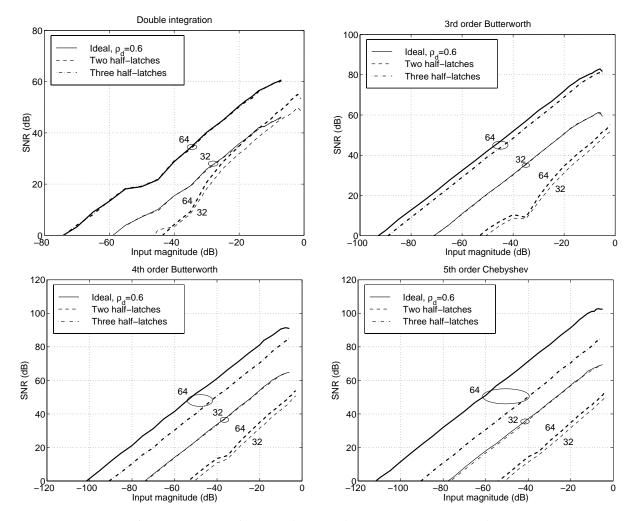

| 6.14       | Dynamic range plots. Numbers on curves are OSR values                                                      |

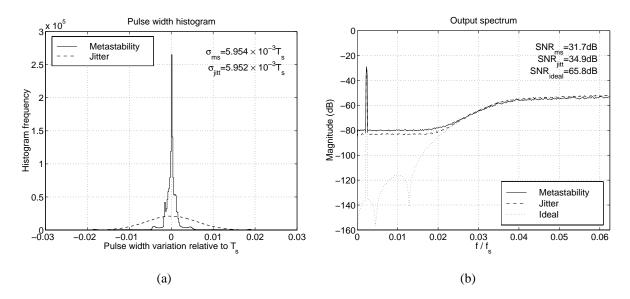

| 6.15       | Comparison of clock jitter to quantizer metastability: (a) DAC pulse width varia-                          |

|            | tion histogram, (b) output spectrum                                                                        |

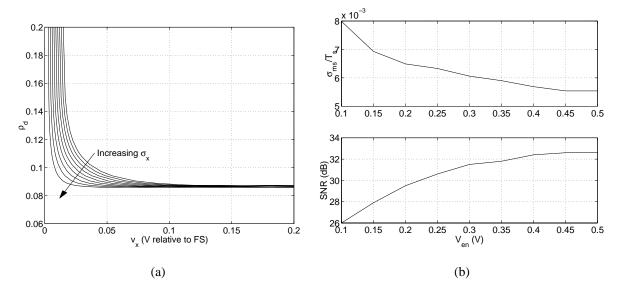

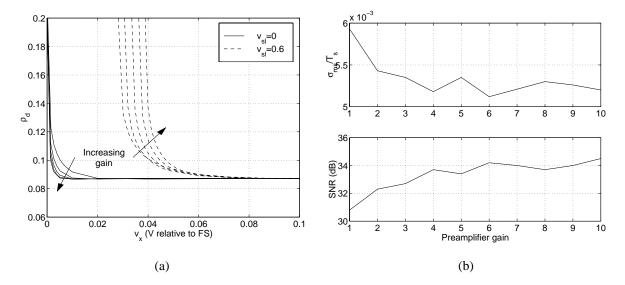

| 6.16       | (a) Quantizer metastability curves and (b) modulator performance as a function of                          |

|            | $\sigma_x$                                                                                                 |

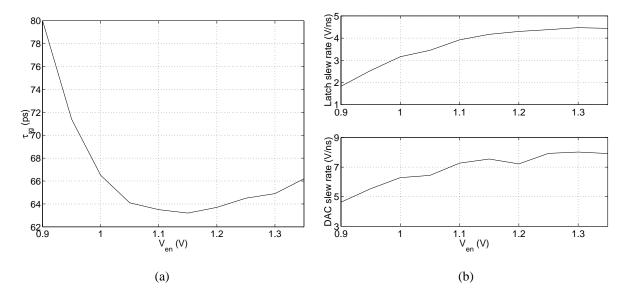

| 6.17       | Effect of $V_{en}$ on (a) regeneration time, (b) slew rates at latch output and DAC output.129             |

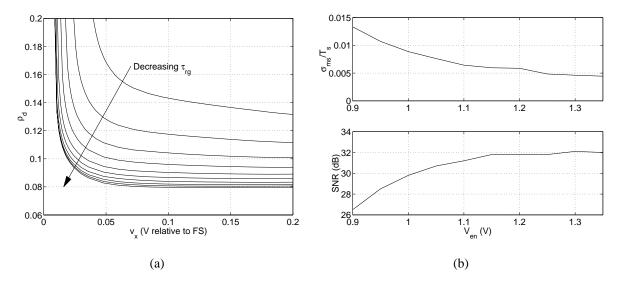

| 6.18       | (a) Quantizer metastability curves and (b) modulator performance as a function of                          |

|            | $	au_{rg}$                                                                                                 |

| 6.19       | (a) Quantizer metastability curves and (b) modulator performance as a function of                          |

|            | preamplifier gain                                                                                          |

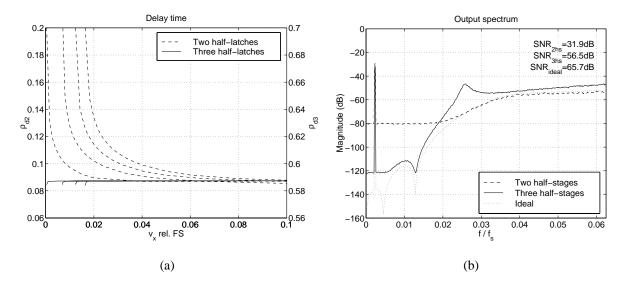

| 6.20       | (a) Quantizer metastability curves and (b) output spectrum for quantizer with an                           |

|            | additional latching stage                                                                                  |

| 6.21       | Dynamic range plots. Numbers on curves are OSR values                                                      |

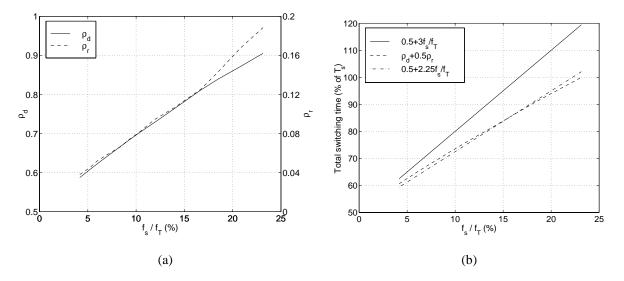

| 6.22       | (a) Effect of increasing $f_s$ on $\rho_d$ and $\rho_r$ , (b) theoretical vs. measured switching time. 137 |

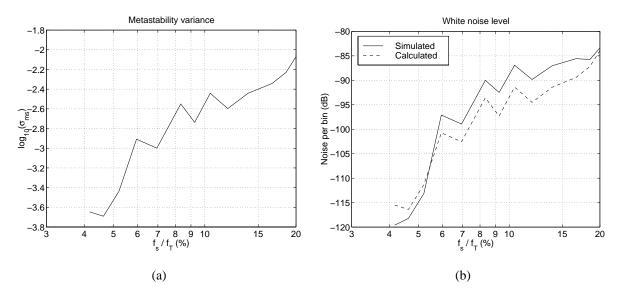

| 6.23       | Effect of increasing $f_s$ on (a) $\sigma_{ms}$ , (b) calculated and simulated noise level 138             |

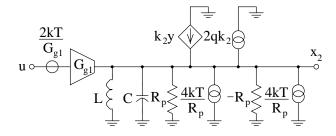

| 7.1        | A 4GHz fourth-order BP CT $\Delta \Sigma M$                                                                |

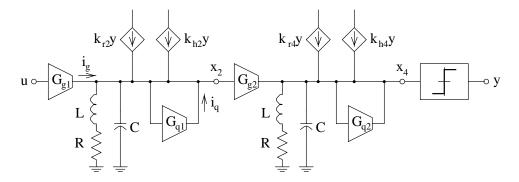

| 7.2        | Approximate single-ended model for modulator                                                               |

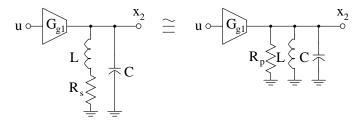

| 7.2        | Series/parallel tank equivalence near resonance                                                            |

| 7.3<br>7.4 | Input transconductor equivalent circuit for noise considerations                                           |

| /.+        | input transconductor equivalent encurt for noise considerations                                            |

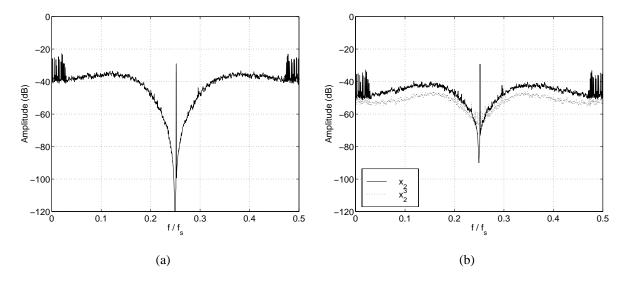

| 7.5  | Spectrum of (a) output bits, (b) $x_2$ and $x_2^3$                                                                                                     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

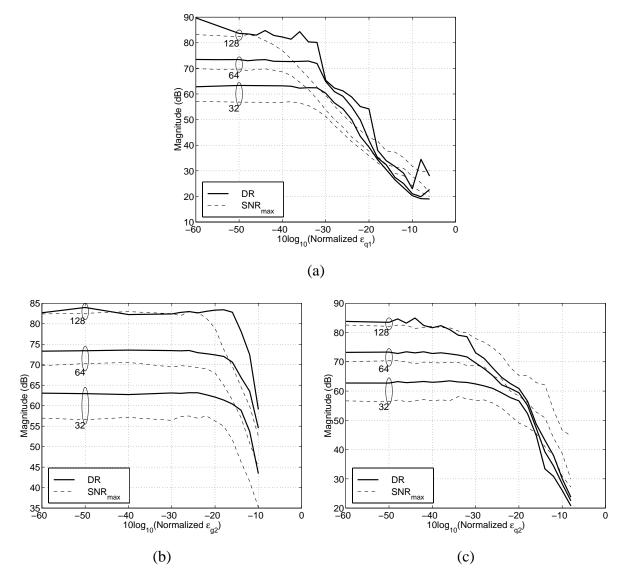

| 7.6  | DR and SNR <sub>max</sub> for (a) $\bar{\epsilon}_{q1}$ , (b) $\bar{\epsilon}_{g2}$ , (c) $\bar{\epsilon}_{q2}$ . Numbers on curves are OSR values 151 |

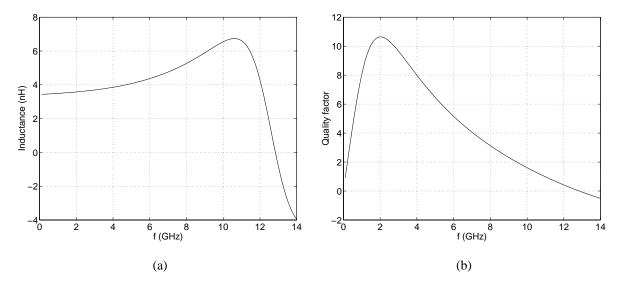

| 7.7  | SPICE ac analysis of inductor: (a) $L$ , (b) $Q$                                                                                                       |

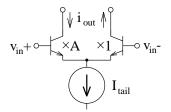

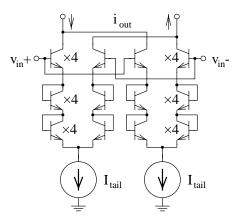

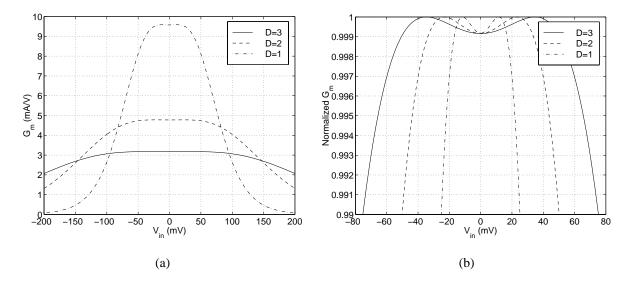

| 7.8  | Differential pair transconductor                                                                                                                       |

| 7.9  | Transconductance of differential pair as a function of (a) tail current, (b) number                                                                    |

|      | of transistors                                                                                                                                         |

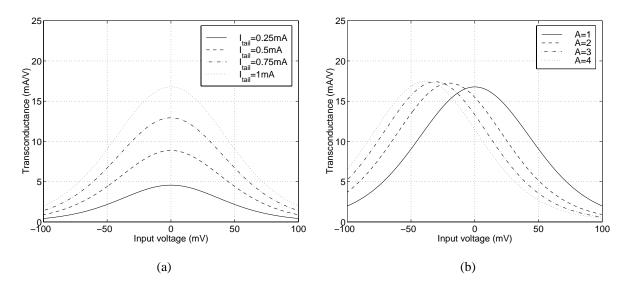

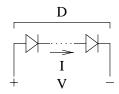

| 7.10 | Multi-tanh circuit                                                                                                                                     |

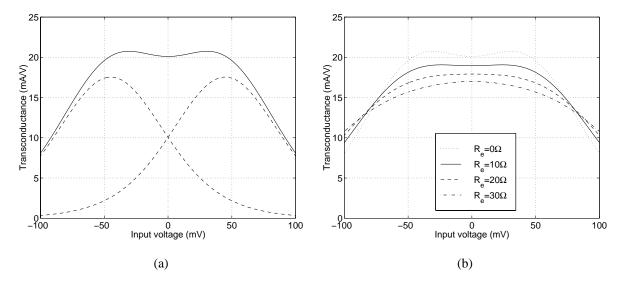

| 7.11 | (a) Multi-tanh $G_m$ characteristic, (b) effect of varying $R_e$                                                                                       |

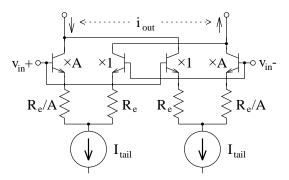

| 7.12 | Actual transconductance topology used                                                                                                                  |

| 7.13 | Transconductance as a function of number of diodes: (a) absolute, (b) normalized                                                                       |

|      | to peak $G_g$                                                                                                                                          |

| 7.14 | Series-connected diodes                                                                                                                                |

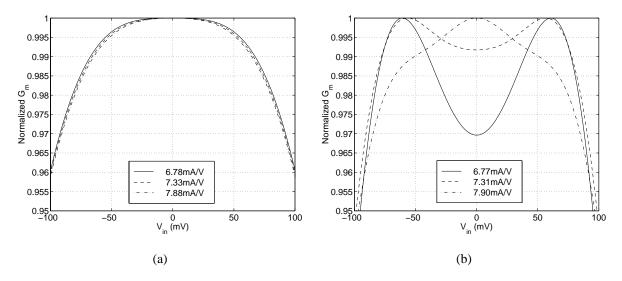

| 7.15 | Linearity for emitter diodes vs. emitter resistors: (a) $A = 4$ , $D = 3$ , (b) $A = 8$ ,                                                              |

|      | $R_e = 100\Omega.  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                    |

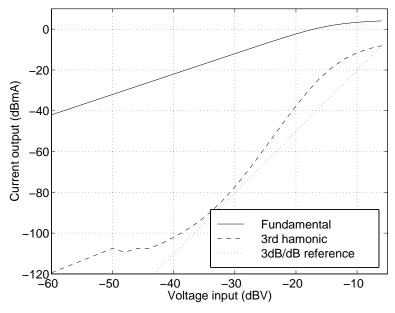

| 7.16 | Linearity plot for a multi-tanh circuit                                                                                                                |

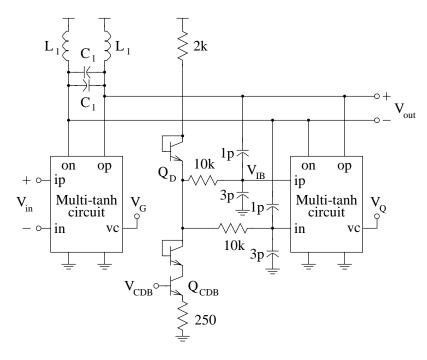

| 7.17 | Band pass resonator block                                                                                                                              |

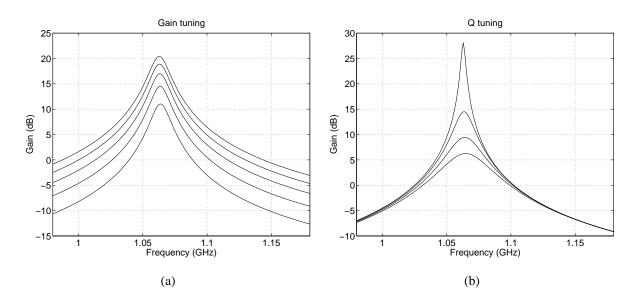

| 7.18 | Filter gain characteristic: (a) fixed $V_Q = 2.6$ V, stepping $V_G$ by 0.2V from 2.0V to                                                               |

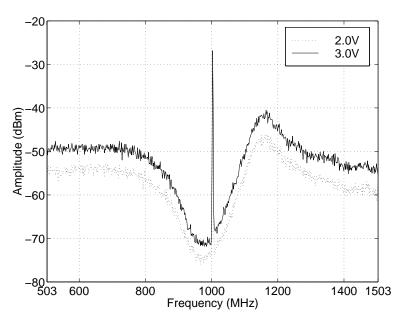

|      | 2.8V, (b) fixed $V_G = 2.2$ V, stepping $V_Q$ by 0.1V vrom 2.4V to 2.7V                                                                                |

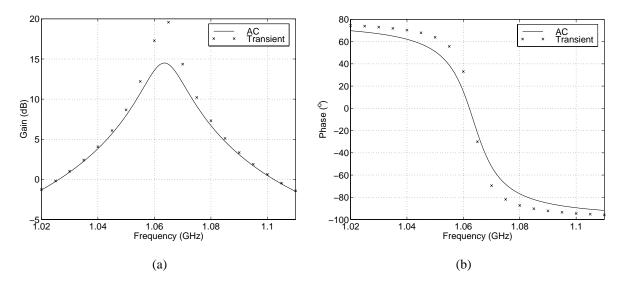

| 7.19 | Transient analysis for $V_G = 2.2$ V and $V_Q = 2.6$ V: (a) gain, (b) phase                                                                            |

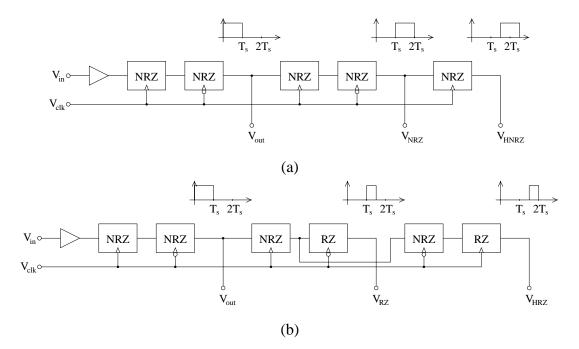

| 7.20 | Overall latching scheme and waveforms: (a) NRZ modulator, (b) RZ modulator 166                                                                         |

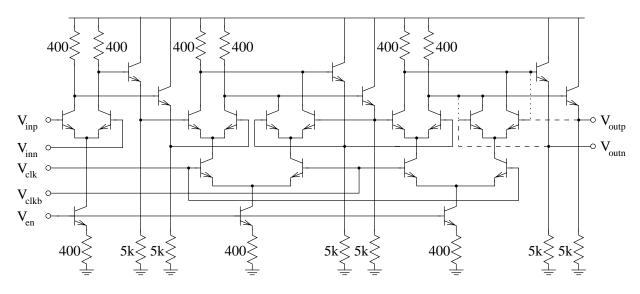

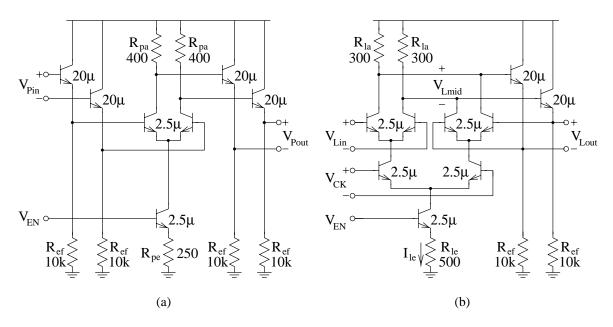

| 7.21 | Schematics for (a) preamplifier, (b) half-latch                                                                                                        |

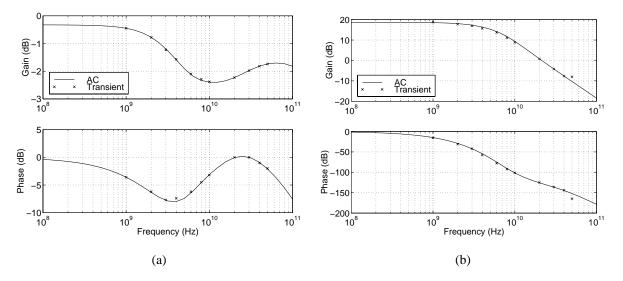

| 7.22 | Original preamp ac analyses: (a) input follower, (b) entire circuit                                                                                    |

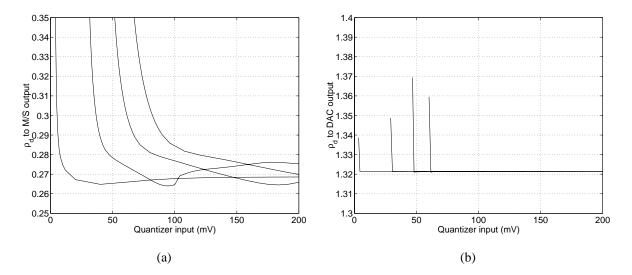

| 7.23 | ZCT characteristics for (a) M/S latch output, (b) one-sample delayed output 169                                                                        |

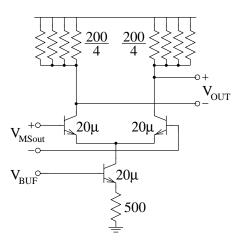

| 7.24 | Modulator output buffer                                                                                                                                |

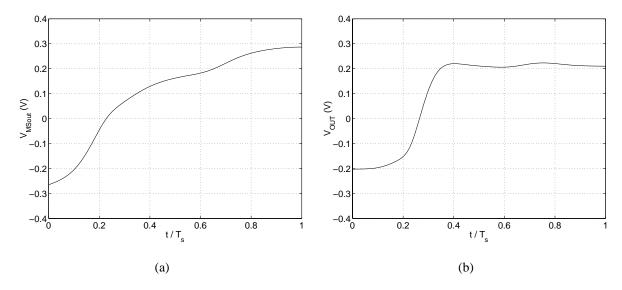

| 7.25 | Output waveforms: (a) M/S latch, (b) output buffer                                                                                                     |

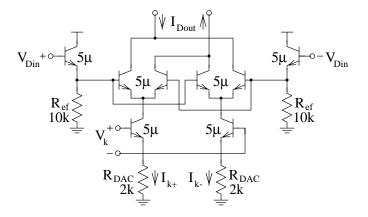

| 7.26 | Current-steering DAC schematic                                                                                                                         |

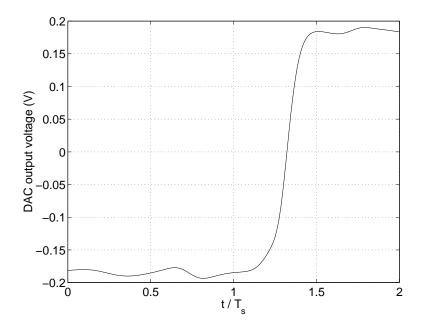

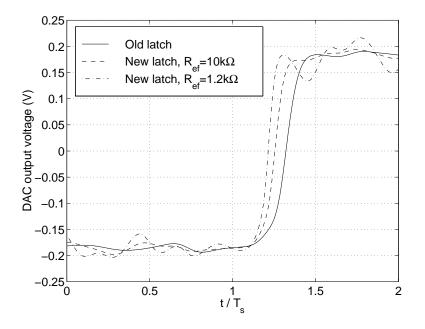

| 7.27 | Dynamic DAC output voltage                                                                                                                             |

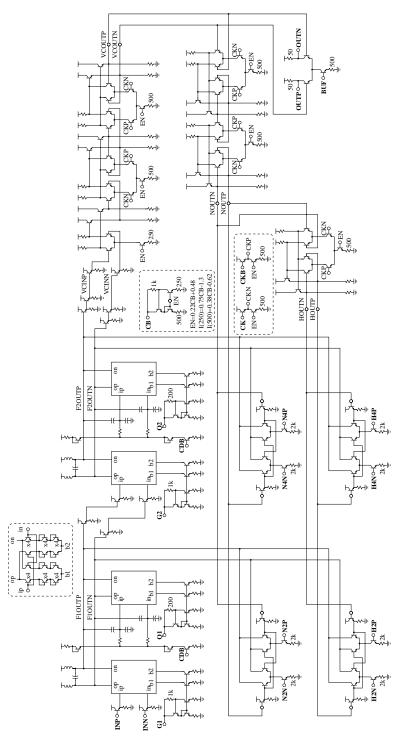

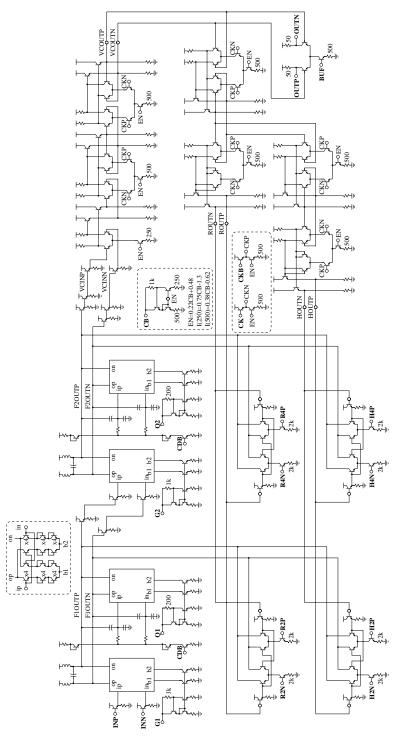

| 7.28 | Complete NRZ $\Delta \Sigma M$ schematic                                                                                                               |

| 7.29 | Complete RZ $\Delta \Sigma M$ schematic                                                |

|------|----------------------------------------------------------------------------------------|

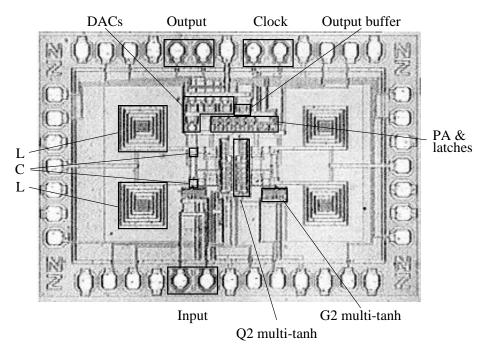

| 7.30 | Die photomicrograph of NRZ modulator                                                   |

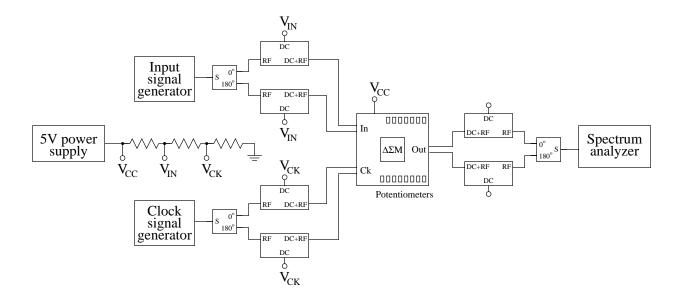

| 7.31 | Measurement test setup                                                                 |

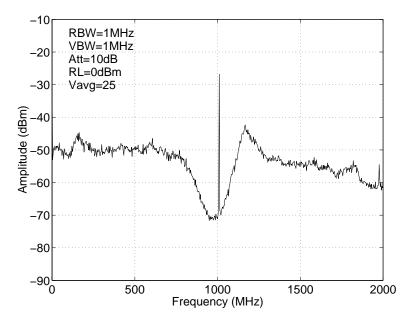

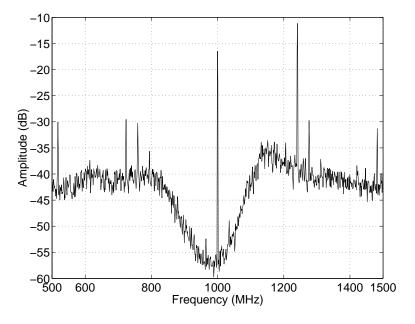

| 7.32 | NRZ modulator output spectrum                                                          |

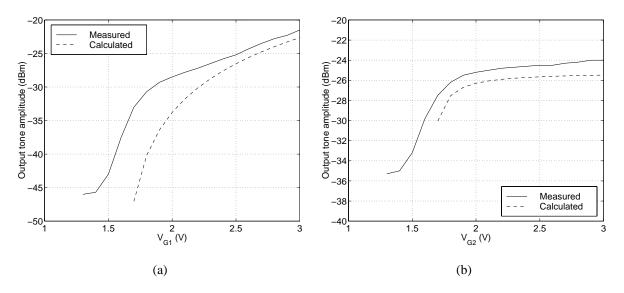

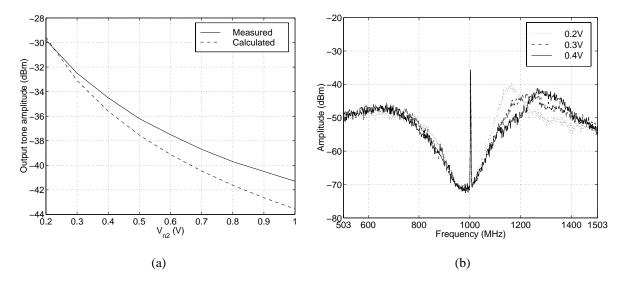

| 7.33 | Tone magnitude in output spectrum against (a) $V_{G1}$ , (b) $V_{G2}$                  |

| 7.34 | (a) Loss of noise shaping for small input and low $Q$ , (b) minimum-detectable input   |

|      | amplitude against $V_Q$                                                                |

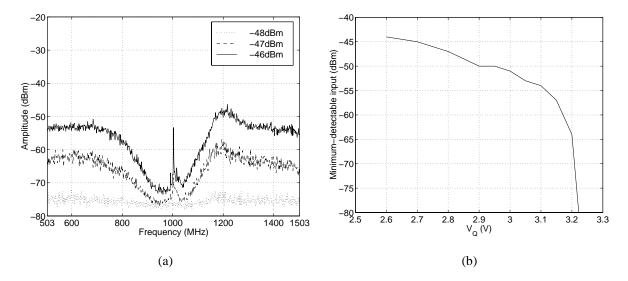

| 7.35 | Oscillation in output spectrum: (a) $V_Q = 3.31$ V, (b) $V_Q = 3.33$ V                 |

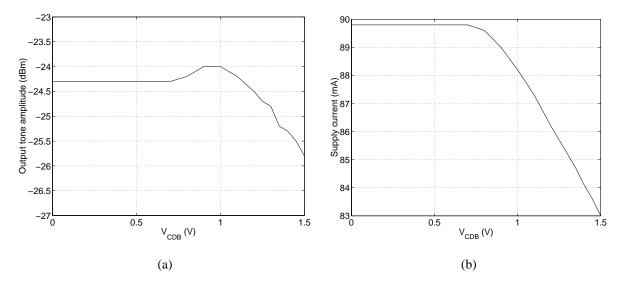

| 7.36 | Effect of $V_{CDB}$ on (a) linearity, (b) supply current                               |

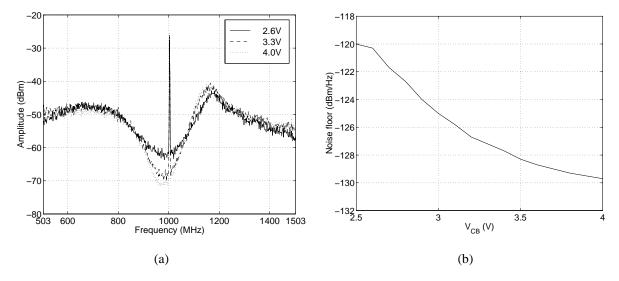

| 7.37 | Changing $V_{CB}$ : (a) overall spectrum, (b) in-band noise                            |

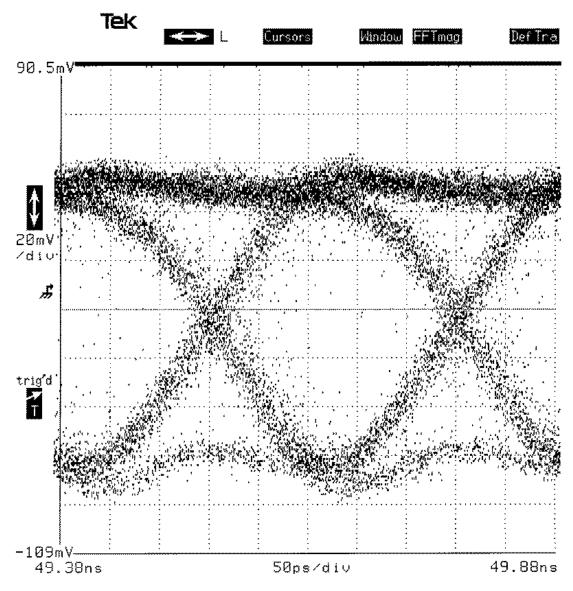

| 7.38 | Output bit stream eye diagram                                                          |

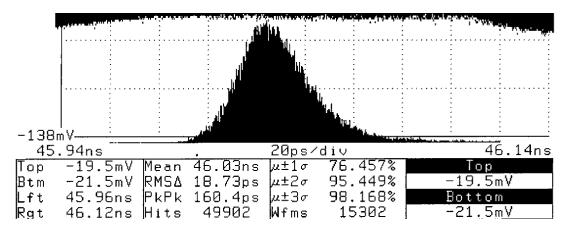

| 7.39 | Histogram of time-domain output bit zero crossings                                     |

| 7.40 | Output spectrum of captured bit stream                                                 |

| 7.41 | Varying $V_{BUF}$                                                                      |

| 7.42 | Changing $V_{n2}$ : (a) tone magnitude at output, (b) overall spectrum                 |

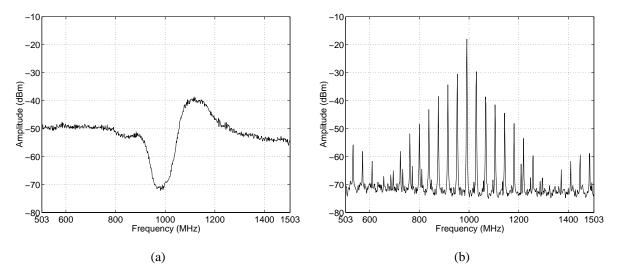

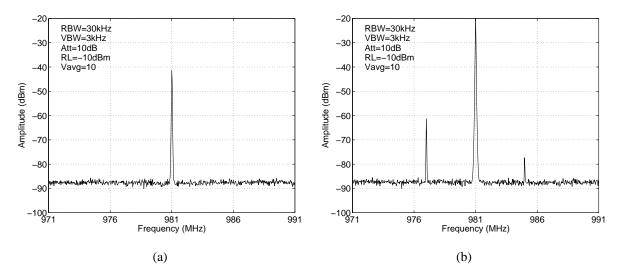

| 7.43 | Measured modulator spectra: (a) $V_{in} = -40$ dBm, (b) $V_{in} = -20$ dBm             |

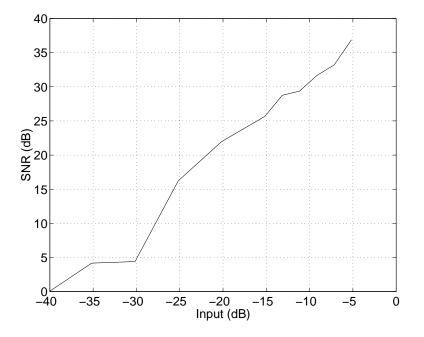

| 7.44 | Dynamic range plot for NRZ modulator in 20MHz bandwidth                                |

| 7.45 | Illustration of nonuniform feedback caused by a half-delayed NRZ DAC 191               |

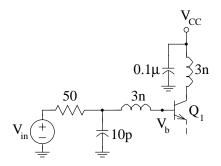

| 7.46 | Model of actual circuit input                                                          |

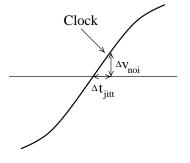

| 7.47 | Clock jitter caused by circuit noise                                                   |

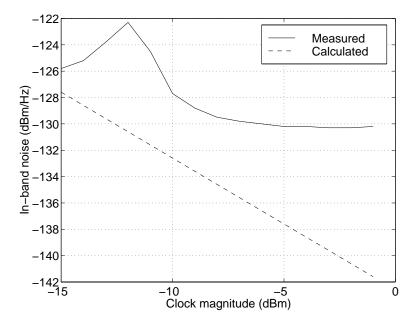

| 7.48 | Measured in-band noise as a function of clock magnitude                                |

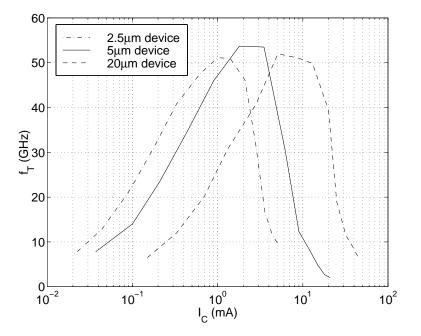

| 7.49 | Measured $f_T$ vs. $I_C$ curves for SiGe BJTs                                          |

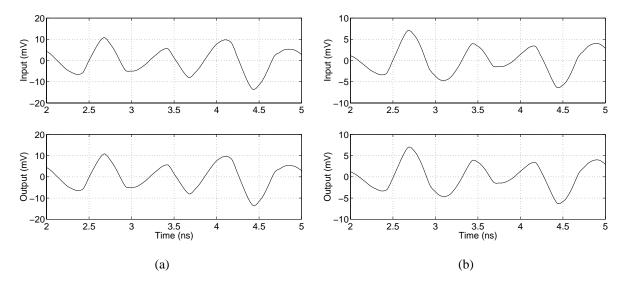

| 7.50 | (a) First and (b) second resonator output buffer waveforms                             |

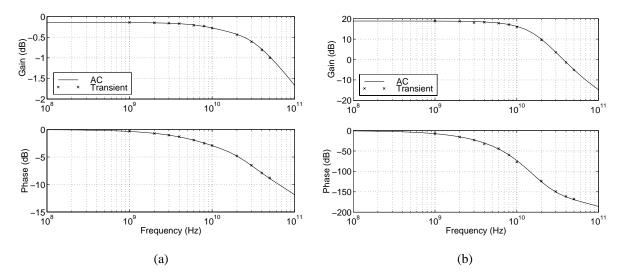

| 7.51 | Optimized preamp ac analyses: (a) input follower, (b) entire circuit                   |

| 7.52 | Output waveforms: (a) M/S latch, (b) output buffer                                     |

| 7.53 | Dynamic DAC output voltage                                                             |

| 7.54 | New ZCT characteristics for (a) M/S latch output, (b) one-sample delayed output 200 $$ |

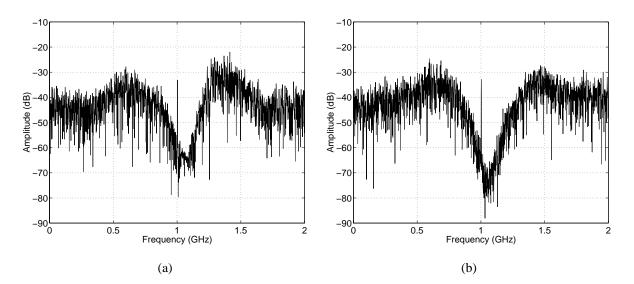

| 7.55 | SPICE output spectra for (a) original modulator, (b) optimized modulator 200           |

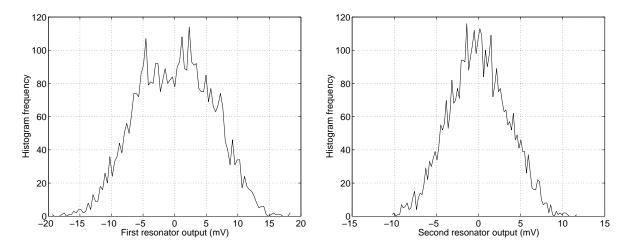

| 7.56        | Resonator output voltage histograms from SPICE                                          |

|-------------|-----------------------------------------------------------------------------------------|

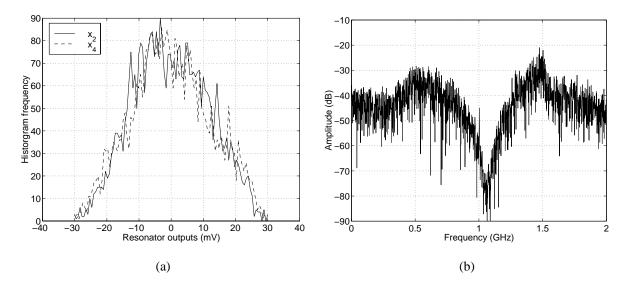

| 7.57        | Scaled DAC currents $k_{n2} = k_{n4} = 500 \mu$ A: (a) resonator output histograms, (b) |

|             | output spectrum                                                                         |

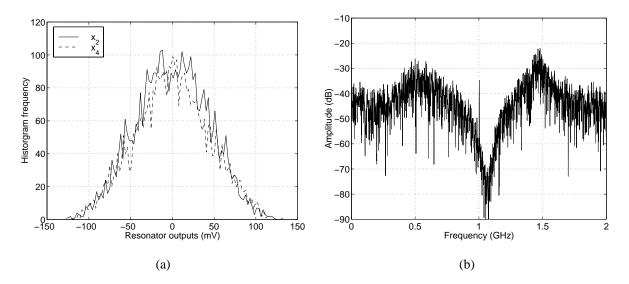

| 7.58        | Scaled DAC currents $k_{n2} = k_{n4} = 1.8$ mA: (a) resonator output histograms, (b)    |

|             | output spectrum                                                                         |

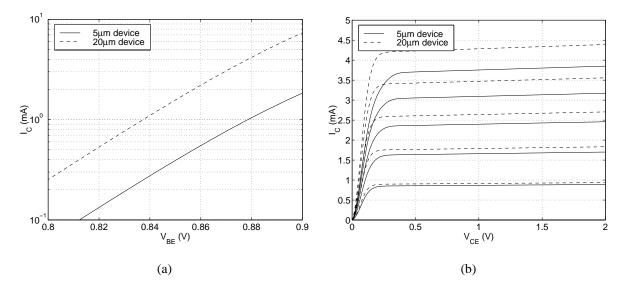

| <b>B</b> .1 | BJT characteristics: collector current vs. (a) $V_{BE}$ , (b) $V_{CE}$                  |

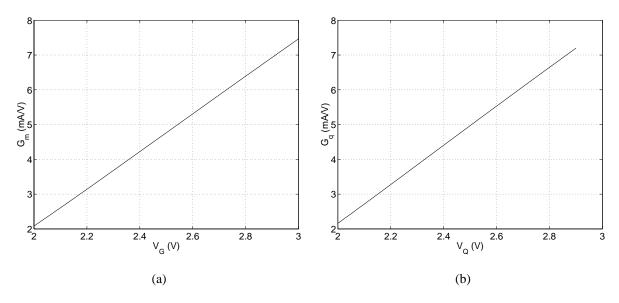

| B.2         | (a) $G_g$ against $V_G$ , (b) $G_q$ against $V_Q$                                       |

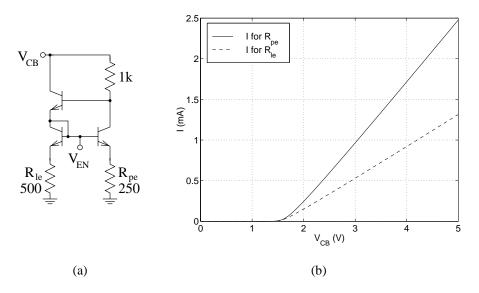

| B.3         | (a) $V_{EN}$ bias circuit, (b) current through bias transistor emitter resistors        |

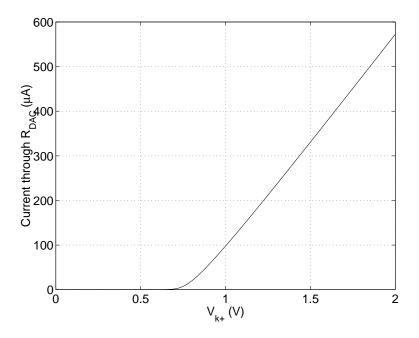

| <b>B.</b> 4 | DAC current vs. control voltage                                                         |

xiv

## **List of Tables**

| 2.1 | Comparison of SNR calculation methods. Including the bin at $f_s/(2 \cdot \text{OSR})$ lowers |     |  |

|-----|-----------------------------------------------------------------------------------------------|-----|--|

|     | SNR by 0.3dB, while trying to account for the tone bin lowers it further by 0.1dB             | 20  |  |

| 3.1 | High-speed CT $\Delta \Sigma$ M published performance                                         | 49  |  |

| 3.2 | Performance in published double integration $CT\Delta\Sigma Ms$ relative to ideal simulation. | 50  |  |

| 4.1 | s-domain equivalences for z-domain loop filter poles.                                         | 58  |  |

| 4.2 | z-domain equivalences for s-domain loop filter poles.                                         | 61  |  |

| 5.1 | Simulated and calculated LP NRZ modulator performance for $\sigma_{\beta} = 10^{-2}T_s$ in    |     |  |

|     | Figure 5.3                                                                                    | 96  |  |

| 5.2 | Performance effects of real VCO clocking on practical modulators                              | 104 |  |

| 6.1 | Performance of LP modulators with two- and three-half latches against ideal 1                 | 133 |  |

| 7.1 | Parameters for the fourth-order design in this chapter                                        | 153 |  |

| 7.2 | Comparison of multi-tanh architectures                                                        | 161 |  |

| 7.3 | Comparison of modulators with different feedback currents                                     | 204 |  |

| 7.4 | Modulator performance summary.                                                                | 206 |  |

xvi

## **List of Abbreviations and Symbols**

### Abbreviations

- A/D Analog-to-digital

- ADC Analog-to-digital converter; analog-to-digital conversion

- AGC Automatic gain compensation

- BJT Bipolar junction transistor

- BP Band pass

- BV<sub>CEO</sub> Collector-emitter breakdown voltage with base open

- CM Common-mode

- CT Continuous time

- DAC Digital-to-analog converter

- DEM Dynamic element matching

- DFT Discrete Fourier transform

- DNL Differential nonlinearity

- DPW DAC pulse width

- DR Dynamic range

- $\Delta \Sigma M$  Delta-sigma modulator; delta-sigma modulation

- DSP Digital signal processing

- DT Discrete time

#### xviii

- ECL Emitter-coupled logic

- FFT Fast Fourier transform

- GB Gain-bandwidth

- HBT Heterojunction bipolar transistor

- HNRZ Half-delayed non-return-to-zero

- HRZ Half-delayed return-to-zero

- IBN In-band noise

- i.i.d. Independent and identically-distributed

- IIP<sub>3</sub> Input third-order intercept point

- INL Integral nonlinearity

- LNA Low-noise amplifier

- LP Low pass

- M/S Master/slave

- MSA Maximum stable amplitude

- NRZ Non-return-to-zero

- NTF Noise transfer function

- OOBG Out-of-band gain

- OSR Oversampling ratio

- pdf Probability distribution function

- RHS Right-hand side

- rms Root mean square

- RK4 Fourth-order Runge-Kutta numerical integration

- RZ Return-to-zero

- SC Switched capacitor

| <b>OLDD</b> | <b>n</b>    | 1 '              |

|-------------|-------------|------------------|

| SFDR        | Sourious_fr | ee dynamic range |

| SIDK        | Spurious-in | ce uynanne range |

|             |             |                  |

- S/H Sample and hold

- SI Switched current

- SiGe Silicon germanium

- SNDR Signal-to-noise-plus-distortion ratio

- SNR Signal-to-noise ratio

- SQNR Signal-to-quantization-noise ratio

- STF Signal transfer function

- VCO Voltage-controlled oscillator

- ZCT Zero-crossing time

### **Roman Symbols**

Equation and figure numbers in the list below refer to equations or figures where an example of the use of the symbol may be seen.

- $a_k$  (2.12) Coefficient of x(n-k)

- A (Figure 7.10) Imbalance of transistors in multi-tanh block

- $A_0$  (3.1) Op amp dc gain

- $A_0$  Resonator center frequency gain

- $A_{clk}$  (7.38) Clock voltage magnitude

- $A_i$  (5.1) Gain of block  $\hat{G}_i(s)$

- *b* Input tone bin number

- $b_k$  (2.12) Coefficient of y(n-k)

- $B_i$  (4.27) Zero-placement feedback coefficients

- $c_k$  (2.12) Coefficient of u(n-k)

- C (2.15) Capacitance

- C (7.13) BP rsonator tank capacitance

- $C_{\mu}$  Base-collector capacitance

- *D* Number of emitter diodes in multi-tanh block

- *e* (Figure 2.2) Quantization noise in linear model

- e(n) (5.11) Jitter-induced error sequence

- E(z) (2.1)  $\mathcal{Z}$ -transform of e

- f Frequency

- $f_c$  (5.21) Carrier frequency

- $f_{max}$  Transistor unity power gain frequency

- $f_n$  (5.22) Offset from  $f_c$  at which phase noise is measured

- $f_N$  (2.4) Nyquist frequency

- $f_s$  (2.4) Sampling frequency

- $f_T$  (4.12) Transistor unity current gain frequency

- $g_m$  (2.15) Transconductance

- G(z) (2.11) DT prefilter transfer function

- $\hat{G}(s)$  (2.14) CT prefilter transfer function

- $G_q$ ,  $G_q$  (7.13) Transconductance of gain and Q-tuning blocks

- $\hat{G}_i(s)$  (5.1) Generalized CT gain block

- h(n) (4.3) DT loop transfer function impulse response

- $\hat{h}(t)$  (4.3) CT loop transfer function impulse response

- H(z) (2.1) DT loop transfer function

- $\hat{H}(s)$  (2.14) CT loop transfer function

- $H(z, \tau_d)$  (4.19) DT loop transfer function of CT  $\hat{H}(s)$  with excess loop delay  $\tau_d$

$I_{Dout}$  (Figure 7.26) DAC output current

- $I_g$  (7.13) Gain transconductor output current

- $I_k$  (7.33) Feedback DAC current

- $I_{le}$  (Figure 7.21(b)) Current through  $R_{le}$

- $I_q$  (7.13) Q-enhancement transconductor output current

- $I_{tail}$  (Figure 7.10) Tail current in multi-tanh block

- *k* Boltzmann's constant

- $k_1, k_2$  (2.15) Second-order LP  $\Delta \Sigma M$  feedback parameters

- $k_2, k_4$  (Figure 7.2) BP modulator feedback parameters

- $k_i$  (4.27) General feedback coefficients

- $k_{h2}, k_{h4}$  (Figure 7.2) HRZ feedback coefficients in BP modulator

- $k_{ni}$  (4.37) NRZ feedback coefficients

- $k_{r2}, k_{r4}$  (Figure 7.2) RZ feedback coefficients in BP modulator

- $\bar{k}_{r2}, \bar{k}_{r4}, \bar{k}_{h2}, \bar{k}_{h4}$  (7.19) Nominal feedback current levels

- $k_{ri}$ ,  $k_{hi}$  (4.26) RZ/HRZ feedback coefficients

- K (Figure 2.10) Number of averaged periodograms

- *l* Loop filter pole multiplicity

- *l* (7.43) Metal length in  $\mu$ m

- L (7.13) BP resonator tank inductance

- $L_{par}$  (7.43) Parasitic metal inductance in nH

- $L_p$  (7.3) Equivalent tank parallel inductance

- $L_s$  (7.3) Equivalent tank series inductance

- m (Figure 2.6) Order of  $\Delta \Sigma M$  loop filter

- n (2.6) Sampling instant number,  $t = nT_s$

- $n_c$  (5.21) VCO phase noise

- $n_t$  (4.12) Number of transistors in feedback path

- N (2.6) Length of output bit sequence

- NTF(z) (2.2) Noise transfer function

- p (3.1) Leaky integration proportionality constant

- $p_x(\alpha)$  (Figure 6.9(b)) pdf of quantizer input voltage

- $\hat{P}(f)$  CT-domain power spectrum

- P(n) (2.7) DT-domain power spectrum,  $n = 0, 1, \dots, N/2$

- $P_n$  (2.9) Total noise power in baseband

- Q Quality factor

- $Q_L$  (7.2) Inductor quality factor

- $Q_{res}$  Resonator quality factor

- $Q_n$  Bipolar transistor n

- R (7.13) Resistance of inductor in resonant tank

- $\hat{r}_D(t)$  (4.3) Time domain feedback DAC impulse response

- $\hat{R}_D(s)$  (4.2) Frequency domain feedback DAC impulse response

- $R_{DAC}$  (Figure 7.26) DAC current-source resistance

- $R_{ef}$  (Figure 7.21) Emitter follower resistance

- $R_{in}$  Input resistance

- $R_{la}$  (Figure 7.21(b)) Latch amplifier load resistance

- $R_{le}$  (Figure 7.21(b)) Latch current-source transistor emitter resistance

- $R_p$  (7.3) Equivalent tank parallel resistance

- $R_{pa}$  (Figure 7.21(a)) Preamp amplifier load resistance

- $R_{par}$  Parasitic metal resistance

xxii

- $R_{pe}$  (Figure 7.21(a)) Preamp current-source transistor emitter resistance

- $R_s$  (7.3) Equivalent tank series resistance

- s Continuous-time frequency variable,  $s = \sigma + j\omega$

- $s_k$  (4.6) kth pole of  $\hat{H}(s)$

- STF(z) (2.2) Signal transfer function

- t Time

- $\Delta t_{jitt}$  (7.39) Time jitter

- $t_n$  (5.4) Time at sample *n* including jitter

- T Absolute emperature

- $T_s$  Sampling period

- u (2.12) DT input to  $\Delta \Sigma M$

- $\hat{u}$  (2.15) CT input to  $\Delta \Sigma M$

- $u_{min}$ ,  $u_{max}$  (7.5), (7.6) Minimum, maximum BP modulator input signals

- U(z) (2.1)  $\mathcal{Z}$ -transform of u

- $\hat{U}(s)$  (2.14) Laplace transform of  $\hat{u}$

- $\overline{v_{nc}}$  (7.41) Clock transistor input-referred noise voltage

- $\overline{v_{nq1}}$  (7.4) Input-referred noise for  $G_{q1}$

- $\Delta v_{noi}$  (7.39) Total clock waveform noise

- $v_{sl}$  Slope of latch input voltage relative to full scale

- $v_x$  Latch input voltage relative to full scale

- $V_{BUF}$  (Figure 7.24) Modulator output swing control voltage

- $V_{CB}$  (Figure B.3(a)) Latch current control voltage

- $V_{CC}$  Power supply voltage

- $V_{CDB}$  (Figure 7.17)  $V_{IB}$  control voltage

- $V_{clk}$  (7.38) Clock voltage waveform

- $V_G$  (Figure 7.17) Voltage to generate  $G_g$

- $V_{h2}$ ,  $V_{h4}$  HNRZ/HRZ DAC control voltages

- $V_{IB}$  (Figure 7.17) Q-tuning multi-tanh block common-mode voltage

- $V_{k+}, V_{k-}$  (Figure 7.26) DAC control voltages

- $V_{Lmid}$  (Figure 7.21(b)) Intermediate latch voltage

- $V_{Lout}$  (Figure 7.21(b)) Latch output voltage

- $V_{n2}$ ,  $V_{n4}$  NRZ DAC control voltages

- $V_{Pin}$  (Figure 7.21(a)) Preamp input voltage

- $V_Q$  (Figure 7.17) Voltage to generate  $G_q$

- $V_{r2}, V_{r4}$  RZ DAC control voltages

- $V_{rd}$  (Figure 6.5) Differential regeneration voltage

- w (7.43) Metal width in  $\mu$ m

- w(n) (2.8) Spectral windowing function

- x (2.12) DT input to quantizer

- $x_2, x_4$  (Figure 7.2) Band pass resonator outputs

- $\hat{x}$  (4.1) CT input to quantizer

- $x_i$  (5.3) Output of gain block  $\hat{G}_i(s)$

- $\hat{x}_1$  (2.15) CT output of first integrator in double integration modulator

- $\hat{x}_2$  (2.15) CT output of second integrator in double integration modulator

- X(z) (2.11)  $\mathcal{Z}$ -transform of x

- $\hat{X}(s)$  (2.14) Laplace transform of  $\hat{x}$

- $X_2$  (7.13) Laplace transform of  $x_2$

- y (2.12) DT output of  $\Delta \Sigma M$

xxiv

- $\hat{y}$  (Figure 4.2) CT output of  $\Delta \Sigma M$

- Y(n) (2.6) DFT of y

- Y(z) (2.1)  $\mathcal{Z}$ -transform of y

- $\hat{Y}(s)$  (2.14) Laplace transform of  $\hat{y}$

- z (2.1) Discrete-time frequency variable,  $z = \exp(sT)$

- $z_k$  (4.6) kth pole of H(z)

### **Greek Symbols**

$(\alpha, \beta)$  (4.4) DAC pulse interval

- $\beta$  Random variable for jitter distribution

- $\beta_n$  (5.4) Jitter at sample n

- $\Delta$  Difference between adjacent quantizer output levels

- $\delta y$  Difference between successive output samples, y(n) y(n-1)

- $\epsilon_{g1}, \epsilon_{g2}$  (7.7) Nonlinearity coefficients of  $G_{g1}, G_{g2}$

- $\bar{\epsilon}_{g2}$  (7.26) Normalized  $\epsilon_{g2}$

- $\epsilon_{q1}, \epsilon_{q2}$  Nonlinearity coefficients of  $G_{q1}, G_{q2}$

- $\bar{\epsilon}_{q1}, \bar{\epsilon}_{q3}$  (7.25), (7.27) Normalized  $\epsilon_{q1}, \epsilon_{q3}$

- $\|\varepsilon\|_2$  (6.5) RMS least-squares matching error

- $\|\varepsilon\|_{\infty}$  (6.5) Maximum least-squares matching error

- $\gamma_k$  (7.21) DAC feedback current scale factor

- $\kappa$  (Figure 4.6) Linearized quantizer gain

- $\rho_d$  (4.11) Excess loop delay as a fraction of  $T_s$ , i.e.,  $\tau_d/T_s$

- $\rho_r$  DAC pulse rise time as a fraction of  $T_s$ , i.e.,  $\tau_r/T_s$

- $\sigma$  Standard deviation

- $\sigma_{\beta}$  (5.12) Standard deviation of  $\beta$

- $\sigma_{\delta y}$  (5.12) Standard deviation of  $\delta y$

- $\sigma_e$  (5.12) Standard deviation of e(n)

- $\sigma_x$  Standard deviation of x(n)

- $\sigma_{x_2}, \sigma_{x_4}$  (7.22) Standard deviation of  $x_2, x_4$

- au Op amp dominant pole time constant

- $\tau_d$  (4.11) Excess loop delay

- $\tau_r$  DAC pulse rise time

- $\tau_{rq}$  Latch regeneration time constant

- $\omega_0$  Center frequency of band pass resonator

- $\omega_i$  (5.2) Center frequency of gain block  $\hat{G}_i(s)$

xxvi

### Chapter 1

### Introduction

### **1.1 Motivation**

The late 1990s will perhaps be remembered as the start of the "system on a chip"-style of design and manufacturing: those engaged in building products for certain markets, cellular radio being a major one, are keen to cut costs and therefore gain a competitive edge by integrating all system functions onto a single substrate with as few external components as possible. This task is made much easier if analog signals, which is how any real-world quantity must inevitably be represented, are converted to digital form for on-chip processing. This helps in two main ways: digital signals are less susceptible to corruption by circuit noise and process variations, and more digital signal processing circuitry can be integrated into the same die area than analog circuitry. Thus, it is clear that analog-to-digital converter (ADC) circuits play an important role in modern integrated systems.

The three main performance measures of an ADC are its resolution (usually number of bits), its speed (how many conversions it does per second), and its power consumption, where customarily it is desired that the first two of these be maximized and the third minimized. There are many different styles of circuit that perform ADC; one particular style that has received a good deal of attention in the last fifteen years is the delta-sigma modulator (DSM or  $\Delta\Sigma M$ ) [Nor97]. These circuits have found their niche in applications requiring very high resolution at low speeds (e.g., 20

bits at 500Hz [Tho94]) and audio converters (16 or more bits at 44kHz [Kwa96]), and they often work with very modest power budgets (2.3mW for an audio coder [vdZ97]). It is fair to say that for high resolution and/or low power at fairly low speeds (up to a few hundred kHz), delta-sigma modulation is the best ADC architecture choice.

The vast majority of  $\Delta\Sigma$ Ms have been built with discrete-time (DT) circuitry, very often switched-capacitor circuits. If circuit waveforms are to be allowed adequate settling time, the speed at which DT circuits are clocked must be restricted. These restrictions can be relaxed by employing continuous-time (CT) circuitry in place of DT circuitry. We noted last paragraph that DT  $\Delta\Sigma$ Ms already enjoy resolution and power advantages over other styles of ADC; perhaps CT  $\Delta\Sigma$ Ms could retain these advantages while operating at higher speeds? This question has been given increasing attention in the last few years as the need for high-resolution ADC at ever-higher speeds grows.

It is this same question that we address in this thesis. We shall see that the practice of building CT  $\Delta\Sigma$ Ms for high-speed conversion has proved more difficult than anticipated—they operate correctly, but they achieve lower resolution than their lower-speed counterparts. We study the reasons for this in the present work. Past work has identified some of the problems in specific architectures, but here we generalize these results to many architectures, explore the effect of some previously unidentified nonidealities, and explain as much as possible about what can be done to overcome their effects. Where feasible, we give simple formulas for prediction of performance limits. This thesis contains a moderate amount of emphasis on theory, but every effort is made to tie the theory to practice. This is made easier because we have an actual high-speed part to test.

### **1.2** Contributions

The introductory chapters of this thesis present summaries of the published literature in the following subjects:

- $\Delta \Sigma M$  performance measurement;

- a  $\Delta \Sigma M$  nonideality literature survey;

#### Chapter 1: Introduction

• a CT  $\Delta \Sigma$ M literature survey.

The first and third of these are not summarized elsewhere to the author's knowledge and so are useful overviews, while the second is discussed in [Nor97, Chap. 11] for DT modulators but extended here for CT modulators. Thereafter follows the original material listed here.

- 1. The phenomenon of "excess loop delay" in  $\Delta \Sigma Ms$  has been identified as an important nonideality in past work, though the study has been scattered among several papers. Here, we collect all the information into one place, use an improved mathematical technique, and apply it to previously-unstudied circuit architectures.

- 2. The effect of clocking a CT  $\Delta \Sigma M$  with an on-chip VCO having a certain phase noise specification is quantified for the first time.

- 3. A new method of system identification is proposed and illustrated for CT  $\Delta \Sigma Ms$ .

- 4. Quantizer metastability is identified as a mechanism of performance loss in CT  $\Delta\Sigma$ Ms and its effect characterized.

- 5. The tradeoffs and parameter selection criteria in the design of  $f_s/4$  fourth-order band pass modulators are outlined and an explicit design procedure formulated.

- 6. Simulation and measurement results are presented on a fabricated fourth-order band pass modulator with a 4GHz clock. As well, design improvements which appear to better the performance significantly are suggested.

There are also many illustrative examples throughout the following chapters that clarify the concepts presented.

### **1.3 Organization**

**Chapter 2** introduces the concept of delta-sigma modulation, lists some of the fundamental modulator design choices, explains how modulator performance is measured, and briefly discusses time-domain simulation of  $\Delta \Sigma Ms$ .

**Chapter 3** summarizes some issues surrounding the implementation of  $\Delta \Sigma Ms$ . We survey the literature that characterizes the effect of certain nonidealities in DT  $\Delta \Sigma Ms$  and explain how these apply to CT  $\Delta \Sigma Ms$ , then we list and briefly describe the important papers in CT  $\Delta \Sigma M$ . Finally, a summary of the performance achieved in published high-speed CT  $\Delta \Sigma Ms$  is given.

**Chapter 4** is about excess loop delay in CT  $\Delta \Sigma$ Ms, which is delay between the clock edge and the effect of the output bit as seen at the feedback. We first expound on the equivalence between ideal DT and CT modulators, then explain what loop delay does to this equivalence, illustrating the performance lost in different modulator orders and architectures. As well, we look at methods for overcoming this performance loss.

**Chapter 5** characterizes the effect of quantizer clock jitter on ideal CT  $\Delta \Sigma M$  performance and looks at the effect of clocking a CT  $\Delta \Sigma M$  with a practical integrated VCO with a given phase noise characteristic.

**Chapter 6** analyzes quantizer metastability and its effect on high-speed CT  $\Delta \Sigma$ Ms and proposes what can be done to alleviate the performance loss it causes.

**Chapter 7** presents design guidelines, analysis, simulation results, and test results for a fourthorder 4GHz band pass  $\Delta \Sigma M$  fabricated with SiGe HBTs for conversion of narrowband 1GHz analog signals to digital. We also redesign key portions of the modulator and estimate the performance improvement that would result.

**Chapter 8** concludes the thesis with a discussion of the appropriateness of CT  $\Delta \Sigma M$  for applications requiring high-speed ADC and makes recommendations for future work.

# Chapter 2

# $\Delta \Sigma \mathbf{M}$ Concepts

In this chapter we explain what a delta-sigma modulator is and how it can be used for analog-todigital conversion along with some of the basic design choices in  $\Delta \Sigma M$  design. We move on to how the performance of a  $\Delta \Sigma M$  is measured. Finally, we discuss some aspects of the time-domain simulation of  $\Delta \Sigma M$ s, distinguishing discrete-time modulator simulation from continuous-time.

# **2.1** A Brief Introduction to $\Delta \Sigma \mathbf{M}$

An overview of the  $\Delta\Sigma M$  concepts relevant for this work will be presented here. If it seems too cursory, the reader may turn to any of a number of excellent summary articles [Hau91, Can92b, Azi96, Can97] for a more detailed treatment.

# 2.1.1 Operating Principles

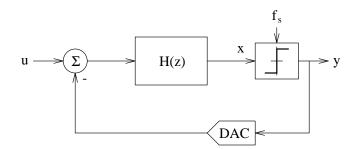

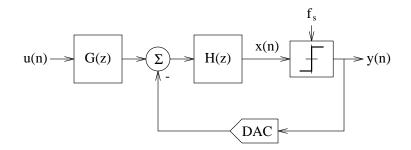

A  $\Delta \Sigma M$  ADC has three important components, depicted in Figure 2.1:

- 1. A loop filter or loop transfer function H(z)

- 2. A clocked quantizer

- 3. A feedback digital-to-analog converter (DAC)

Figure 2.1: Basic components of a  $\Delta \Sigma M$  for ADC.

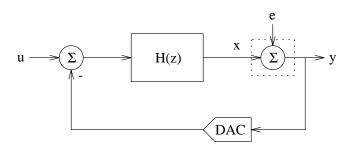

The quantizer is a strongly-nonlinear circuit in an otherwise linear system, which makes the behavior of  $\Delta\Sigma$ Ms very complicated to investigate analytically [Gra90]. The basic idea of  $\Delta\Sigma$  modulation is that the analog input signal is modulated into a digital word sequence with a spectrum that approximates that of the analog input well in a narrow frequency range and has the quantization noise "shaped" away from this range. An intuitive qualitative understanding of how this happens can be had by *linearizing* the circuit as shown in Figure 2.2. The quantizer is replaced by an adder

Figure 2.2: Linearizing the quantizer in a  $\Delta \Sigma M$ .

and we pretend that the quantization noise is "generated" by an input e which is independent of the circuit input u. The output y may now be written in terms of the two inputs u and e as

$$Y(z) = \frac{H(z)}{1 + H(z)}U(z) + \frac{1}{1 + H(z)}E(z)$$

(2.1)

$$= \operatorname{STF}(z) \cdot U(z) + \operatorname{NTF}(z) \cdot E(z)$$

(2.2)

where STF(z) and NTF(z) are the so-called *signal transfer function* and *noise transfer function*. From (2.1) we see that the poles of H(z) become the zeros of NTF(z), and that for any frequency

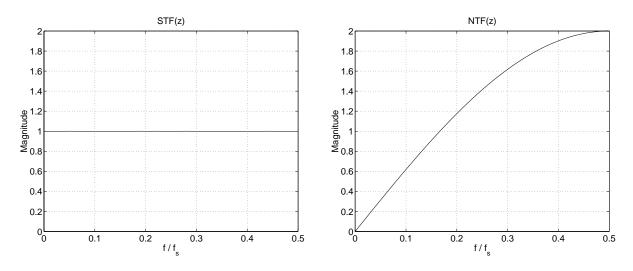

Figure 2.3: STF(z) and NTF(z) for circuit of Example 2.1.

where  $H(z) \gg 1$ ,

$$Y(z) \approx U(z)$$

In other words, the output resembles the input most closely at frequencies where the gain of H(z) is large.

**Example 2.1**: Consider the system of Figure 2.1 with a simple integrator H(z) = 1/(z-1) as the loop filter and a one-bit quantizer which produces output bits with values  $\pm 1$ . From (2.1) we can calculate

$$STF(z) = z^{-1}, NTF(z) = 1 - z^{-1}.$$

(2.3)

These are depicted graphically in Figure 2.3 with  $z = \exp(j2\pi fT_s)$ . We have  $H(z) \rightarrow \infty$  at dc (i.e., at f = 0), which means input signals near dc should be reproduced faithfully in the output bit stream. In fact, |STF(z)| = 1 everywhere, so we at least expect the *magnitude* of an input at any frequency to be reproduced at the output. As well,  $\text{NTF}(z) \rightarrow 0$  at dc, and it increases away from dc; hence, the quantization noise is "shaped away from dc".

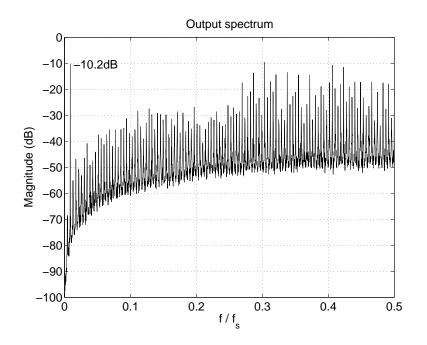

If we implement the system mathematically, simulate it in Matlab, and look at the power spectrum of the output bit stream, we obtain the plot shown in Figure 2.4. In

Figure 2.4: Simulated output bit stream power spectrum.

this example, the input tone had an amplitude of 0.434V and a frequency of  $(8.545 \times 10^{-3})f_s$ . Relative to the output levels of  $\pm 1$ , we expect, and observe, an output signal power of  $20 \log_{10}(0.434/\sqrt{2}) = -10.2$ dB. The quantization noise spectrum follows NTF(z) qualitatively at least, going to zero at dc and increasing away from dc, but it clearly contains tones spaced at an interval related to the input frequency. The usual assumption when linearizing the quantizer as in (2.1) is that the quantization noise spectrum is white, as well as uncorrelated with the input; while the former is often true, the latter is never exactly true though the correlation is often so complex as to be all but impossible to determine. The linearization is thus not really valid, but it often gives correct qualitative predictions of modulator performance. However, we usually require *quantitative* accuracy, and thus for the most part we eschew linearization throughout this thesis.

Note what is implied in this example: the quantization noise is reduced only in a small bandwidth, that is, a bandwidth much smaller than the sampling frequency  $f_s$ . If we wish to obtain high converter resolution, then the signal must be bandlimited to a value much smaller than  $f_s$ . This means that for a signal with Nyquist rate  $f_N$ , we require  $f_N \ll f_s$ , which is the same as saying we must sample much *faster* than the Nyquist rate.  $\Delta \Sigma Ms$ , therefore, are so-called *oversampled* converters, with an oversampling ratio defined as

$$OSR \equiv f_s / f_N. \tag{2.4}$$

How is the high-speed low-resolution quantizer output converted to multibit output samples at the Nyquist rate? A complete block diagram of a  $\Delta \Sigma M$  ADC is shown in Figure 2.5; it includes

Figure 2.5: Complete  $\Delta \Sigma M$  ADC block diagram including decimator.

a modulator followed by a circuit called a *decimator*. The decimator's purpose is twofold: it *decimates*, i.e., reduces in frequency, the high-rate bit stream *and* removes everything outside the desired band with a filter. Typical time domain and frequency domain waveforms at the modulator and decimator outputs are shown in the figure.

We do not go into detail regarding the design of the decimator, instead preferring to concentrate on designing a  $\Delta\Sigma M$  to obtain an output bit stream with desirable properties. Decimator design is reasonably well-understood and is covered in [Can92a]. As is customarily done in work about  $\Delta\Sigma M$ , we shall assume that the modulator output is filtered by a brick-wall filter with a gain of 1 in the signal band and 0 elsewhere.

# 2.1.2 Design Choices

There is a myriad of design choices for  $\Delta \Sigma Ms$ . Very briefly, the major ones are listed and described here.

#### Order of H(z) and oversampling ratio

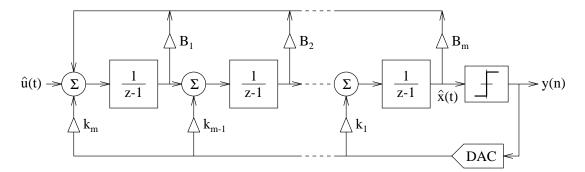

Example 2.1 featured a single integrator, a first-order transfer function, for H(z). In general, the order of H(z) (which must be strictly proper to ensure causality) is the maximum power of z in the denominator. It is possible to use a second-, third-, or even higher-order H(z) as a loop filter; generally, a converter of order m is built as a cascade of m integrators usually surrounded with feedforward and feedback coefficients [Cha90] as depicted in Figure 2.6.

Figure 2.6: General *m*th-order low pass  $\Delta \Sigma M$  structure.

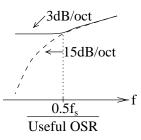

In a given application, the signal bandwidth  $f_N$  is usually fixed. Sampling faster than the Nyquist rate is *always* beneficial for improving the signal-to-noise ratio (SNR) in an ADC because the quantization noise inside the signal band is reduced by 3dB per octave of oversampling; in an order- $m \Delta \Sigma M$ , this improvement can be shown to be 6m + 3dB/oct [Can92b] because the noise is shaped by the loop filter. Thus, a high-order modulator is desirable because of the huge increase in converter dynamic range (DR) obtained from each doubling of the OSR.

Not surprisingly, using a high-order modulator has drawbacks. First, the stability of the overall system with H(z) above order two becomes conditional: input signals whose amplitudes are below but close to full scale (to be defined later) can cause overload at the output of the integrators closer to the quantizer, which degrades DR [Sch93]. As well, the placement of the poles and zeros of H(z) becomes a complicated problem, though many solutions have been proposed in the literature (e.g., [Ris94] among others). Furthermore, the technology in which the circuit is implemented and the circuit architecture itself will limit the maximum-achievable sampling rate and hence, from (2.4), the OSR. Finally, the design of the decimator increases in complexity and area for larger

oversampling ratios. Typical values of OSR lie in the range 32–256, though circuits with OSRs outside this range have been fabricated [Bai96, Nys96].

#### **Quantizer resolution**

It is possible to replace the single-bit quantizer of Example 2.1 with a multibit quantizer, e.g., a flash converter [Ada86]. This has two major benefits: it improves overall  $\Delta\Sigma M$  resolution and it tends to make higher-order modulators more stable. Furthermore, nonidealities in the quantizer (e.g., slightly misplaced levels or hysteresis) don't degrade performance much because the quantizer is preceded by several high-gain integrators, hence the input-referred error is small [Hau86]. Its two major drawbacks are the increase in complexity of a multibit vs. a one-bit quantizer, and that the feedback DAC nonidealities are directly input-referred so that a slight error in one DAC level corrupts converter performance greatly. There exist methods to compensate for multibit DAC level errors (e.g., [Gal96], [Lar88]). These aren't needed in a single-bit design because one-bit quantizers are inherently linear [Sch93].

#### Low pass vs. band pass

Integrators have poles at dc, and hence building H(z) from integrators will shape noise away from dc.  $\Delta\Sigma$ Ms where the quantization noise has a high pass shape are built with low pass loop filters and hence are denoted *low pass* (LP) converters. If we were to build H(z) out of *resonators*, the noise would tend to be shaped away from the resonant frequency. The quantization noise then has a band stop shape because the loop filter is band pass, and the resulting  $\Delta\Sigma$ Ms are called *band pass* (BP) converters [Sch91]. A common type of band pass converter is built starting with a low pass H(z) and performing the substitution  $z^{-1} \rightarrow -z^{-2}$ ; this produces a converter with noise shaped away from  $f_s/4$  with identical stability properties performance as the low pass prototype, though the order is doubled [Sho96].

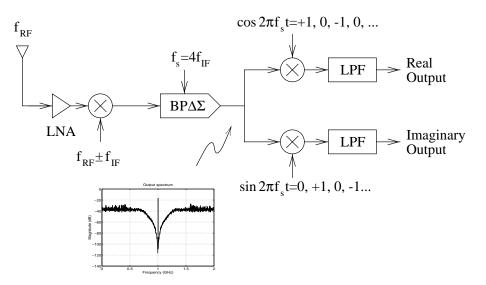

A typical application of such a converter is the conversion of an RF or IF signal to digital for processing and heterodyning in the digital domain, as depicted in Figure 2.7. The spectrum at the output of the converter is shown in the figure—the quantization noise is large everywhere except

Figure 2.7: Typical radio receiver application for a band pass  $\Delta \Sigma M$ .

in a narrow band near 1GHz. Mixing to baseband digitally for I and Q channel recovery becomes particularly easy when the sampling frequency is chosen to be four times the input signal frequency because sine and cosine are sequences involving only  $\pm 1$  and 0, so simple digital logic can replace a complicated multiplier circuit. In general, the ability of a  $\Delta \Sigma M$  to perform narrowband conversion at a frequency other than dc makes them particularly attractive for radio applications; furthermore, CT  $\Delta \Sigma Ms$  can be made fast enough to allow conversion of signals into the hundreds of MHz and beyond<sup>1</sup>.

OSR for BP converters is defined as half the sampling frequency divided by the bandwidth of interest [Nor97, Chap. 9]; thus, an  $f_s/4$  converter with a signal occupying the frequency range  $(f_s/4 - f_s/32, f_s/4 + f_s/32)$  has a bandwidth of  $f_s/16$ , and hence OSR = 8.

#### Discrete- vs. continuous-time

We have been writing the loop transfer function H(z) in the discrete-time (DT) domain. The majority of  $\Delta \Sigma Ms$  in the literature are implemented as discrete-time circuits such as switched-

<sup>&</sup>lt;sup>1</sup>This is not the only possible architecture: we might digitize directly at the RF rather than at the IF, although the noise figure of the  $\Delta \Sigma M$  might be too high to achieve the desired system dynamic range. We might also mix more than once prior to the modulator.

#### Chapter 2: $\Delta \Sigma M$ Concepts

capacitor (SC) [Bai96] or switched-current (SI) [Ned95] circuits. It is possible to build the loop filter as a *continuous-time* (CT) circuit  $\hat{H}(s)$ , for example with transconductors and integrators [Jen95]. It is this kind of circuit in which we are interested in this thesis for it will usually be possible to clock a CT  $\Delta\Sigma$ M at a much higher rate than an SC or SI design in the same technology.

## Single stage vs. multi-stage

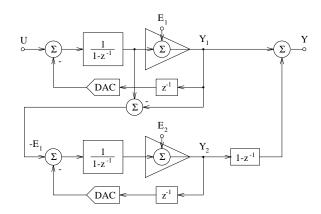

Many modulators employ a single quantizer with multiple feedback loops leading to various points inside the forward modulator path, and these are called *multiloop*  $\Delta\Sigma$ Ms. It is possible to build stable high-order modulators out of two or more low-order modulators where later modulators' inputs are the *quantization noise* from previous stages. Such  $\Delta\Sigma$ Ms are called *multistage*; they were originally dubbed "MASH" structures, where MASH is an acronym deriving somehow from Multistage Noise-Shaping [Hay86]. In Figure 2.8, a first-order modulator's quantization noise is

Figure 2.8: A multistage  $\Delta \Sigma M$ .

shaped by another first-order modulator:

$Y_1 = U + (1 - z^{-1})E_1$  $Y_2 = -E_1 + (1 - z^{-1})E_2.$

When  $Y_2$  is differentiated and added to  $Y_1$ , we find

$$Y = Y_1 + (1 - z^{-1})Y_2$$

$$= U + (1 - z^{-1})E_1 - (1 - z^{-1})E_1 + (1 - z^{-1})^2 E_2$$

= U + (1 - z^{-1})^2 E\_2. (2.5)

Thus, the first-order noise is canceled in the output and the modulator achieves second-order quantization noise shaping. In principle, this can be extended to *m*th order noise shaping while preserving unconditional stability since each first-order  $\Delta \Sigma M$  is unconditionally stable. In practice, mismatches between components in the stages result in imperfect noise cancellation [Mat87].

To the author's knowledge, all published MASH  $\Delta \Sigma$ Ms to date have been DT. It is possible to do CT MASH, but the only place it is discussed is [Nor97, Chap. 6]. As such, we will consider only single-stage modulators in this thesis.

# 2.2 **Performance Measures**

We have mentioned certain A/D converter performance measures such as dynamic range and signal-to-noise ratio, but we have yet to explain how to determine them for a  $\Delta \Sigma M$ . This section does just that by combining information from a literature survey about the subject with the author's practical experience.

## 2.2.1 **Power Spectrum Estimation**

A  $\Delta\Sigma M$  is a *noise-shaping converter*: the quantization noise is shaped away from the desired frequency band. We are thus interested in the frequency domain representation of the time domain output bits. More specifically, we care about the power spectrum of the output bits. The most common tool for finding power spectra is the discrete Fourier transform or DFT.

Suppose we have N uniformly-sampled data points  $y(n) = \hat{y}(t)|_{t=nT_s}$ ,  $n = 0 \dots N - 1$ ,  $y(n) \in \mathbf{R}$ . We will be using the so-called *periodogram* to estimate the power spectrum of y(n). The DFT (which can be a *fast Fourier transform* or FFT when N is a power of two, which it frequently is) of y(n) is given by

$$Y(n) = \sum_{k=0}^{N-1} y(k) e^{j2\pi kn/N}, \ n = 0 \dots N - 1$$

(2.6)

and the periodogram is defined as [Pre92]

$$P(0) = \frac{1}{N^2} |Y(0)|^2$$

$$P(n) = \frac{1}{N^2} [|Y(n)|^2 + |Y(N-n)|^2], n = 1 \dots (\frac{N}{2} - 1)$$

$$P(N/2) = \frac{1}{N^2} |Y(N/2)|^2.$$

(2.7)

This power spectrum is defined at N/2 + 1 uniformly-spaced frequency points between 0 and the Nyquist rate  $f_s/2$ . Thus, each frequency *bin* is of width  $f_s/N$ . An example plot of  $10 \log_{10} P$  from (2.7) was shown in Figure 2.4 in Example 2.1. Evidently, *P* is rms power: our input had magnitude -7.2dB and its power in the spectrum is -10.2dB. In this thesis, when we refer to the "spectrum", we mean the power spectrum as found from the periodogram.

A periodogram is a discrete representation of the spectrum of a discrete (sampled) signal, but in the real world power spectra are continuous functions of continuous signals. The discretization gives rise to two problems in periodograms, the first of which is usually denoted *spectral leakage* or simply *leakage*, and the second of which relates to uncertainty. We discuss both and how to alleviate them below.

## Leakage and windowing

If there exists a tone in the input signal at a frequency that does not fall exactly in the center of a frequency bin, then leakage will result: instead of a sharp "spike" in one sepctrum bin, the tone will become spread over several adjacent bins. This can be understood by realizing that we can only take the FFT of a finite stretch of data (i.e., at a finite number of points); this is akin to taking the FFT of an infinite stretch of data multiplied by a rectangular window that is 1 for the duration of the finite stretch and 0 elsewhere. In the frequency domain, this corresponds to convolving an infinite power spectrum with the Fourier transform of a rectangle, namely,  $(\sin x)/x$ . The amount of leakage is determined by the spectrum of this function.

The severity of leakage may be reduced by *windowing* the data, which means multiplying it by a *windowing function* before taking its FFT. This has the effect of convolving the spectrum with a function other than  $(\sin x)/x$ . [Har78] lists many examples of windows; in the time domain, they

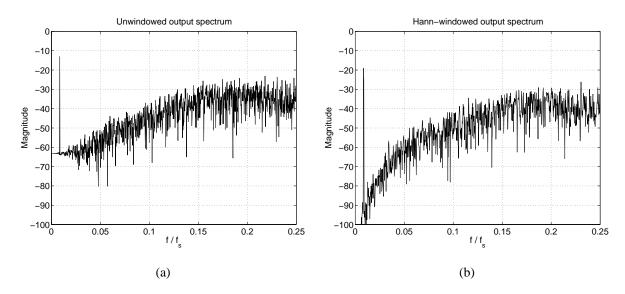

Figure 2.9: Effect of windowing: (a) unwindowed output spectrum, (b) windowed output spectrum.

generally peak at 1 near the center of the data and fall to 0 in various ways near the edges. We prefer to use a *Hann window* (often incorrectly called a *Hanning window*), also called a *raised cosine* window because of the formula that describes it:

$$w(n) = \frac{1}{2} \left[ 1 - \cos\left(\frac{2\pi n}{N}\right) \right], n = 0, \dots, N - 1.$$

(2.8)

**Example 2.2**: In the simulation of  $\Delta \Sigma Ms$ , it is easy (and recommended) to choose an input sinusoid with a frequency exactly in the center of a bin by making its frequency a multiple of  $f_s/N$ . Thus, leakage from the input tone is not usually problematic. Moreover, discrete tones arising from output limit cycles also usually fall exactly in the center of frequency bins. One case where they don't occurs when simulating a low pass  $\Delta \Sigma M$  and the mean of y(n) is nonzero. This creates a dc component in P(n) and also "misaligns" the output limit cycles such that there is leakage into all the low-frequency bins. We shall see that this turns out to give an unfairly-pessimistic SNR estimate.

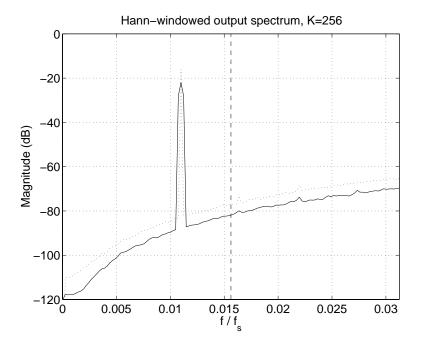

Windowing greatly alleviates the problem. Figure 2.9(a) illustrates what happens when N = 4096 output bits from a second-order modulator have an average value of 2/N = -66.2dB: the spectrum near dc flattens out to -63.2dB. Taking that same output bit stream and first multiplying it by a Hann window before taking the FFT yields Figure 2.9(b): now, the noise-shaping behavior is clearly evident down to dc. The author prefers a Hann window because the input tone only becomes smeared over its immediately adjacent bin on each side; compare this to Blackman or Welch windows, commonly used by other authors, which smear the tone over several adjacent bins. This is of concern for calculating SNR as we shall see in Example 2.4.

## Uncertainty and averaging

The second reason why periodograms are inaccurate is as follows: the periodogram at a single frequency P(n) is an estimate of a continuous function  $\hat{P}(f)$  over a frequency range  $f_s/N$  centered at  $f_n$ . It turns out the estimate P(n) has a standard deviation of 100% of the "actual" value. However, by taking K successive sets of N output bits, finding the periodogram of each, and *averaging* them, the standard deviation in each frequency bin is reduced by  $\sqrt{K}$  [Pre92].

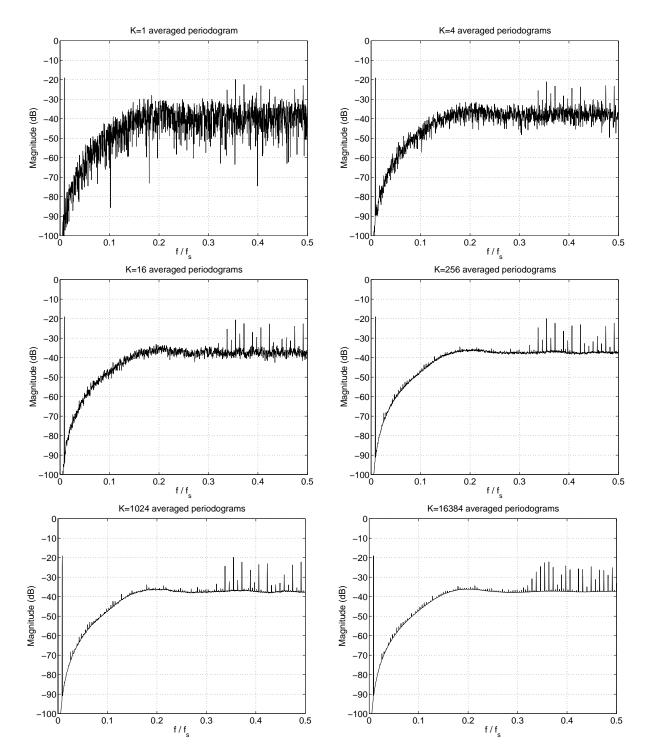

**Example 2.3**: Figure 2.10 is a striking illustration of the effect of averaging on the output power spectrum of a second-order  $\Delta \Sigma M$ . The upper-left graph shows the FFT of N = 4096 output bits; the upper-right graph depicts the average of K = 4 successive sets of N output bits. The following graphs are for  $K = \{16, 256, 1024, 16384\}$ ; the graphs become smoother and smoother as the variance in each frequency bin is reduced. Moreover, the detail of the tones near  $f_s/2$  is enhanced.

To generate the graph for K = 16384 we must calculate  $N \times K \approx 67 \times 10^6$  output bits, and that takes about 12 minutes with a C program on an unloaded 170MHz Sparc Ultra. We do not usually need that large a K; it was provided merely as an illustration. 256 would certainly suffice for most purposes.

# 2.2.2 Signal to Noise Ratio (SNR)

One of the most important performance measures of a  $\Delta \Sigma M$  is its signal-to-noise ratio (SNR). From this we may calculate other important performance measures such as its dynamic range

Figure 2.10: Effect of averaging on spectrum variance.

Figure 2.11: Unwindowed averaged periodogram near dc.

(DR) and peak SNR (SNR<sub>max</sub>).

To find the SNR in a Nyquist-rate converter, we would divide the signal amplitude by the integrated noise from 0 to  $f_N/2$  [Kes90a], which is the same frequency as  $f_s/2$ . A  $\Delta\Sigma M$  is an oversampled converter, however, so we do the same calculation over the bandwidth from 0 to  $f_N/2$ , which is now  $f_s/(2 \cdot OSR)$ . As noted earlier, this assumption is the same as having the modulator followed by a brick-wall low pass filter which cuts off sharply at  $f_N/2$ . That being said, we are about to see that there remain a number of subtleties in this calculation.

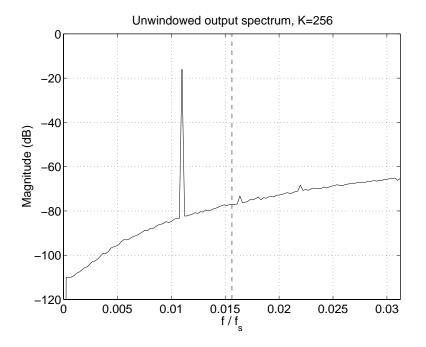

**Example 2.4**: Consider a 4096-point simulation of a second-order modulator. With K = 256 averaged periodograms, the spectrum near dc appears as in Figure 2.11. The input tone is -13dB and it occurs in bin b = 45, which is  $0.01099 f_s$ . Let us try to calculate the SNR for OSR = 32.

We must integrate the noise between 0 and  $f_s/64$ , which is shown by the dashed line in Figure 2.11. This corresponds to bin numbers 0 through 4096/64 = 64. Pre-

sumably, the noise power we're interested in can be found from

$$P_n = \sum_{i=0}^{64} P(i) - P(b).$$

(2.9)

However, do we include bin 64 in the calculation, or exclude it? In other words, should we find the noise for  $0 \le f \le f_s/64$ , or  $0 \le f < f_s/64$ ? Moreover, what should we do about the bin containing the signal? Do we subtract it as in (2.9) and leave it at that, or perhaps add the geometric mean of the power in the surrounding bins to  $P_n$  to make up for the missing bin?

Table 2.1 addresses some of these considerations, as well as the effect of K (the