### 8.2 A Fully Integrated Digital Hearing-Aid Chip with Human-Factors Considerations

### Sunyoung Kim, Seung Jin Lee, Namjun Cho, Seong-Jun Song, Hoi-Jun Yoo

KAIST, Daejeon, Korea

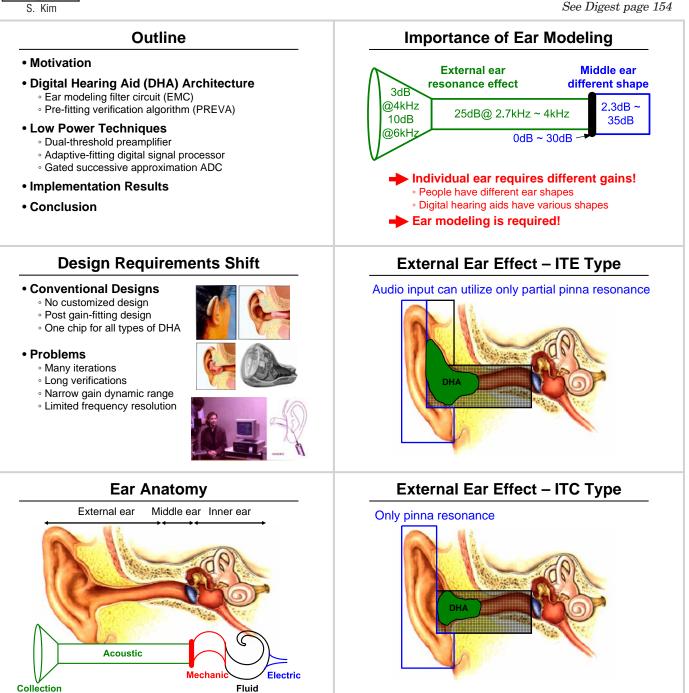

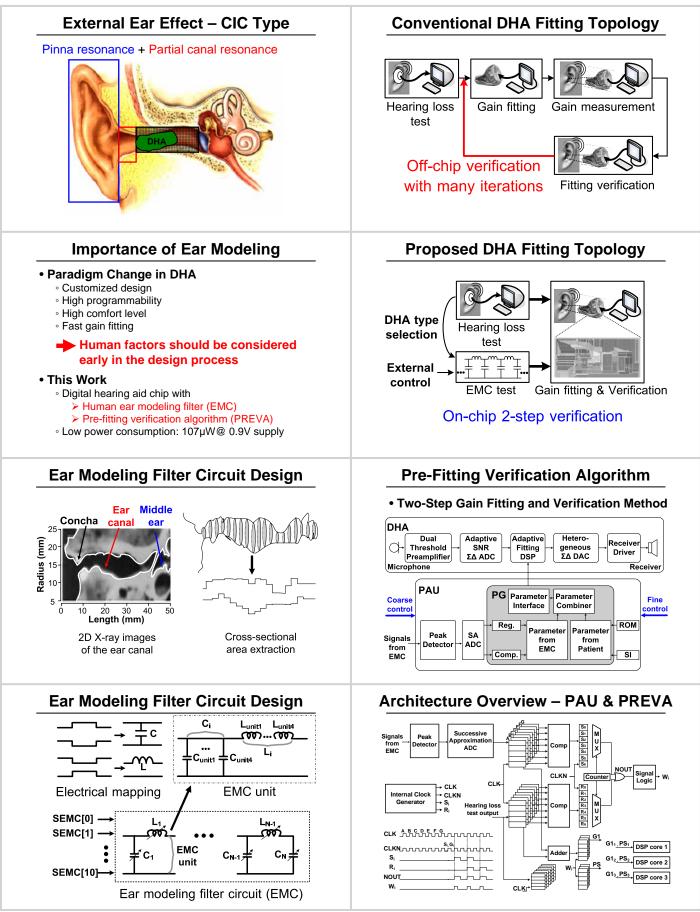

A digital hearing-aid chip integrates a pre-fitting verification algorithm to obtain gain fitting in two steps: coarse and fine. The internal ear canal modeling filter circuit enables the coarse fitting based on the shape of the external ear. Fine fitting verification is performed with external inputs. The 3.74mm<sup>2</sup> chip draws less than 120µA from a single 0.9V supply in a 0.18µm CMOS technology.

Continued on Page 549

8

Continued from page 111

## Performance Summary

104 1 10 1

High Input Compressio

101

Low Input

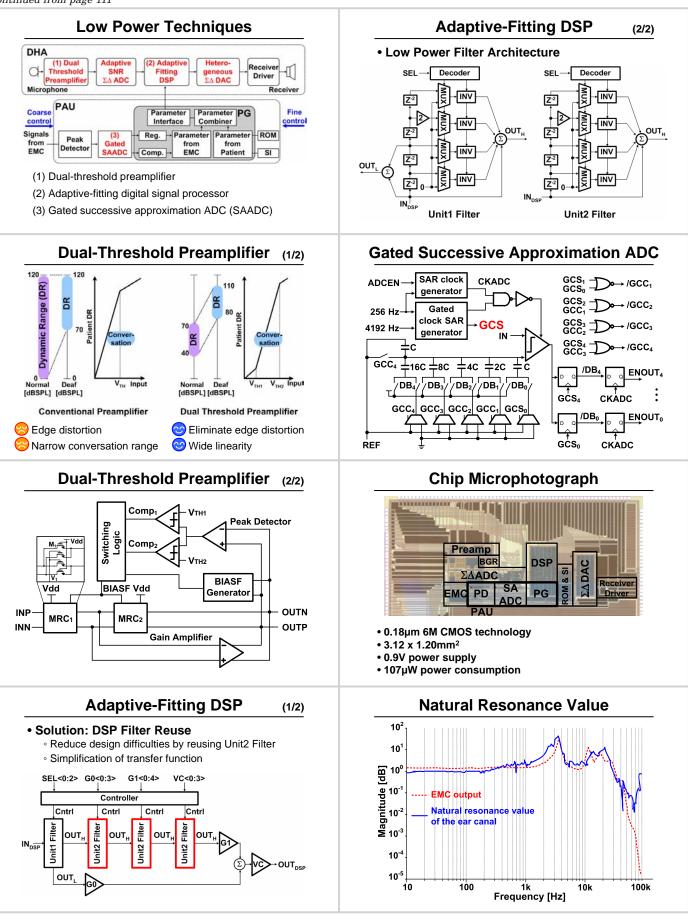

| Supply voltage                     |                          |            |    |    |                         | 0.9V                         |                 |       |

|------------------------------------|--------------------------|------------|----|----|-------------------------|------------------------------|-----------------|-------|

| Peak SNR (Overall Voltage)         |                          |            |    |    |                         | 81dB                         |                 |       |

| Power dissipation                  |                          |            |    |    |                         | 70μW(analog) / 37μW(Digital) |                 |       |

| -3dB bandwidth                     |                          |            |    |    |                         | 8kHz                         |                 |       |

| Input referred noise               |                          |            |    |    | 4.2µVrms                |                              |                 |       |

| Human factor considered techniques |                          |            |    |    | EMC / PREVA             |                              |                 |       |

| Core area / CMOS process           |                          |            |    |    | 3.12 x 1.20 mm²/ 0.18µm |                              |                 |       |

| Pre                                | Max. gain                |            | 38 | dB |                         | DSP                          | Gate count      | 43K   |

| amp                                | DB <sub>TH</sub>         | 0.45V~0.8V |    | &  | Clock freq.             | 32kHz                        |                 |       |

| ΣΔ                                 | Туре                     | 1          | 2  | 3  | 4                       | PG                           | Channel         | 8/3   |

| ADC                                | SNR <sub>PEAK</sub> (dB) | 75         | 85 | 77 | 89                      |                              | Sampling rate   | 256   |

| ΣΔ                                 | Gate count               | 16K        |    |    |                         | SA                           | On current      | 0.8µA |

| DAC                                | Input freq.              | 512kHz     |    |    |                         | ADC                          | Standby current | 55pA  |

|                                    | Clock freq.              | 2.048MHz   |    |    |                         |                              | ENOB (2kHz)     | 5.7   |

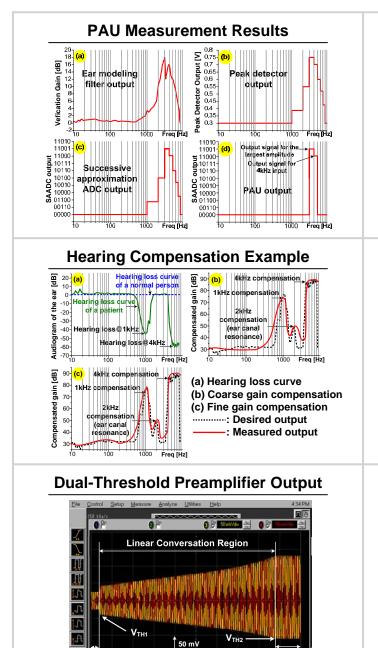

# **Comparison of DHA Chip**

|                                                | JSSC 1997<br>Neuteboom, et.al. | JSSC 2004<br>Serra-Graells, et.al. | This work           |

|------------------------------------------------|--------------------------------|------------------------------------|---------------------|

| Supply voltage                                 | 1.3V                           | 1V                                 | 0.9V                |

| Peak SNR                                       | 77dBA                          | 70dB                               | 81dB                |

| Power<br>consumption                           | 2mW                            | 200µW                              | 107µW               |

| Туре                                           | Digital                        | Programming                        | Digital             |

| Design techniques<br>based on<br>human factors | No                             | No                                 | Yes<br>(EMC, PREVA) |

| # of DSP band                                  | 4                              | -                                  | 8                   |

| CMOS technology                                | Low V <sub>тн</sub> 0.8µm      | 1.2µm                              | 0.18µm              |

# Conclusion

#### • A Digital Hearing-Aid Chip with Human-Factors Considerations

## Ear modeling filter circuit (EMC)

- Pre-fitting verification algorithm (PREVA)

- Low Power Techniques Utilized

- Dual-threshold preamplifier

- Adaptive-fitting digital signal processor

Gated successive approximation ADC

- Overall Power Consumption • 107µW@ 0.9V supply